# ADVANCED MULTI-CHEMISTRY AND MULTI-CELL SYNCHRONOUS SWITCH-MODE CHARGER AND SYSTEM POWER SELECTOR

# **FEATURES**

- High Efficiency NMOS-NMOS Synchronous Buck Converter With User-Selectable 300 kHz or 500 kHz frequency

- bq24721C Offers Softer Turn-On, Stronger Turn-Off

- SBS-Like<sup>(1)</sup> SMBus Interface for Control and Status Communications With Host

- Programmable Battery Voltage, Charge Current, and AC Adapter Current via SBS-Like SMBus Interface

- 0.4% Charge Voltage Regulation Accuracy

- 3% Charge Current Regulation Accuracy

- 3% Adapter Current Regulation Accuracy Dynamic Power Management (DPM)

- 2% Accuracy Integrated Charge and AC Adapter 20× Current Amplifier Output

- 3-Cell and 4-Cell Li-Ion Voltage Regulation

9 V, 12 V–14.4 V, 16 V–19.2 V

- Battery Pack Voltage Operating Range

0 V–19.2 V

- AC Adapter Operating Range 8 V–28 V

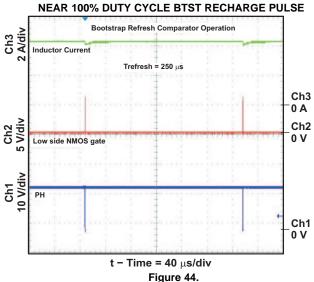

- 99.5% Max Duty Cycle

- Internal Soft Start

- Integrated 5% 5-V LDO When AC Adapter Applied

- 6-V Drive Supply Voltage for Increased Efficiency

- Reverse Battery to Adapter Discharge

Protection

- Battery/Adapter to System Power Selector Function

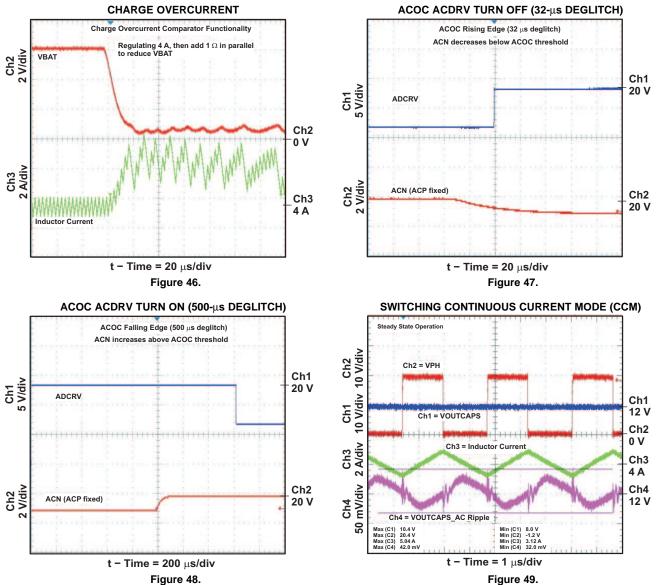

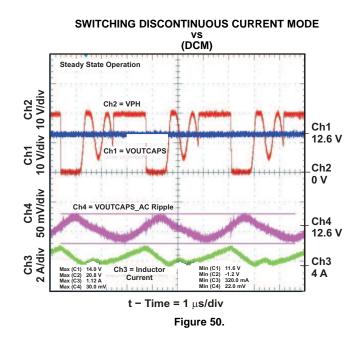

- Charge and Adapter Overcurrent Protection

- Battery Thermistor Sense, TS, Comparators

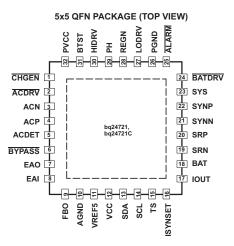

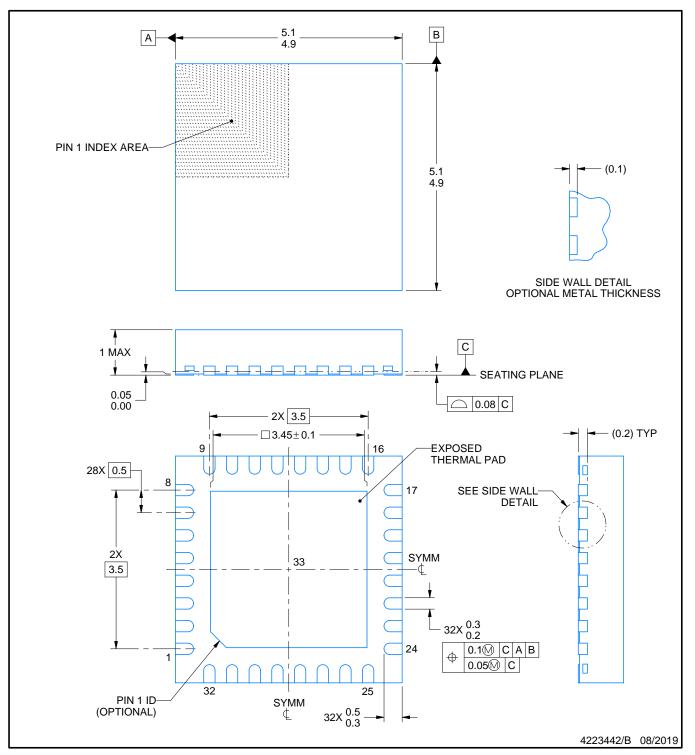

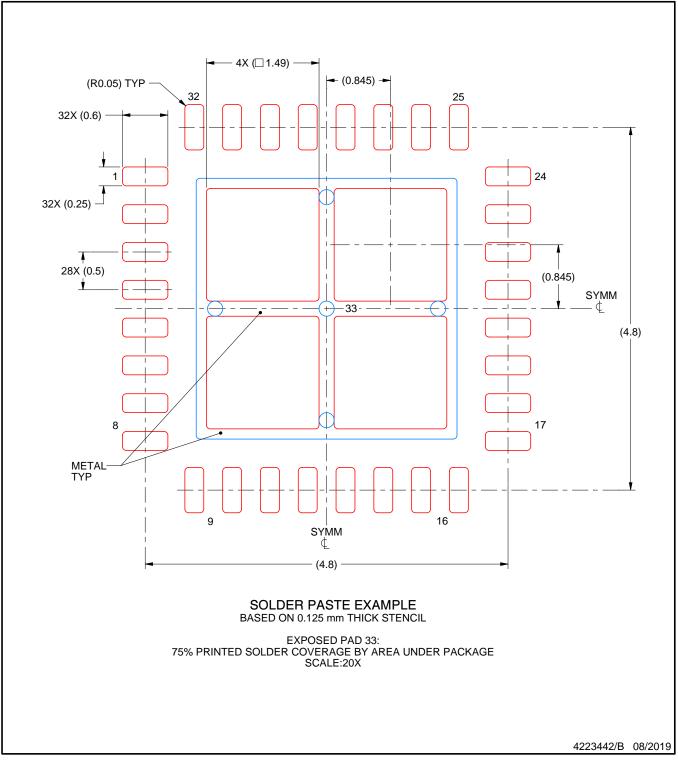

- Available in 32-Pin 5x5-mm QFN Package

(1) SBS-Like interface is not 100% SBS compliant. SBS-Like interface is SMBus1.1 complaint but does not support Packet Error Correction (PEC). The control and status registers were changed to simplify and enhance notebook charger control. An 8-bit address (0x12) is used. See Table 1 for a comparison between SBS-like vs SBS Specification.

# APPLICATIONS

- Portable Notebook Computers

- Portable DVD Players

- Webpads, PC Tablets

# DESCRIPTION

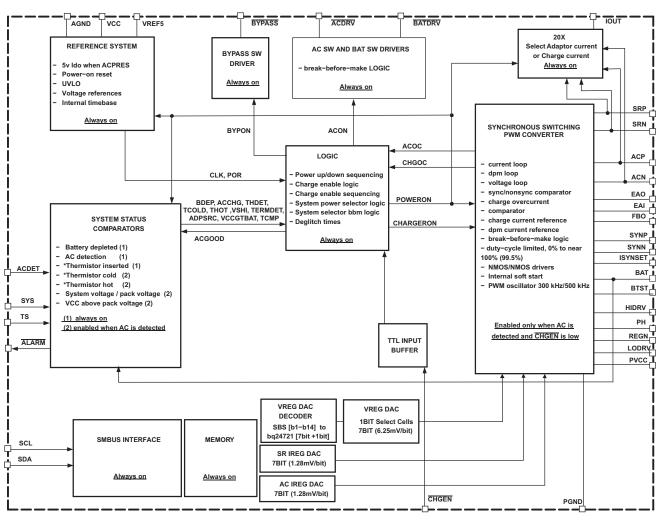

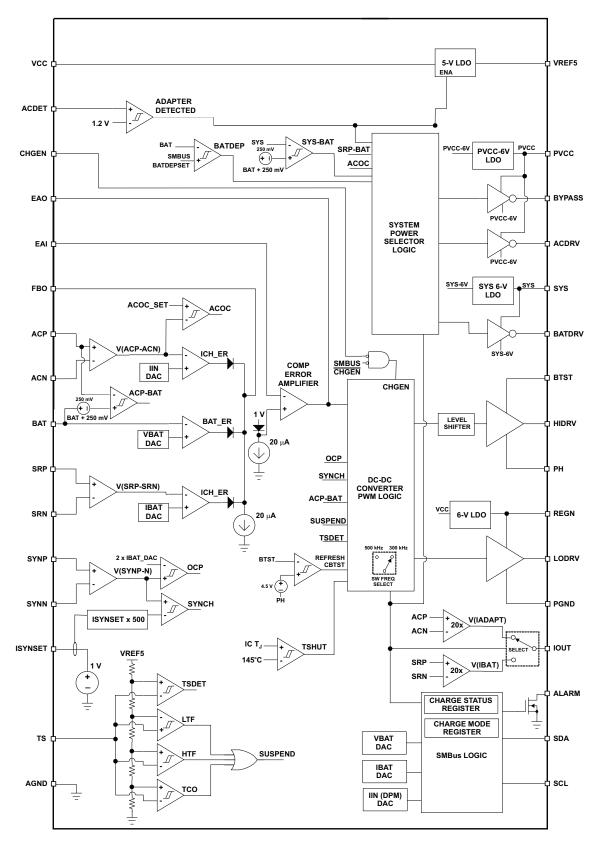

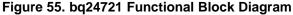

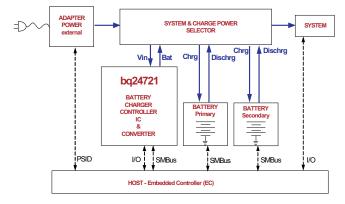

The bq24721 is a high efficiency synchronous battery pack charger with high level of integration for portable applications. This device implements a high performance analog front-end that interfaces to the system power management micro-controller through a simplified SBS-like SMBus interface.

The dynamic power management (DPM) function modifies the charge current depending on system load conditions, avoiding ac adapter overload.

High accuracy current sense amplifiers enable accurate measurement of either the charge current or the ac adapter current, allowing termination of nonsmart packs and monitoring of overall system power.

The adapter isolation diode can be bypassed or entirely replaced with an external MOSFET using a control signal provided by the bq24721, thus reducing overall power dissipation.

Integrated features such as charger soft start, charge overcurrent protection, and IC temperature monitoring provide a second level of protection, in addition to pack and system protection functions.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

# bq24721 bq24721C SLUS683F-NOVEMBER 2005-REVISED APRIL 2009

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

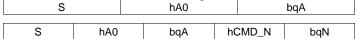

#### **ORDERING INFORMATION**

| PART NO. | PACKAGE   | THERMISTOR<br>SENSE | BATTERY SHORTED<br>(VERY LOW BATTERY<br>VOLTAGE) OPERATION | ORDERING NUMBER<br>(TAPE AND REEL) | QUANTITY |

|----------|-----------|---------------------|------------------------------------------------------------|------------------------------------|----------|

| ha04704  | 32 PIN    | те                  | Charge Current Changes to                                  | bq24721RHBR                        | 3000     |

| bq24721  | 5x5mm QFN | TS                  | C/8                                                        | bq24721RHBT                        | 250      |

| ha247240 | 32 PIN    | те                  | Charge Current Changes to                                  | bq24721CRHBR                       | 3000     |

| bq24721C | 5x5mm QFN | TS                  | C/8                                                        | bq24721CRHBT                       | 250      |

### PACKAGE THERMAL DATA

| PACKAGE <sup>(1)</sup> | $\theta_{JA}$ | T <sub>A</sub> ≤ 40°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C |

|------------------------|---------------|---------------------------------------|------------------------------------------------|

| RHB <sup>(2)</sup>     | 36°C/W        | 2.36 W                                | 0.028 W/°C                                     |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

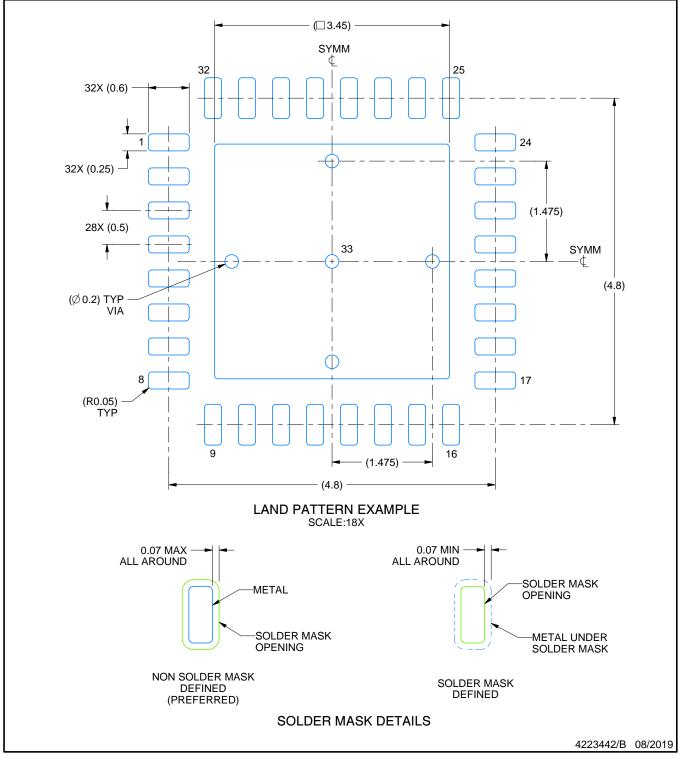

(2) This data is based on using the JEDEC High-K board and the exposed die pad is connected to a copper pad on the board. This is connected to the ground plane by a 2x3 via matrix.

# **DEVICE INFORMATION**

#### **TERMINAL FUNCTIONS**

| TE  | ERMINAL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO. | NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 1   | CHGEN   | <u>Charge</u> enable logic level low input. Logic HI on the <u>CHGEN</u> pin disables the charger. Logic LO on the <u>CHGEN</u> pin enables the charger. When the SMBus control register = bit0, CHGEN is also LO.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

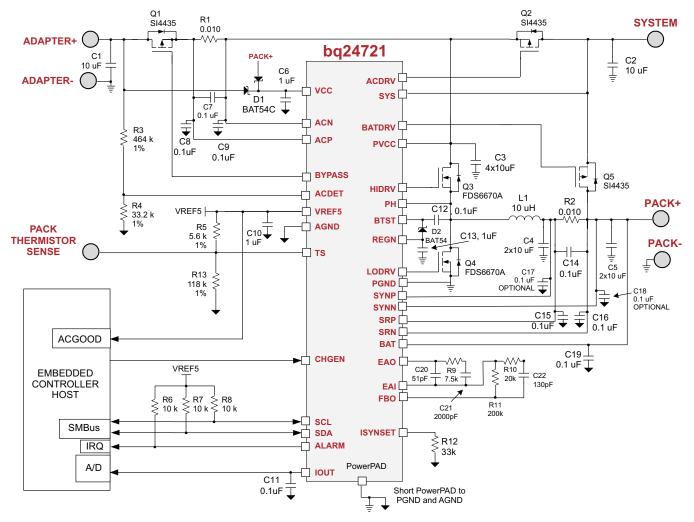

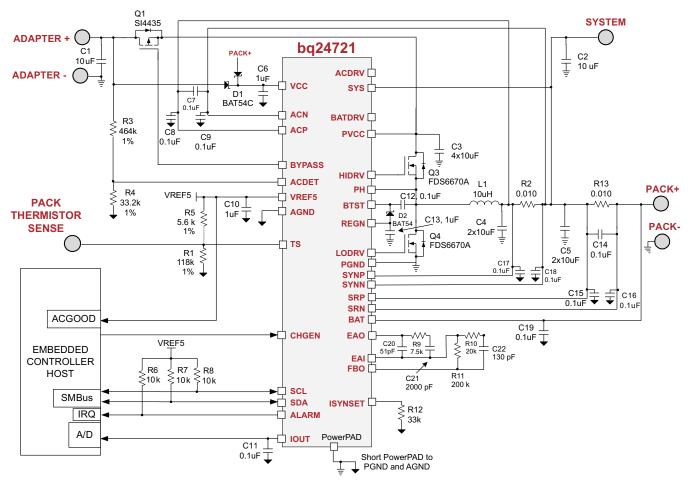

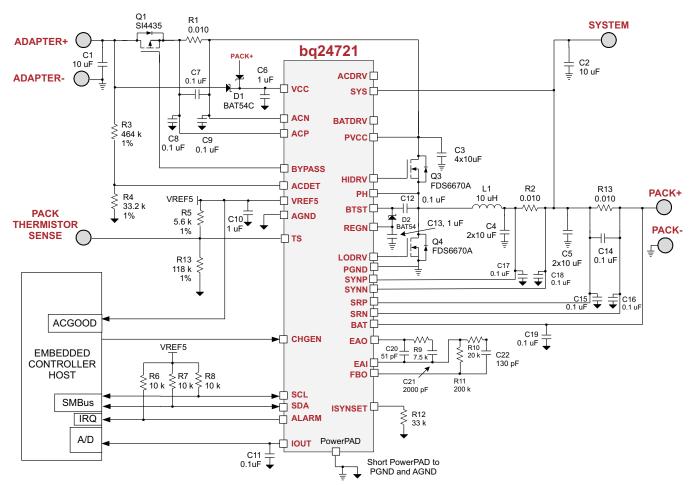

| 2   | ACDRV   | AC adapter to system switch driver output. Connect directly to the gate of the ACFET PMOS power FET. Connect the FET source to the PVCC node and negative side of the input current-sense resistor. Connect the FET drain to the system load side. Recommend placing a 100-k $\Omega$ resistor from the gate to the source of the Bypass FET. If needed, an optional capacitor from gate to source of the ACFET is used to help slow down the ON and OFF times. The internal gate drive is asymmetrical allowing a quick turn-off and slower turn-off in addition to the internal break-before-make logic with respect to the BATDRV. |  |  |  |  |

| 3   | ACN     | Adapter current sense resistor, negative input. An optional $0.1-\mu$ F ceramic capacitor is placed from this pin to AGND for common-mode filtering. An optional $0.1-\mu$ F ceramic capacitor is placed from ACN to ACP to provide differential-mode filtering.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 4   | ACP     | Adapter current sense resistor, positive input. Place this on the adapter side of the input current sense resistor. Recommend placing a 0.1-µF ceramic capacitor from ACP to AGND to provide common-mode filtering.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

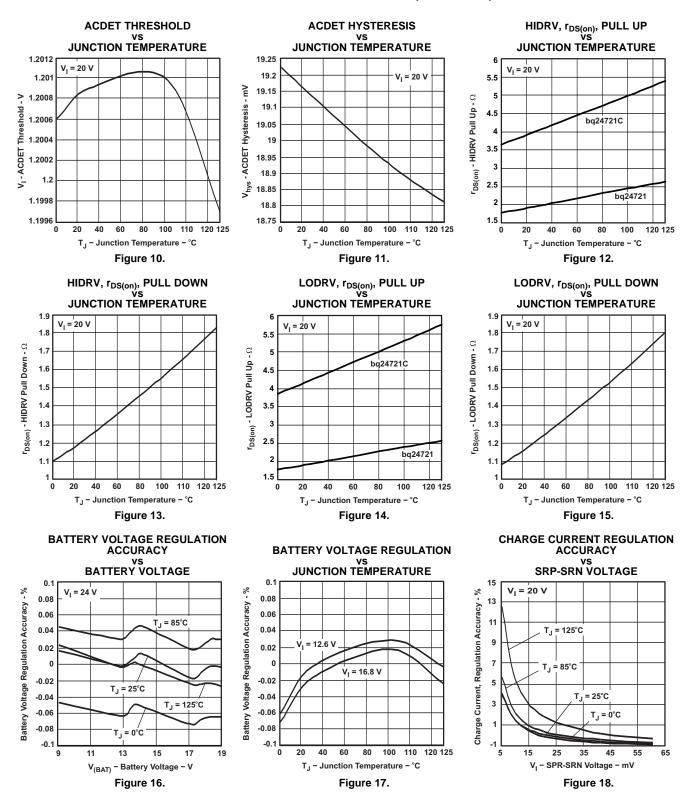

| 5   | ACDET   | AC adapter detected sense voltage input. Connect a voltage divider resistor from adapter input (before Bypass FET) to ACDET, and another resistor from ACDET to AGND, in order to program adapter detect threshold of 1.2 V. ACDET threshold should be greater than maximum battery regulation voltage, and lower than the minimum adapter voltage.                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 6   | BYPASS  | Gate drive for the adapter input BYPASS switch to prevent reverse discharge from the battery to the input. Connect this pin directly to the gate of the input bypass PMOS power FET. The source of the FET is connected to the adapter input voltage node. Recommend placing a $10-k\Omega$ resistor from the gate to the source of the BYPASS FET. The drain of the FET is connected to the positive node of the input current-sense resistor. An optional capacitor can be placed from the gate to the source to slow-down the switching times. Adjusting the turn-on and turn-off times is typically not needed for this FET.      |  |  |  |  |

| 7   | EAO     | Error amplifier output for compensation. Connect the feedback compensation components from EAO to EAI. Typically a capacitor in parallel with a series resistor and capacitor. See the compensation calculation procedures. This node is internally compared to the PWM saw-tooth oscillator.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

# **TERMINAL FUNCTIONS (continued)**

| TERMINAL |         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO.      | NAME    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 8        | EAI     | Error amplifier input for compensation, also connect the feedback compensation components from EA to EAO. Connect the input compensation components from FBO to EAI. See the compensation calculation procedures.                                                                                                                                                                                                                                                                                                |  |  |  |

| 9        | FBO     | Feedback output for compensation. Connect the input compensation components from FBO to EAI.<br>Typically, a resistor in parallel with a series resistor and capacitor. See the compensation calculation procedures.                                                                                                                                                                                                                                                                                             |  |  |  |

| 10       | AGND    | Analog ground. Ground connection for low current sensitive analog and digital signals. Only connect the PGND node by connecting to the PowerPAD <sup>™</sup> underneath the IC.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 11       | VREF5   | 5-V regulated voltage output, used for internal bias and the reference for programming the TS thermistor sense network. Used to indicate adapter present status. It is enabled by ac detected. Connect a 1- $\mu$ F ceramic capacitor from VREF5 pin to AGND as close to IC as possible.                                                                                                                                                                                                                         |  |  |  |

| 12       | VCC     | IC analog positive supply. Connect to adapter input, or diode, or by putting a diode from adapter inpu<br>and a diode from battery pack to VCC. Put a 1-µF ceramic capacitor from VCC to AGND, as close to<br>the IC as possible.                                                                                                                                                                                                                                                                                |  |  |  |

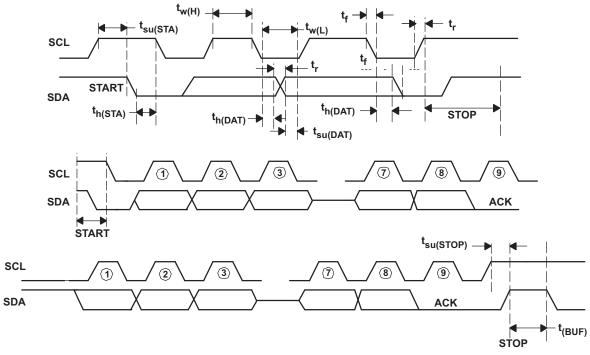

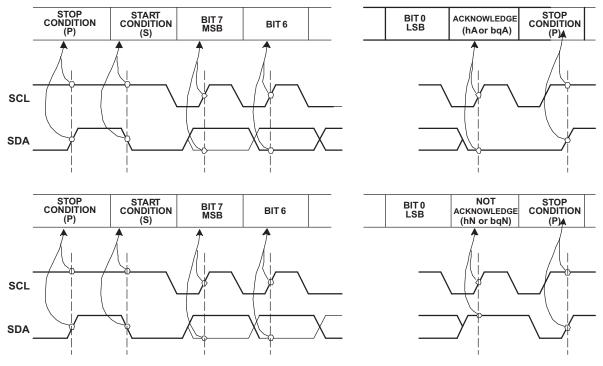

| 13       | SDA     | SMBus Data input. Connect to SMBus data line from the host controller. A 10-kΩ pullup resistor to th host controller supply rail is needed.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 14       | SCL     | SMBus Clock input. Connect to SMBus clock line from the host controller. A $10-k\Omega$ pullup resistor to the host controller supply rail is needed.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 15       | TS      | Thermistor sense input. Use a voltage divider from VREF5 to TS and AGND. Place a resistor from VREF to TS, and a resistor from TS to AGND to program the hot and cold battery pack thermistor temperatures. Charge is disabled when outside the hot/cold window. The TS pin is also used to deter if a battery is connected.                                                                                                                                                                                     |  |  |  |

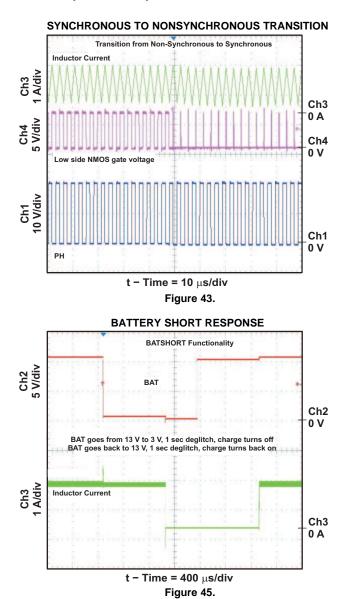

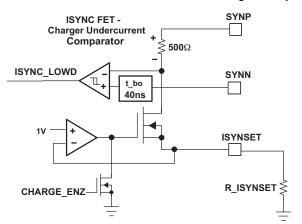

| 16       | ISYNSET | Program current threshold for synchronous to nonsynchronous regulation transition. Place a resistor from ISYNSET to AGND to program the charge undercurrent threshold to force nonsynchronous converter operation at low output current and prevent negative inductor current. Threshold should be set from inductor current ripple to full value of inductor current ripple.                                                                                                                                    |  |  |  |

| 17       | IOUT    | Battery charger or adapter current amplifier output. Current sense amplifier that outputs a voltage 20:<br>the current sense resistor differential voltage. The output can be selected by SMBus charge control<br>register (0x12) bit3 to be the input adapter current (ACP-ACN), or the battery charge current<br>(SRP-SRN). Place a 0.1-μF capacitor from IOUT to AGND for filtering the output ripple. Optionally, as<br>an RC filter after the output filter for further filtering.                          |  |  |  |

| 18       | BAT     | Battery voltage remote sense. Directly connect a kelvin sense trace from the battery pack positive terminal to the BAT pin to accurately sense the battery pack voltage. Place a $0.1-\mu$ F capacitor from BAT to AGND close to the IC to filter high frequency noise.                                                                                                                                                                                                                                          |  |  |  |

| 19       | SRN     | Charge current sense resistor, negative input. Connect to the charge current sense resistor negative terminal. Optionally, add a $0.1$ - $\mu$ F ceramic capacitor from SRN to AGND near the IC for common-mo filter.                                                                                                                                                                                                                                                                                            |  |  |  |

| 20       | SRP     | Charge current sense resistor, positive input. Connect to the charge current sense resistor positive terminal. Recommend placing a $0.1-\mu$ F ceramic capacitor from SRP to AGND near the IC for common-mode filter. Optionally, place a $0.1-\mu$ F ceramic capacitor from SRP to SRN near the IC for differential-mode filter.                                                                                                                                                                                |  |  |  |

| 21       | SYNN    | Charge overcurrent and charge undercurrent negative sense input. Connect to the charge current sense resistor negative terminal. If sensing the same sense resistor as SRN, the user can connect directly to the SRN pin and no further filter capacitors are needed. To sense a different sense resistor add a $0.1$ - $\mu$ F ceramic capacitor from SYNN to AGND near the IC for common-mode filter.                                                                                                          |  |  |  |

| 22       | SYNP    | Charge overcurrent and charge undercurrent negative sense input. Connect to the charge current sense resistor positive terminal. If sensing the same sense resistor as SRP, the user can connect directly to the SRP pin, and no further filter capacitors are needed. To sense a different sense resistor add a $0.1$ - $\mu$ F ceramic capacitor from SYNP to AGND near the IC for common-mode filter, and place $0.1$ - $\mu$ F ceramic capacitor from SYNP to SYNN near the IC for differential-mode filter. |  |  |  |

| 23       | SYS     | System load, voltage sense. Connect directly to the system load node and the source of the BAT PMOS power FET.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

bq24721 bq24721C SLUS683F-NOVEMBER 2005-REVISED APRIL 2009

www.ti.com

# **TERMINAL FUNCTIONS (continued)**

| TE  | RMINAL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 24  | BATDRV | Battery to system switch driver output. Gate drive for the battery to system load BAT PMOS power FET to isolate the system from the battery to prevent current flow from the system to the battery, while allowing a low impedance path from battery to system while discharging the battery pack to the system load. Connect this pin directly to the gate of the input BAT PMOS power FET. Connect the source of the FET to the system load voltage node. Connect the drain of the FET to the battery pack positive node. Recommend placing a 100-k $\Omega$ resistor from the gate to the source of the BAT FET. An optional capacitor is placed from the gate to the source to slow-down the switching times. The internal gate drive is asymmetrical allowing a quick turn-off and slower turn-off in addition to the internal break-before-make logic with respect to the ACDRV. |  |  |  |

| 25  | ALARM  | Alarm indicating charger status change, open-drain output. The ALARM is pulled low (LO) whenever the SMBus status register (0x13) has a change. The ALARM output is cleared (HI) when the SMBus status (0x13) register is read, or there is a reset. This is used to alert the host and initiate an interrupt with the host instead of having to continuously poll the charger. A 10-k $\Omega$ pull-up resistor to the host controller supply rail is needed.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 26  | PGND   | Power ground. Ground connection for the high-current power converter nodes. Only connect to the AGND node by connecting to the PowerPAD <sup>™</sup> underneath the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 27  | LODRV  | PWM low side driver output. Connect directly to the gate of the low-side NMOS power FET with a short trace.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 28  | REGN   | Low-side driver gate voltage regulator and source for high-side driver bootstrap voltage. Add a 1-µF ceramic capacitor from REGN pin to PGND pin, close to the IC. Place a small signal Schottky diode from REGN to BTST for bootstrap voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 29  | PH     | High-side driver negative supply. Connect directly to the source of the high-side NMOS FET with a short trace. This node is the common connection between the high-side FET, low-side FET, and output inductor. Connect a 0.1-μF boot-strap ceramic capacitor from BTST to PH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 30  | HIDRV  | PWM high side driver output. Connect directly to the gate of the high-side NMOS power FET with a short trace.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 31  | BTST   | High-side driver positive supply, connect pos-side of boot-strap capacitor. Connect a 0.1- $\mu$ F bootstrap capacitor from the BTST pin to the PH node. Also, connect a bootstrap diode with the anode connected to the REGN pin and the cathode connected to the BTST pin. An optional 4.7- $\Omega$ - 15- $\Omega$ series resistor is placed between the BTST pin and the bootstrap-diode/capacitor junction to slow-down the turn-on time of the high-side FET for reducing ringing due to high dv/dt of the phase node.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 32  | PVCC   | IC power positive supply. Connect directly to the drain of the high-side NMOS power FET. Recommend placing at least a 10- $\mu$ F ceramic capacitor directly from the drain of the high-side NMOS power FET to PGND. Up to 40 $\mu$ F may be needed to prevent resonance filtering inductance. Also, a 0.1- $\mu$ F decoupling ceramic capacitor is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)<sup>(1) (2)</sup>

| PARAMETER                                             | PIN                                                                                     | VALUE / UNIT    |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

|                                                       | ACN, ACP, PVCC, ACDRV, SYNN, SYNP, SRP, SRN, BATDRV, BAT, BYPASS, SYS, VCC              | –0.3 V to 30 V  |

|                                                       | PH                                                                                      | -1 V to 30 V    |

| Supply voltage range                                  | LODRV, REGN, FBO, EAI, EAO, ISYNSET, CHGEN, TS ,<br>VREF5, ACDET, IOUT, ALARM, SCL, SDA | –0.3 V to 7 V   |

|                                                       | BTST, HIDRV (with respect to AGND and PGND)                                             | -1 V to 36 V    |

| Maximum differential voltage                          | AGND-PGND                                                                               | –0.3 V to 0.3 V |

| Maximum difference voltage                            | ACP-ACN, SRP-SRN, and SYNP-SYNN                                                         | 0.6 V           |

| Operating ambient temperature range (T <sub>A</sub> ) |                                                                                         | –40°C to 85°C   |

| Maximum junction temperature (T <sub>J_MAX</sub> )    |                                                                                         | 150°C           |

| Storage temperature range (T <sub>stg</sub> )         |                                                                                         | –65°C to 150°C  |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to AGND, unless otherwise noted. Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the Databook for thermal limitations and considerations of packages.

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                                     | PIN                                                                              | MIN  | NOM MAX | UNIT |

|-----------------------------------------------|----------------------------------------------------------------------------------|------|---------|------|

| Supply voltage range                          | ACN, ACP, PVCC, ACDRV, SRP, SRN,<br>BATDRV, BAT, BYPASS, SYS, VCC, SYNN,<br>SYNP | 0    | 24      | V    |

|                                               | PH                                                                               | -0.5 | 30      | V    |

|                                               | LODRV, REGN, VREF5                                                               | 0    | 6.5     | V    |

|                                               | FBO, EAI, EAO, ISY <u>NSET, CHGEN</u> , TS ,<br>ACDET, SCL, SDA, ALARM           | 0    | 5.5     | V    |

|                                               | IOUT, ACDET                                                                      | 0    | 5.5     | V    |

|                                               | BTST, HIDRV                                                                      | 0    | 30      | V    |

| Maximum differential voltage                  | AGND-PGND                                                                        |      | 0       | V    |

| Maximum difference voltage                    | ACP-ACN, SYNN-SYNP, SRP-SRN                                                      |      | 0.5     | V    |

| Junction temperature Range (T <sub>J</sub> )  |                                                                                  | 0    | 125     | °C   |

| Storage temperature Range (T <sub>stg</sub> ) |                                                                                  | -55  | 150     | °C   |

TEXAS INSTRUMENTS

www.ti.com

# **ELECTRICAL CHARACTERISTICS**

8 Vdc  $\leq$  V<sub>(VCC)</sub>  $\leq$  24 Vdc, 0°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, all voltages with respect to AGND (unless otherwise noted)

|                             | PARAMETER                                                            | TEST CONDIT                                                                                                                                                                                                                                                    | TIONS                                                                       | MIN   | TYP | MAX    | UNIT |

|-----------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|-----|--------|------|

| BATTERY VOL                 | TAGE REGULATION                                                      |                                                                                                                                                                                                                                                                |                                                                             |       |     |        |      |

| V <sub>(BAT_ICR)</sub>      | VBAT Input voltage range                                             | V <sub>(BAT)</sub>                                                                                                                                                                                                                                             |                                                                             | 0     |     | PVCC   | V    |

|                             | Detter (Desulation )/-It                                             | Full valid voltage DAC range,                                                                                                                                                                                                                                  | $T_J = 0^{\circ}C - 85^{\circ}C$                                            | -0.4% |     | 0.4%   |      |

|                             | Battery Regulation Voltage Accuracy                                  | SMBus DAC register 0×15                                                                                                                                                                                                                                        | T <sub>J</sub> = 0°C – 125°C                                                | -0.5% |     | 0.5%   |      |

| V <sub>(VBATREG)</sub>      | BAT voltage regulation range                                         |                                                                                                                                                                                                                                                                | - I                                                                         | 9     |     | 19.2   | V    |

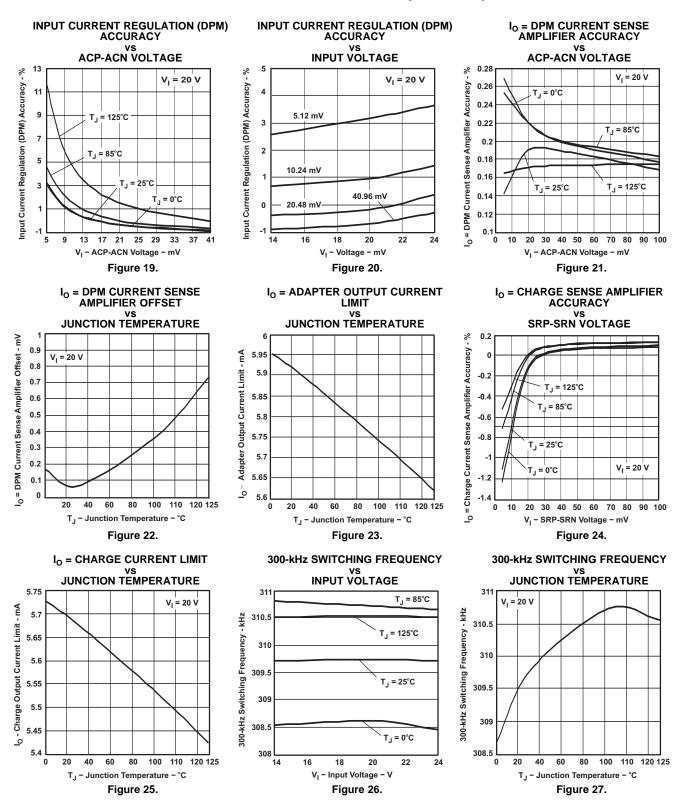

| PWM AC ADA                  | PTER INPUT CURRENT REGULATION                                        | , DPM (Dynamic Power Management),                                                                                                                                                                                                                              |                                                                             | μ     |     | 1      |      |

| $(REG_DPM) = V_{(IRE})$     | G_DPM)/R(SENSE_DPM)                                                  |                                                                                                                                                                                                                                                                |                                                                             |       |     |        |      |

| V <sub>(IREG_DPM)</sub>     | ACP-ACN differential voltage range<br>for input current regulation   | $V_{(IREG_DPM)} = V_{(ACP)} V_{(ACN)}$<br>SMBus DAC register 0x3F, bits b0-b13                                                                                                                                                                                 |                                                                             |       |     | 162.56 | mV   |

| (REG_step_DPM)              | Current regulation LSB programming current step                      | $V_{(ACP \cdot ACN)}$ / $10m\Omega$ Using a $10m\Omega$ sense resistor, $R_{(SNS)}$                                                                                                                                                                            |                                                                             |       | 128 |        | mA   |

|                             |                                                                      | $V_{cc} \ge V_{cc}$ (min), (1)                                                                                                                                                                                                                                 | $V_{(ACP)} - V_{(ACN)} > 40.96 \text{ mV}$<br>(4096 mA with 10 m $\Omega$ ) | -3%   |     | 3%     |      |

|                             | Current regulation accuracy                                          | $V_{CC} \ge V_{((BAT)} + V_{(DO-MAX)}$ , <sup>(1)</sup><br>Over differential threshold range, $V_{((REG)}$ ,<br>Does not include error induced by the                                                                                                          | $V_{(ACP)} - V_{(ACN)} > 20.48 \text{ mV}$<br>(2048 mA with 10 m $\Omega$ ) | -5%   |     | 5%     |      |

|                             |                                                                      | tolerance of the sense resistor, $R_{(SNS)}$ $$V_{(ACP)}-V_{(ACN)}>5.12\mbox{ mV} \\ (512\mbox{ mA with }10\mbox{ m}\Omega)$                                                                                                                                   |                                                                             | -25%  |     | 25%    |      |

| <b>WM BATTER</b>            | Y CHARGE CURRENT REGULATION,                                         | I <sub>(REG_CHG)</sub> = V <sub>(IREG_CHG)</sub> / R <sub>(SENSE_CHG)</sub>                                                                                                                                                                                    | - ·                                                                         |       |     | 1      |      |

| V <sub>(IREG_CHG)</sub>     | SRP-SRN differential voltage range<br>for input current regulation   | $V_{(IREG_CHG)} = V_{(SRP)} V_{(SRN)}$<br>SMBus DAC register 0×14, bits b0–b13                                                                                                                                                                                 |                                                                             | 1.28  |     | 162.56 | mV   |

| I <sub>(REG_step_CHG)</sub> | Current regulation LSB programming current step                      | $V_{(SRP\text{-}SRN)}$ / 10 m $\Omega$ Using a 10m $\Omega$ sense resistor, $R_{(SNS)}$                                                                                                                                                                        |                                                                             | 128   |     | mA     |      |

|                             | Current regulation accuracy                                          | $ \begin{array}{l} V_{CC} \geq V_{CC} \mbox{ (min),} \\ V_{CC} \geq V_{I(BAT)} + V_{(DO-MAX)}, \mbox{ (i)} \\ Over differential threshold range, V_{(IREG)}, \\ Does not include error induced by the tolerance of the sense resistor, R_{(SNS)} \end{array} $ | V <sub>(SRP-SRN)</sub> > 40.96 mV<br>(4096 mA with 10 mΩ)                   | -3%   |     | 3%     |      |

|                             |                                                                      |                                                                                                                                                                                                                                                                | V <sub>(SRP-SRN)</sub> >20.48 mV<br>(2048 mA with 10 mΩ)                    | -5%   |     | 5%     |      |

|                             |                                                                      |                                                                                                                                                                                                                                                                | $V_{(SRP-SRN)} > 5.12 \text{ mV}$<br>(512 mA with 10 m $\Omega$ )           | -25%  |     | 25%    |      |

| CURRENT SEI                 | NSE AMPLIFIERS – IBAT AMPLIFIER :                                    | and IADAPT AMPLIFIER $\rightarrow$ MUX TO IOUT                                                                                                                                                                                                                 |                                                                             | II    | I   |        |      |

| ,                           | SRP, SRN common-mode input voltage range                             |                                                                                                                                                                                                                                                                |                                                                             | 2.5   |     | 20     | V    |

| V <sub>(IOUT_IBAT)</sub>    | IOUT output voltage range with IBAT selected                         | $ \begin{array}{l} V_{(IOUT)} = V_{(SRP, \ SRN)} \times A_{(IBAT)} \\ V_{(BAT)} > 2.5 \ V \ or \ V_{(BAT)} > V_{(IOUT)} + V_{(DO\cdot MAX)}^{(1)} \end{array} $                                                                                                |                                                                             | 0     |     | 3.5    | V    |

| G <sub>(IBAT)</sub>         | Voltage gain                                                         | A <sub>(IOUT)</sub> = V <sub>(IOUT)</sub> / V <sub>(SRP, SRN)</sub>                                                                                                                                                                                            |                                                                             |       | 20  |        | V/V  |

|                             |                                                                      | $V_{(BAT)} > 2.5 V \text{ or } V_{(BAT)} >$                                                                                                                                                                                                                    | $V_{(SRP, SRN)} = 40 \text{ mV}$ and higher                                 | -2%   |     | 2%     |      |

|                             | Charge current amplifier accuracy                                    | $ \begin{array}{c} V_{(BAT)} > 2.5 \text{ V or } V_{(BAT)} > \\ V_{(IOUT)} + V_{(DO-MAX)}^{(1)} \end{array} \end{array} \begin{array}{c} V_{(SRP, SRN)} \\ V_{(SRP, SRN)} \end{array} $                                                                        | $V_{(SRP, SRN)} = 20 \text{ mV}$ and higher                                 | -3%   |     | 3%     |      |

|                             |                                                                      |                                                                                                                                                                                                                                                                | V <sub>(SRP, SRN)</sub> = 5 mV and higher                                   | -25%  |     | 25%    |      |

| ,                           | ACP, ACN Common-mode input voltage range                             |                                                                                                                                                                                                                                                                |                                                                             | 0     |     | 24     | V    |

| V <sub>(IOUT_IADAPT)</sub>  | IOUT output voltage range with<br>IADAPT selected                    |                                                                                                                                                                                                                                                                |                                                                             | 0     |     | 3.5    | V    |

| G <sub>(IADP)</sub>         | Voltage gain                                                         | A <sub>(IADP)</sub> = V <sub>(IOUT)</sub> / V <sub>(ACP, ACN)</sub>                                                                                                                                                                                            |                                                                             |       | 20  |        | V/V  |

|                             |                                                                      |                                                                                                                                                                                                                                                                | $V_{(ACP, ACN)} = 40 \text{ mV}$ and higher                                 | -2%   |     | 2%     |      |

|                             | Adapter current amplifier accuracy,<br>bq24721                       | $V_{(BAT)} > 2.5 V \text{ or } V_{(BAT)} > V_{(IOUT)} + V_{(DO-MAX)}^{(1)}$                                                                                                                                                                                    | $V_{(ACP, ACN)} = 30 \text{ mV}$ and higher                                 | -3%   |     | 3%     |      |

|                             |                                                                      | - (IOUT) * * (DO-MAA)                                                                                                                                                                                                                                          | $V_{(ACP, ACN)} = 5 \text{ mV}$ and higher                                  | -25%  |     | 25%    |      |

|                             |                                                                      |                                                                                                                                                                                                                                                                | $V_{(ACP, ACN)} = 40 \text{ mV}$ and higher                                 | -2%   |     | 2%     |      |

|                             | Adapter current amplifier accuracy,<br>bg24721C                      | $V_{(BAT)} > 2.5 V \text{ or } V_{(BAT)} > V_{(IOUT)} + V_{(DO-MAX)}^{(1)}$                                                                                                                                                                                    | $V_{(ACP, ACN)} = 30 \text{ mV}$ and higher                                 | -5%   |     | 5%     |      |

|                             | 54E (1210                                                            | $V_{(IOUT)} + V_{(DO-MAX)}$<br>$V_{(ACP, ACN)} = 5 \text{ mV and higher}$                                                                                                                                                                                      |                                                                             | -25%  |     | 25%    |      |

| (OUT_LIM)                   | IOUT output current limit                                            | IOUT shorted to AGND                                                                                                                                                                                                                                           |                                                                             | 4.5   |     |        | mA   |

| OPERATING C                 | ONDITIONS                                                            |                                                                                                                                                                                                                                                                |                                                                             | . I   | I   | 1      |      |

| / <sub>(INOP)</sub>         | $V_{(\text{VCC})},V_{(\text{PVCC})}$ , input voltage operating range | Selector and charger operational.                                                                                                                                                                                                                              |                                                                             | 8     |     | 24     | V    |

|                             | 1                                                                    | 1                                                                                                                                                                                                                                                              |                                                                             |       |     |        |      |

(1)  $V_{(DO-max)}$  is defined as the maximum drop-out voltage.  $V_{(DO-MAX)} = 1 V$  unless other wise specified. In an actual application,  $V_{(DO - MAX)} = (R_{(SNS)} \times I_O) + V_{(DSON\_HIGH\_SIDE\_FET)} + V_{(DSON\_BYPASS\_FET)}$ .

Copyright © 2005–2009, Texas Instruments Incorporated

# ELECTRICAL CHARACTERISTICS (continued)

8 Vdc  $\leq$  V<sub>(VCC)</sub>  $\leq$  24 Vdc, 0°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, all voltages with respect to AGND (unless otherwise noted)

|                          | PARAMETER                                                                | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                  | MIN  | TYP | MAX  | UNIT |

|--------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| QUIESCENT C              | URRENT – NO ADAPTER CONNECTE                                             | D                                                                                                                                                                                                                                                                                                                                                                                | L    |     |      |      |

| (VCC,PVCC)               | VCC and PVCC quiescent current                                           | $I_{(VCC,PVCC)} = (I_{(VCC)} + I_{(PVCC)})$ at $V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                                                         |      |     | 254  | μA   |

| (ACP,ACN)                | ACP and ACN quiescent current                                            | $I_{(ACP,ACN)} = (I_{(ACP)} + I_{(ACN)})$ at $V_{(ACP)} = V_{(ACN)} = V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                                   |      |     | 1    | μA   |

| (BAT)                    | BAT quiescent current                                                    | $I_{(BAT)}$ at $V_{(BAT)} = V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                                                                             |      |     | 17   | μA   |

| (SRP,SRN)                | SRP and SRN quiescent current                                            | $I_{(SRP,SRN)} = (I_{(SRP)} + I_{(SRN)})$ at $V_{(SRP)} = V_{(SRN)} = V_{(VCC)} = V_{(PVCC)} = 16.8 V$                                                                                                                                                                                                                                                                           |      |     | 1    | μA   |

| (SYNN,SYNP)              | SYNN and SYNP quiescent current                                          | $I_{(SYNN,SYNP)} = (I_{(SYNN)} + I_{(SYNP)})$ at $V_{(SYNP)} = V_{(SYNN)} = V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                             |      |     | 1    | μA   |

| (SYS)                    | SYS quiescent current                                                    | $I_{(SYS)}$ at $V_{(SYS)} = V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                                                                             |      |     | 25   | μA   |

| I <sub>(PH)</sub>        | PH quiescent current                                                     | $I_{(PH)}$ at $V_{(PH)} = V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                                                                               |      |     | 1    | μA   |

| (BTST)                   | BTST quiescent current                                                   | $I_{(BTST)}$ at $V_{(BTST)} = V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                                                                           |      |     | 1    | μA   |

| QUIESCENT C              | URRENT – ADAPTER CONNECTED A                                             | ND READY TO CHARGE                                                                                                                                                                                                                                                                                                                                                               |      |     |      | -    |

| I(VCC, PVCC)             | VCC and PVCC quiescent current                                           | $I_{(VCC,PVCC)} = (I_{(VCC)} + I_{(PVCC)} \text{ at } V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                                                   |      |     | 4.45 | mA   |

| I(ACP,ACN)               | ACP and ACN quiescent current                                            | $I_{(ACP,ACN)} = (I_{(ACP)} + I_{(ACN)})$ at $V_{(ACP)} = V_{(ACN)} = V_{(VCC)} = V_{(PVCC)} = 16.8$ V                                                                                                                                                                                                                                                                           |      |     | 815  | μA   |

| I <sub>(BAT)</sub>       | BAT quiescent current                                                    | $I_{(BAT)}$ at $V_{(BAT)} = V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                                                                             |      |     | 500  | μA   |

| I(SRP,SRN)               | SRP and SRN quiescent current                                            | $I_{(SRP,SRN)} = (I_{(SRP)} + I_{(SRN)})$ at $V_{(SRP)} = V_{(SRN)} = V_{(VCC)} = V_{(PVCC)} = 16.8$ V                                                                                                                                                                                                                                                                           |      |     | 305  | μA   |

| I(SYNN,SYNP,SYS)         | SYNN, SYNP, and SYS quiescent current                                    | $I_{(SYNN,SYNP,SYS)}$ = ( $I_{(SYNN)}$ + $I_{(SYNP)}$ + $I_{(SYS)}$ ) at $V_{(SYNP)}$ = $V_{(SYNN)}$ = $V_{(SYS)}$ = $V_{(VCC)}$ = $V_{(VCC)}$ = 16.8 V                                                                                                                                                                                                                          |      |     | 321  | μA   |

| I <sub>(PH)</sub>        | PH quiescent current                                                     | $I_{(PH)}$ at $V_{(PH)} = V_{(VCC)} = V_{(PVCC)} = 16.8 \text{ V}$                                                                                                                                                                                                                                                                                                               |      |     | 1    | μA   |

| I(BTST)                  | BTST quiescent current                                                   | $I_{(BTST)}$ at $V_{(BTST)} = V_{(VCC)} = V_{(PVCC)} = 16.8 V$                                                                                                                                                                                                                                                                                                                   |      |     | 1    | μA   |

| I <sub>(VCC_SW)</sub>    | VCC Current while converter is<br>switching including gate drive current | $\begin{array}{l} I_{(VCC\_SW)} = I_{(VCC)} \\ FPWM = 300 \text{ kHz}, \text{ charger on } (\overline{CHGEN} = LO) = \text{ENABLED} \\ Q_{(G)} \text{ at HIDRV} = Q_{(G)} \text{ at LODRV} = 30 \text{ nC}, [\text{No Load on VREF5}] \\ \text{Gate drive switching current} = Q_{(G)} \times FPWM = (30\text{nC} + 30\text{nC}) \times 300\text{kHz} = 18\text{mA} \end{array}$ |      | 25  |      | mA   |

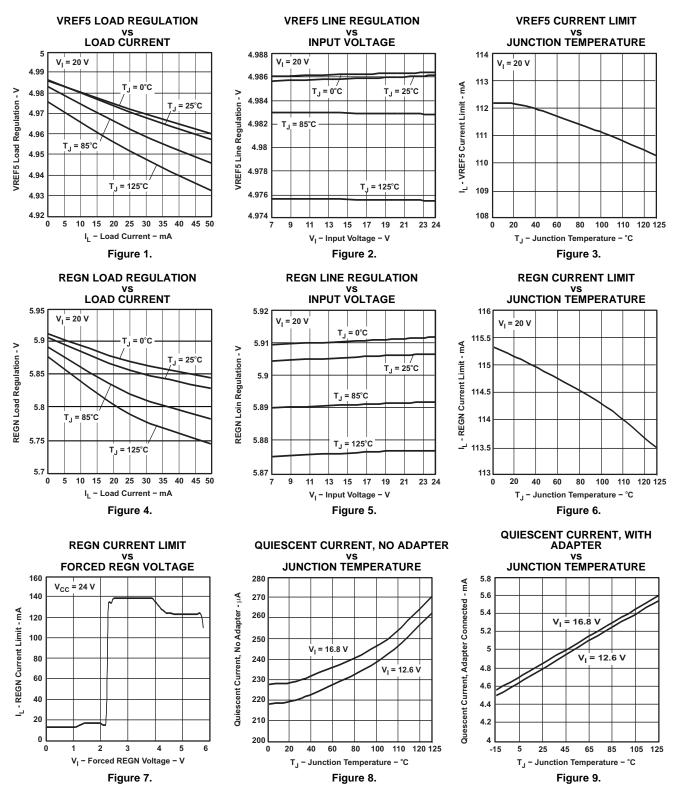

| 5-V REFEREN              | CE LDO VOLTAGE AND AC DETECTIO                                           | ON STATUS (VREF5, TURNS ON WHEN AC DETECTED)                                                                                                                                                                                                                                                                                                                                     |      |     |      | -    |

| V <sub>(VREF5)</sub>     | 5V Regulator output voltage                                              | Adapter detected (V <sub>ACDET</sub> >V <sub>(ACD)</sub> ), V <sub>CC</sub> >7 V 0 $\rightarrow$ 10 mA, source current                                                                                                                                                                                                                                                           | 4.75 | 5   | 5.25 | V    |

| V <sub>(VREF5_SAT)</sub> | Saturation voltage when VREF5 is off                                     | Adapter not detected, (V <sub>ACDET</sub> <v<sub>(ACD))<br/>0 <math>\rightarrow</math> -10 mA, ac adapter inserted, C<sub>0</sub> = 1 µF, discharge Load</v<sub>                                                                                                                                                                                                                 |      |     | 0.3  | V    |

| I(VREF5_LIM)             | Short-circuit current                                                    | V <sub>(VREF5)</sub> = AGND                                                                                                                                                                                                                                                                                                                                                      |      | 20  |      | mA   |

| UNDERVOLTA               | GE LOCKOUT CIRCUIT                                                       |                                                                                                                                                                                                                                                                                                                                                                                  |      |     |      |      |

|                          | Undervoltage lockout threshold                                           | VREF5 rising, POR mode set at VREF5 < V <sub>(UVLO)</sub>                                                                                                                                                                                                                                                                                                                        |      | 3.7 |      | V    |

| UVLO                     | V <sub>(UVLO)</sub> hysteresis                                           | VREF5 falling                                                                                                                                                                                                                                                                                                                                                                    |      | 100 |      | mV   |

| SBS-Like SMB             | Bus LOGIC LEVELS                                                         |                                                                                                                                                                                                                                                                                                                                                                                  |      |     |      |      |

| VIL                      | Input low threshold level                                                | 2.7 V < V <sub>(pull-up)</sub> < 5.5 V, SDA and SCL                                                                                                                                                                                                                                                                                                                              |      |     | 0.8  | V    |

| V <sub>IH</sub>          | Input high threshold level                                               | 2.7 V < V <sub>(pull-up)</sub> < 5.5 V, SDA and SCL                                                                                                                                                                                                                                                                                                                              | 2.1  |     |      | V    |

| (bias)                   | Input bias current                                                       | 2.7 V < V <sub>(pull-up)</sub> < 5.5 V, SDA and SCL                                                                                                                                                                                                                                                                                                                              |      |     | 1    | μΑ   |

| ALARM OPEN               | DRAIN OUTPUT                                                             | •                                                                                                                                                                                                                                                                                                                                                                                | I    |     |      | -    |

| V <sub>(ALARM_sat)</sub> | ALARM output low saturation level                                        | I <sub>(ALARM)</sub> = 5mA                                                                                                                                                                                                                                                                                                                                                       |      |     | 0.5  | V    |

| lkg(ALARM)               | ALARM leakage current                                                    | V <sub>(ALARM)</sub> = 5V                                                                                                                                                                                                                                                                                                                                                        |      |     | 1    | μA   |

| THERMAL SH               | UTDOWN, IC OVERTEMPERATURE PF                                            | ROTECTION                                                                                                                                                                                                                                                                                                                                                                        |      |     |      |      |

| T <sub>(SHUT)</sub>      | Thermal shutdown Threshold                                               | $T_J$ rising, Charge disabled at $T_J > T_{(SHUT)}$                                                                                                                                                                                                                                                                                                                              |      | 145 |      | °C   |

| T <sub>(SHUTH)</sub>     | Hysteresis                                                               | $T_J$ falling, Charge enabled at $T_J < T_{(SHUT)} - T_{(SHUTH)}$                                                                                                                                                                                                                                                                                                                |      | 15  |      | °C   |

|                          | Deglitch time, thermal shutdown                                          | T, rising/falling                                                                                                                                                                                                                                                                                                                                                                |      | 8   |      | ms   |

TEXAS INSTRUMENTS

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

8 Vdc  $\leq$  V<sub>(VCC)</sub>  $\leq$  24 Vdc, 0°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, all voltages with respect to AGND (unless otherwise noted)

|                                   | PARAMETER                                                                                    | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MIN   | TYP  | MAX   | UNIT                          |

|-----------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------------------------------|

| THERMISTOR                        | R COMPARATORS, TS                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |      |       |                               |

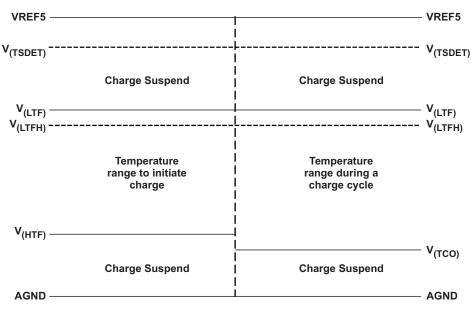

| V <sub>(LTF)</sub>                | Cold temperature threshold, TS pin voltage                                                   | V <sub>(TS)</sub> rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72.8  | 73.5 | 74.2  | %VREF5                        |