# 16-BIT, 500 MSPS 2×–8× INTERPOLATING DUAL-CHANNEL DIGITAL-TO-ANALOG CONVERTER (DAC)

## FEATURES

- 500 MSPS

- Selectable 2×–8× Interpolation

- On-Chip PLL/VCO Clock Multiplier

- Full IQ Compensation Including Offset, Gain, and Phase

- Flexible Input Options:

- FIFO With Latch on External or Internal Clock

- Even/Odd Multiplexed Input

- Single Port Demultiplexed Input

- Complex Mixer With 32-Bit NCO

- Fixed Frequency Mixer With  $f_s/4$  and  $f_s/2$

- 1.8-V or 3.3-V I/O Voltage

- On-Chip 1.2-V Reference

- Differential Scalable Output: 2 mA to 20 mA

- Pin Compatible to DAC5686

- High Performance

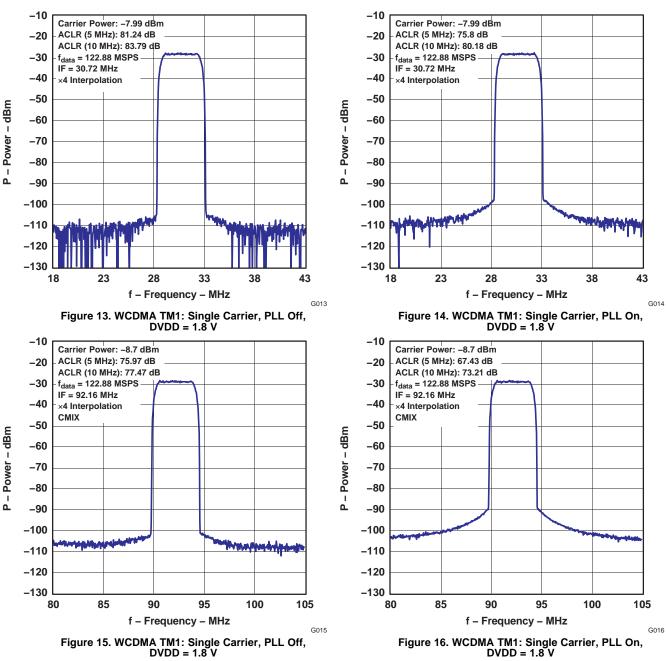

- 81-dBc ACLR WCDMA TM1 at 30.72 MHz

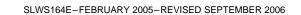

- 72-dBc ACLR WCDMA TM1 at 153.6 MHz

- Package: 100-Pin HTQFP

## **APPLICATIONS**

- Cellular Base Transceiver Station Transmit Channel

- CDMA: W-CDMA, CDMA2000, TD-SCDMA

- TDMA: GSM, IS-136, EDGE/UWC-136

- OFDM: 802.16

- Cable Modem Termination System

## DESCRIPTION

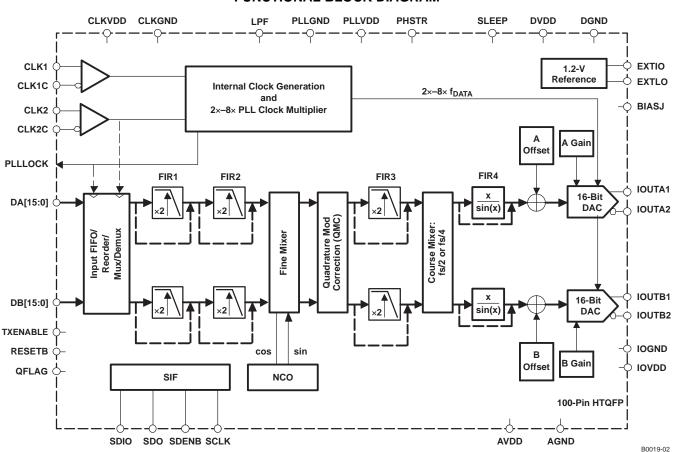

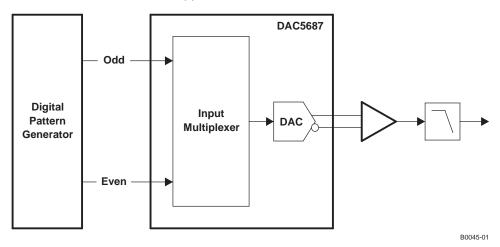

The DAC5687 is a dual-channel 16-bit high-speed digital-to-analog converter (DAC) with integrated  $2\times$ ,  $4\times$ , and  $8\times$  interpolation filters, a complex numerically

controlled oscillator (NCO), onboard clock multiplier, IQ compensation, and on-chip voltage reference. The DAC5687 is pin-compatible to the DAC5686, requiring only changes in register settings for most applications, and offers additional features and superior linearity, noise, crosstalk, and PLL phase noise performance.

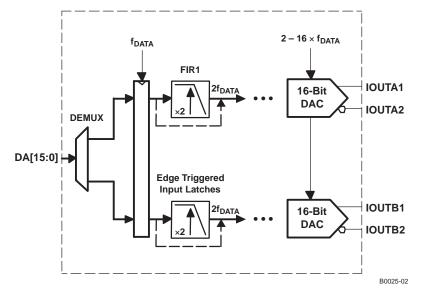

The DAC5687 has six signal processing blocks: two interpolate-by-two digital filters, a fine frequency mixer with 32-bit NCO, a quadrature modulation compensation block, another interpolate-by-two digital filter, and a coarse frequency mixer with  $f_S/2$  or  $f_S/4$ . The different modes of operation enable or bypass the signal processing blocks.

The coarse and fine mixers can be combined to span a wider range of frequencies with fine resolution. The DAC5687 allows both complex or real output. Combining the frequency upconversion and complex output produces a Hilbert transform pair that is output from the two DACs. An external RF quadrature modulator then performs the final single-sideband upconversion.

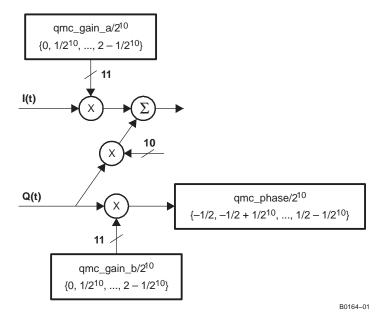

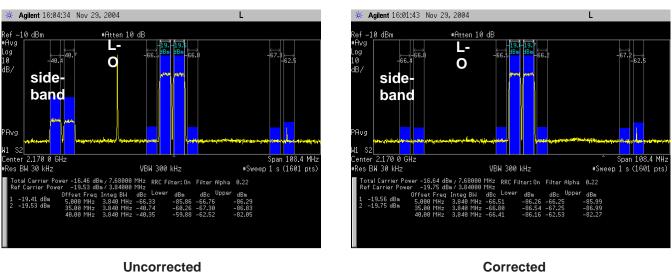

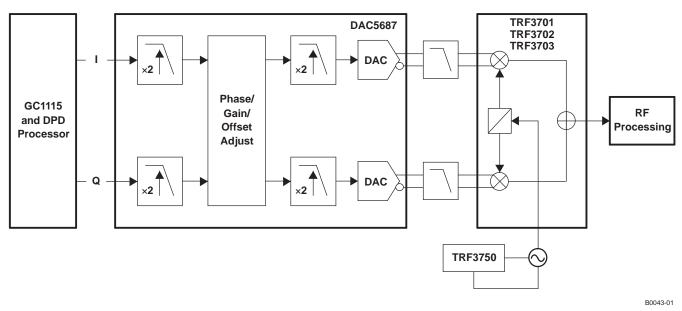

The IQ compensation feature allows optimization of phase, gain, and offset to maximize sideband rejection and minimize LO feedthrough for an analog quadrature modulator.

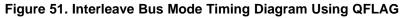

The DAC5687 includes several input options: single-port interleaved data, even and odd multiplexing at half-rate, and an input FIFO with either external or internal clock to ease the input timing ambiguity when the DAC5687 is clocked at the DAC output sample rate.

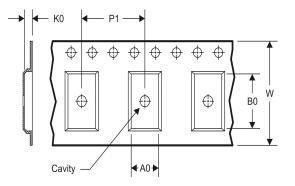

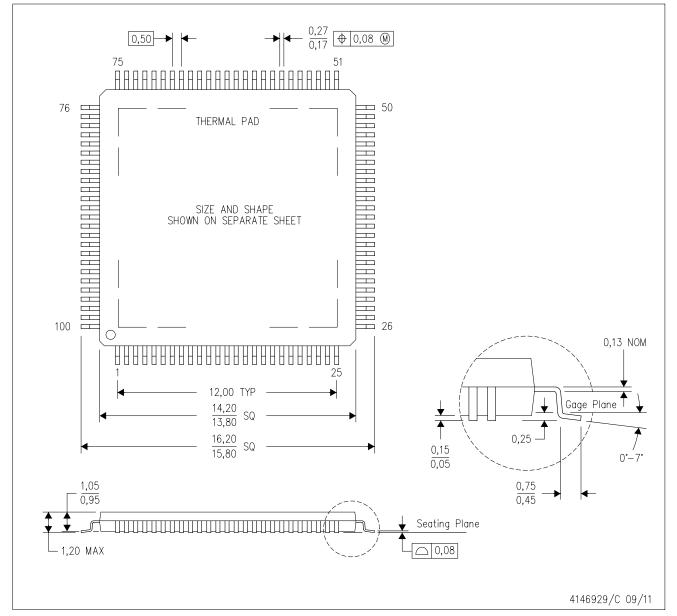

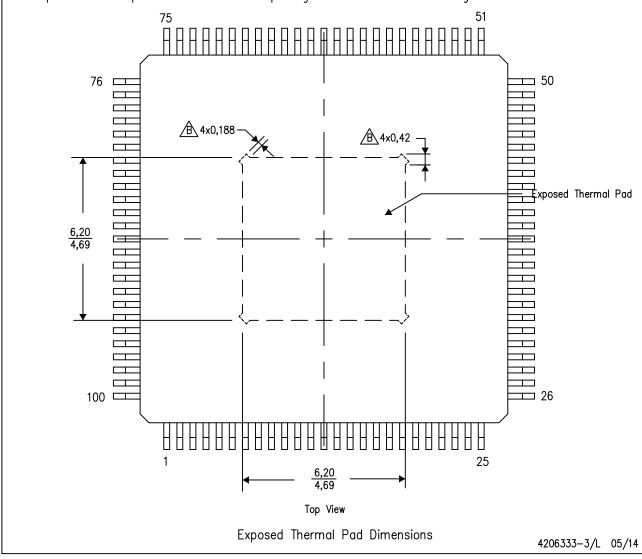

#### **ORDERING INFORMATION**

| T <sub>A</sub> | Package Device                                                             |

|----------------|----------------------------------------------------------------------------|

| -40°C to 85°C  | 100 HTQFP <sup>(1)</sup> (PZP) PowerPAD™<br>package, plastic quad flatpack |

|                | DAC5687IPZP                                                                |

(1) Thermal pad size:  $6 \text{ mm} \times 6 \text{ mm}$ .

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments. Excel is a trademark of Microsoft Corporation. Matlab is a trademark of The MathWorks, Inc. All other trademarks are the property of their respective owners.

## DAC5687

#### SLWS164E-FEBRUARY 2005-REVISED SEPTEMBER 2006

Res.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

2

3

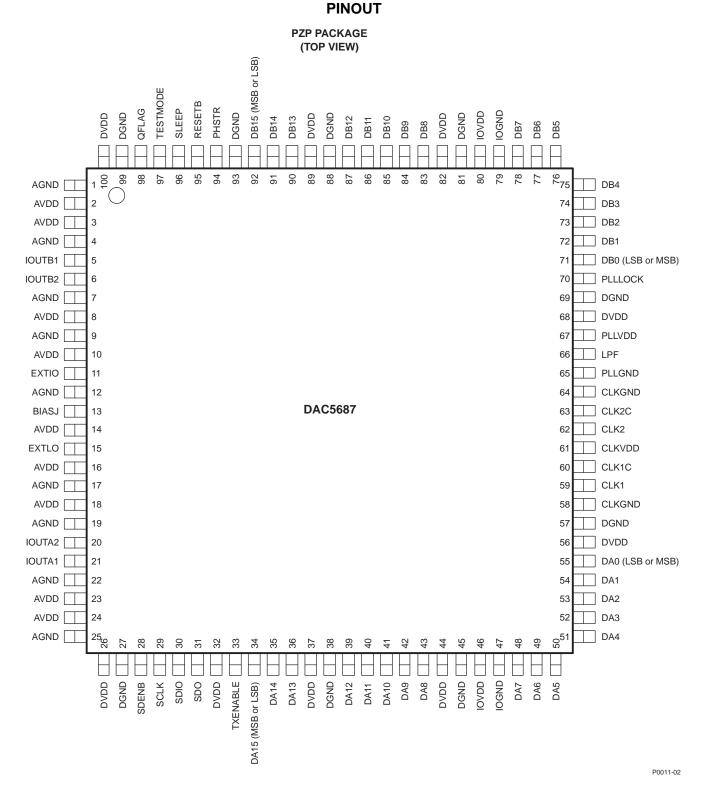

### **TERMINAL FUNCTIONS**

|          | TERMINAL                                  |     | DECODIDEION                                                                                                                                                                                                                                  |  |  |

|----------|-------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO.                                       | I/O | DESCRIPTION                                                                                                                                                                                                                                  |  |  |

| AGND     | 1, 4, 7, 9, 12,<br>17, 19, 22, 25         | I   | Analog ground return                                                                                                                                                                                                                         |  |  |

| AVDD     | 2, 3, 8, 10, 14,<br>16, 18, 23, 24        | I   | Analog supply voltage                                                                                                                                                                                                                        |  |  |

| BIASJ    | 13                                        | 0   | Full-scale output current bias                                                                                                                                                                                                               |  |  |

| CLK1     | 59                                        | I   | In PLL clock mode and dual clock modes, provides data input rate clock. In external clock mode, provides optional input data rate clock to FIFO latch. When the FIFO is disabled, CLK1 is not used and can be left unconnected.              |  |  |

| CLK1C    | 60                                        | Ι   | Complementary input of CLK1.                                                                                                                                                                                                                 |  |  |

| CLK2     | 62                                        | I   | External and dual clock mode clock input. In PLL mode, CLK2 is unused and can be left unconnected.                                                                                                                                           |  |  |

| CLK2C    | 63                                        | Ι   | Complementary input of CLK2. In PLL mode, CLK2C is unused and can be left unconnected.                                                                                                                                                       |  |  |

| CLKGND   | 58, 64                                    | I   | Ground return for internal clock buffer                                                                                                                                                                                                      |  |  |

| CLKVDD   | 61                                        | I   | Internal clock buffer supply voltage                                                                                                                                                                                                         |  |  |

| DA[15:0] | 34–36, 39–43,<br>48–55                    | I   | A-channel data bits 0 through 15. DA15 is most significant data bit (MSB). DA0 is least significant data bit (LSB). Order can be reversed by register change.                                                                                |  |  |

| DB[15:0] | 71–78, 83–87,<br>90–92                    | I   | B-channel data bits 0 through 15. DB15 is most significant data bit (MSB). DB0 is least significant data bit (LSB). Order can be reversed by register change.                                                                                |  |  |

| DGND     | 27, 38, 45, 57,<br>69, 81, 88, 93,<br>99  | I   | Digital ground return                                                                                                                                                                                                                        |  |  |

| DVDD     | 26, 32, 37, 44,<br>56, 68, 82, 89,<br>100 | I   | Digital supply voltage                                                                                                                                                                                                                       |  |  |

| EXTIO    | 11                                        | I/O | Used as external reference input when internal reference is disabled (i.e., EXTLO connected to AVDD). Used as internal reference output when EXTLO = AGND, requires a $0.1-\mu$ F decoupling capacitor to AGND when used as reference output |  |  |

| EXTLO    | 15                                        | I/O | Internal/external reference select. Internal reference selected when tied to AGND, external reference selected when tied to AVDD. Output only when atest is not zero (register 0x1B bits 7 to 3).                                            |  |  |

| IOUTA1   | 21                                        | 0   | A-channel DAC current output. Full scale when all input bits are set 1                                                                                                                                                                       |  |  |

| IOUTA2   | 20                                        | 0   | A-channel DAC complementary current output. Full scale when all input bits are 0                                                                                                                                                             |  |  |

| IOUTB1   | 5                                         | 0   | B-channel DAC current output. Full scale when all input bits are set 1                                                                                                                                                                       |  |  |

| IOUTB2   | 6                                         | 0   | B-channel DAC complementary current output. Full scale when all input bits are 0                                                                                                                                                             |  |  |

| IOGND    | 47, 79                                    | Ι   | Digital I/O ground return                                                                                                                                                                                                                    |  |  |

| IOVDD    | 46, 80                                    | Ι   | Digital I/O supply voltage                                                                                                                                                                                                                   |  |  |

| LPF      | 66                                        | Ι   | PLL loop filter connection                                                                                                                                                                                                                   |  |  |

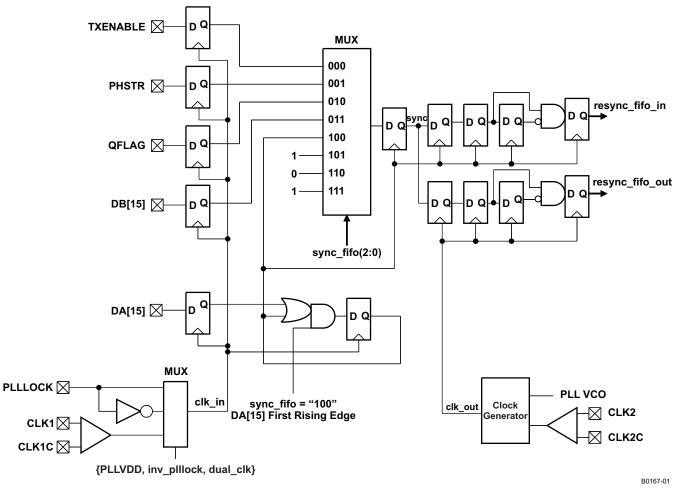

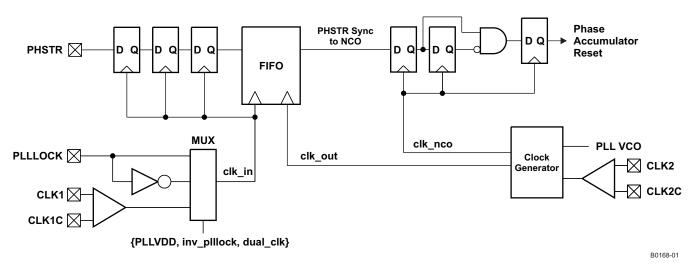

| PHSTR    | 94                                        | I   | Synchronization input signal that can be used to initialize the NCO, coarse mixer, internal clock divider, and/or FIFO circuits.                                                                                                             |  |  |

| PLLGND   | 65                                        | Ι   | Ground return for internal PLL                                                                                                                                                                                                               |  |  |

| PLLVDD   | 67                                        | Ι   | PLL supply voltage. When PLLVDD is 0 V, the PLL is disabled.                                                                                                                                                                                 |  |  |

| PLLLOC   | K 70                                      | 0   | In PLL mode, provides PLL lock status bit or internal clock signal. PLL is locked to input clock when high. In external clock mode, provides input rate clock.                                                                               |  |  |

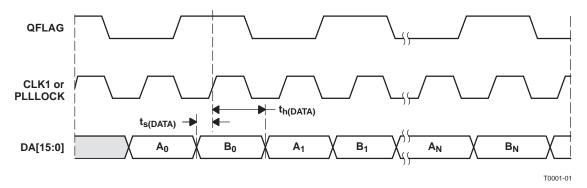

| QFLAG    | 98                                        | I   | When qflag register is 1, the QFLAG pin is used by the user during interleaved data input mode to identify the B sample. High QFLAG indicates B sample. Must be repeated every B sample.                                                     |  |  |

| RESETB   | 95                                        | Ι   | Resets the chip when low. Internal pullup                                                                                                                                                                                                    |  |  |

| SCLK     | 29                                        | Ι   | Serial interface clock                                                                                                                                                                                                                       |  |  |

| SDENB    | 28                                        | Ι   | Active-low serial data enable, always an input to the DAC5687                                                                                                                                                                                |  |  |

| SDIO     | 30                                        | I/O | Bidirectional serial data in three-pin interface mode, input-only in four-pin interface mode. Three-pin mode is the default after chip reset.                                                                                                |  |  |

| SDO      | 31                                        | 0   | Serial interface data, unidirectional data output, if SDIO is an input. SDO is in the high-impedance state when the three-pin interface mode is selected (register 0x04 bit 7).                                                              |  |  |

#### **TERMINAL FUNCTIONS (continued)**

| TERMINAL         I/O         DESCRIPTION |    | 1/0         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------|----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          |    | DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SLEEP                                    | 96 | I           | Asynchronous hardware power-down input. Active-High. Internal pulldown.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

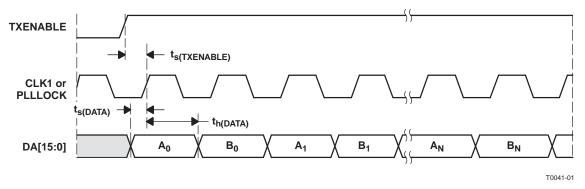

| TXENABLE                                 | 33 | I           | TXENABLE has two purposes. In all modes, TXENABLE must be high for the DATA to the DAC to be enabled. When TXENABLE is low, the digital logic section is forced to all 0, and any input data presented to DA[15:0] and DB[15:0] is ignored. In interleaved data mode, when the qflag register bit is cleared, TXENABLE is used to synchronizes the data to channels A and B. The first data after the rising edge of TXENABLE is treated as A data, while the next data is treated as B data, and so on. |

| TESTMODE                                 | 97 | I           | TESTMODE is DGND for the user                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                                             |                                            | UNIT                     |

|------------------|-----------------------------------------------------------------------------|--------------------------------------------|--------------------------|

|                  |                                                                             | AVDD <sup>(2)</sup>                        | –0.5 V to 4 V            |

|                  |                                                                             | DVDD <sup>(3)</sup>                        | –0.5 V to 2.3 V          |

|                  | Supply voltage range<br>Peak input current (any<br>Peak total input current | CLKVDD <sup>(2)</sup>                      | –0.5 V to 4 V            |

|                  |                                                                             | IOVDD <sup>(2)</sup>                       | –0.5 V to 4 V            |

|                  | Voltage between AGND<br>Supply voltage range<br>Peak input current (any     | PLLVDD <sup>(2)</sup>                      | –0.5 V to 4 V            |

|                  |                                                                             | , DGND, CLKGND, PLLGND, and IOGND          | –0.5 V to 0.5 V          |

|                  |                                                                             | AVDD to DVDD                               | –0.5 V to 2.6 V          |

|                  | Supply voltage range                                                        | DA[15:0] <sup>(4)</sup>                    | -0.5 V to IOVDD + 0.5 V  |

|                  |                                                                             | DB[15:0] <sup>(4)</sup>                    | -0.5 V to IOVDD + 0.5 V  |

|                  |                                                                             | SLEEP <sup>(4)</sup>                       | -0.5 V to IOVDD + 0.5 V  |

|                  |                                                                             | CLK1/2, CLK1/2C <sup>(3)</sup>             | -0.5 V to CLKVDD + 0.5 V |

|                  |                                                                             | RESETB <sup>(4)</sup>                      | -0.5 V to IOVDD + 0.5 V  |

|                  |                                                                             | LPF <sup>(4)</sup>                         | -0.5 V to PLLVDD + 0.5 V |

|                  |                                                                             | IOUT1, IOUT2 <sup>(2)</sup>                | -1 V to AVDD + 0.5 V     |

|                  |                                                                             | EXTIO, BIASJ <sup>(2)</sup>                | -0.5 V to AVDD + 0.5 V   |

|                  |                                                                             | EXTLO <sup>(2)</sup>                       | -0.5 V to IAVDD + 0.5 V  |

|                  | Peak input current (any                                                     | input)                                     | 20 mA                    |

|                  | Peak total input current                                                    | (all inputs)                               | 30 mA                    |

| T <sub>A</sub>   | Operating free-air tempe                                                    | erature range (DAC5687I)                   | –40°C to 85°C            |

| T <sub>stg</sub> | Storage temperature rar                                                     | nge                                        | –65°C to 150°C           |

|                  | Lead temperature 1,6 m                                                      | m (1/16 inch) from the case for 10 seconds | 260°C                    |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Measured with respect to AGND.

(3) Measured with respect to DGND.

(4) Measured with respect to IOGND.

## THERMAL CHARACTERISTICS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|               | Thermal Conductivity                            | 100 HTQFP | UNIT |

|---------------|-------------------------------------------------|-----------|------|

| TJ            | Junction temperature <sup>(2)</sup>             | 105       | °C   |

| 0             | Theta junction-to-ambient (still air)           | 19.88     | °C/W |

| $\theta_{JA}$ | Theta junction-to-ambient (150 lfm) (0.762 m/s) | 14.37     | °C/W |

(1) Air flow or heat sinking reduces  $\theta_{JA}$  and is highly recommended.

(2) Air flow or heat sinking required for sustained operation at 85°C and maximum operating conditions to maintain junction temperature.

#### TEXAS INSTRUMENTS www.ti.com

## **THERMAL CHARACTERISTICS (continued)**

over operating free-air temperature range (unless otherwise noted)

| Thermal Conductivity |                        | 100 HTQFP | UNIT |  |

|----------------------|------------------------|-----------|------|--|

| $\theta_{JC}$        | Theta junction-to-case | 0.12      | °C/W |  |

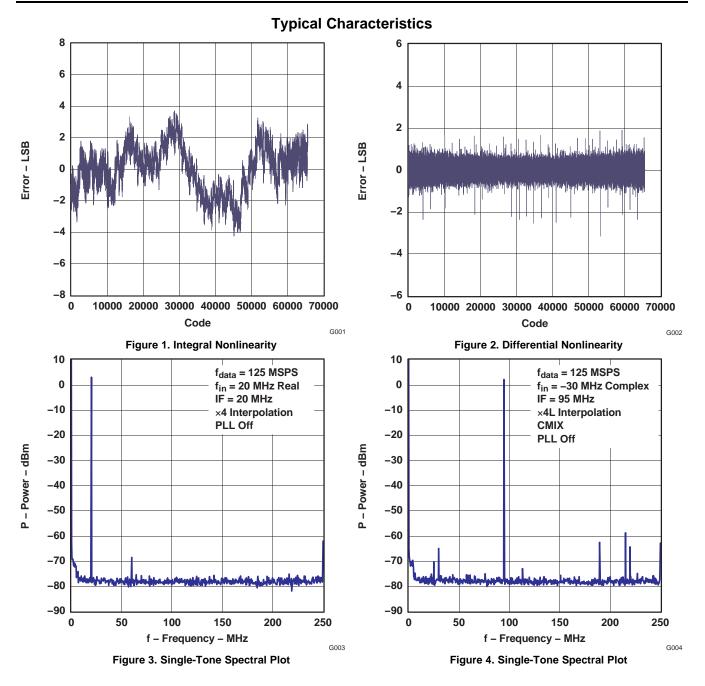

## **ELECTRICAL CHARACTERISTICS (DC SPECIFICATIONS)**

over recommended operating free-air temperature range, AVDD = 3.3 V, CLKVDD = 3.3 V, PLLVDD = 3.3 V, IOVDD = 3.3 V, DVDD = 1.8 V, IOUT<sub>FS</sub> = 19.2 mA (unless otherwise noted)

|                    | PARAMETER                                        | TEST CONDITIONS                                                                     | MIN             | TYP   | MAX             | UNIT             |

|--------------------|--------------------------------------------------|-------------------------------------------------------------------------------------|-----------------|-------|-----------------|------------------|

| RESOLU             | JTION                                            |                                                                                     | 16              |       |                 | Bits             |

| DC ACC             | URACY <sup>(1)</sup>                             | 1                                                                                   |                 |       |                 |                  |

| INL                | Integral nonlinearity                            | 1 LSB = IOUT <sub>FS</sub> /2 <sup>16</sup><br>T <sub>MIN</sub> to T <sub>MAX</sub> |                 | ±4    |                 | LSB              |

| DNL                | Differential nonlinearity                        |                                                                                     |                 | ±4    |                 | LSB              |

| ANALO              | G OUTPUT                                         | ·                                                                                   |                 |       |                 |                  |

|                    | Coarse gain linearity                            |                                                                                     |                 | ±0.04 |                 | LSB              |

|                    | Fine gain linearity                              | Worst-case error from ideal linearity                                               |                 | ±3    |                 | LSB              |

|                    | Offset error                                     | Mid code offset                                                                     |                 | 0.01  |                 | %FSR             |

|                    |                                                  | Without internal reference                                                          |                 | 1     |                 | %FSR             |

|                    | Gain error                                       | With internal reference                                                             |                 | 0.7   |                 | %FSR             |

|                    | Gain mismatch                                    | With internal reference, dual DAC, and SSB mode                                     | -2              |       | 2               | %FSR             |

|                    | Minimum full-scale output current <sup>(2)</sup> |                                                                                     |                 | 2     |                 | mA               |

|                    | Maximum full-scale output current <sup>(2)</sup> |                                                                                     |                 | 20    |                 | mA               |

|                    | Output compliance range <sup>(3)</sup>           | IOUT <sub>FS</sub> = 20 mA                                                          | AVDD –<br>0.5 V |       | AVDD<br>+ 0.5 V | V                |

|                    | Output resistance                                |                                                                                     |                 | 300   |                 | kΩ               |

|                    | Output capacitance                               |                                                                                     |                 | 5     |                 | pF               |

| REFERE             | ENCE OUTPUT                                      |                                                                                     |                 |       |                 |                  |

|                    | Reference voltage                                |                                                                                     | 1.14            | 1.2   | 1.26            | V                |

|                    | Reference output current <sup>(4)</sup>          |                                                                                     |                 | 100   |                 | nA               |

| REFERE             |                                                  |                                                                                     |                 |       |                 |                  |

| V <sub>EXTIO</sub> | Input voltage range                              |                                                                                     | 0.1             |       | 1.25            | V                |

|                    | Input resistance                                 |                                                                                     |                 | 1     |                 | MΩ               |

|                    | Small signal bandwidth                           |                                                                                     |                 | 1.4   |                 | MHz              |

|                    | Input capacitance                                |                                                                                     |                 | 100   |                 | pF               |

| TEMPER             | RATURE COEFFICIENTS                              |                                                                                     |                 |       |                 |                  |

|                    | Offset drift                                     |                                                                                     |                 | ±1    |                 | ppm of<br>FSR/°C |

|                    | Gain drift                                       | Without internal reference                                                          |                 | ±15   |                 | ppm of           |

|                    |                                                  | With internal reference                                                             |                 | ±30   |                 | FSR/°C           |

|                    | Reference voltage drift                          |                                                                                     |                 | ±8    |                 | ppm of<br>FSR/°C |

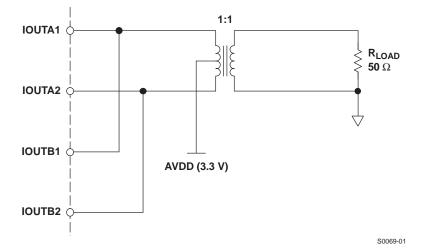

(1) Measured differential across IOUTA1 and IOUTA2 or IOUTB1 and IOUTB2 with 25  $\Omega$  each to AVDD.

(2) Nominal full-scale current, IOUT<sub>FS</sub>, equals 32× the IBIAS current.

(3) The upper limit of the output compliance is determined by the CMOS process. Exceeding this limit may result in transistor breakdown, resulting in reduced reliability of the DAC5687 device. The lower limit of the output compliance is determined by the load resistors and full-scale output current. Exceeding the limits adversely affects distortion performance and integral nonlinearity.

(4) Use an external buffer amplifier with high impedance input to drive any external load.

## **ELECTRICAL CHARACTERISTICS (DC SPECIFICATIONS) (continued)**

over recommended operating free-air temperature range, AVDD = 3.3 V, CLKVDD = 3.3 V, PLLVDD = 3.3 V, IOVDD = 3.3 V, DVDD = 1.8 V, IOUT<sub>FS</sub> = 19.2 mA (unless otherwise noted)

|                     | PARAMETER                             | TEST CONDITIONS                                  | MIN  | TYP  | MAX  | UNIT   |

|---------------------|---------------------------------------|--------------------------------------------------|------|------|------|--------|

| POWER S             | SUPPLY                                |                                                  |      |      |      |        |

| AVDD                | Analog supply voltage                 |                                                  | 3    | 3.3  | 3.6  | V      |

| DVDD                | Digital supply voltage                |                                                  | 1.71 | 1.8  | 2.15 | V      |

| CLKVDD              | Clock supply voltage                  |                                                  | 3    | 3.3  | 3.6  | V      |

| IOVDD               | I/O supply voltage                    |                                                  | 1.71 |      | 3.6  | V      |

| PLLVDD              | PLL supply voltage                    |                                                  | 3    | 3.3  | 3.6  | V      |

|                     |                                       | Mode 5 <sup>(5)</sup>                            |      | 41   |      |        |

| I <sub>AVDD</sub>   | Analog supply current                 | Mode 6 <sup>(5)</sup>                            |      | 80   |      | mA     |

| I <sub>DVDD</sub>   | Digital supply current <sup>(5)</sup> | Mode 6 <sup>(5)</sup>                            |      | 587  |      | mA     |

| I <sub>CLKVDD</sub> | Clock supply current <sup>(5)</sup>   | Mode 6 <sup>(5)</sup>                            |      | 5    |      | mA     |

| I <sub>PLLVDD</sub> | PLL supply current <sup>(5)</sup>     | Mode 6 <sup>(5)</sup>                            |      | 20   |      | mA     |

| IIOVDD              | IO supply current <sup>(5)</sup>      | Mode 6 <sup>(5)</sup>                            |      | 2    |      | mA     |

| I <sub>AVDD</sub>   | Sleep mode AVDD supply current        | Sleep mode (SLEEP pin high), CLK2 = 500<br>MHz   |      | 1    |      | mA     |

| I <sub>DVDD</sub>   | Sleep mode DVDD supply current        | Sleep mode (SLEEP pin high), CLK2 = 500<br>MHz   |      | 2    |      | mA     |

| I <sub>CLKVDD</sub> | Sleep mode CLKVDD supply current      | Sleep mode (SLEEP pin high), CLK2 = 500<br>MHz   |      | 0.25 |      | mA     |

| I <sub>PLLVDD</sub> | Sleep mode PLLVDD supply current      | Sleep mode (SLEEP pin high), CLK2 = 500<br>MHz   |      | 0.6  |      | mA     |

| I <sub>IOVDD</sub>  | Sleep mode IOVDD supply current       | Sleep mode (SLEEP pin high), CLK2 = 500<br>MHz   |      | 0.6  |      | mA     |

|                     |                                       | Mode 1 <sup>(5)</sup> AVDD = 3.3 V, DVDD = 1.8 V |      | 750  |      |        |

|                     |                                       | Mode 2 <sup>(5)</sup> AVDD = 3.3 V, DVDD = 1.8 V |      | 910  |      |        |

|                     |                                       | Mode 3 <sup>(5)</sup> AVDD = 3.3 V, DVDD = 1.8 V |      | 760  |      |        |

|                     |                                       | Mode 4 <sup>(5)</sup> AVDD = 3.3 V, DVDD = 1.8 V |      | 1250 |      |        |

| PD                  | Power dissipation                     | Mode 5 <sup>(5)</sup> AVDD = 3.3 V, DVDD = 1.8 V |      | 1250 |      | mW     |

|                     |                                       | Mode 6 <sup>(5)</sup> AVDD = 3.3 V, DVDD = 1.8 V |      | 1410 |      |        |

|                     |                                       | Mode 7 <sup>(5)</sup> AVDD = 3.3 V, DVDD = 1.8 V |      | 1400 | 1750 |        |

|                     |                                       | Sleep mode (SLEEP pin high), CLK2 = 500<br>MHz   |      | 11   | 20   |        |

| APSRR               | Device complex sets estimation        |                                                  | -0.2 |      | 0.2  | %FSR/V |

| DPSRR               | Power supply rejection ratio          |                                                  | -0.2 |      | 0.2  | %FSR/V |

(5) MODE 1 – MODE 7:

a. Mode 1: X2, PLL off, CLK2 = 320 MHz, DACA and DACB on, IF = 5 MHz

b. Mode 2: X4 QMC, PLL on, CLK1 = 125 MHz, DACA and DACB on, IF = 5 MHz

c. Mode 3: X4 CMIX, PLL off, CLK2 = 500 MHz, DACA off and DACB on, IF = 150 MHz

d. Mode 4: X4L FMIX CMIX, PLL off, CLK2 = 500 MHz, DACA off and DACB on, IF = 150 MHz

e. Mode 5: X4L FMIX CMIX, PLL on, CLK1 = 125 MHz, DACA off and DACB on, IF = 150 MHz

f. Mode 6: X4L FMIX CMIX, PLL on, CLK1 = 125 MHz, DACA on and DACB on, IF = 150 MHz

g. Mode 7: X8 FMIX CMIX, PLL on, CLK1 = 62.5 MHz, DACA and DACB on, IF = 150 MHz

7

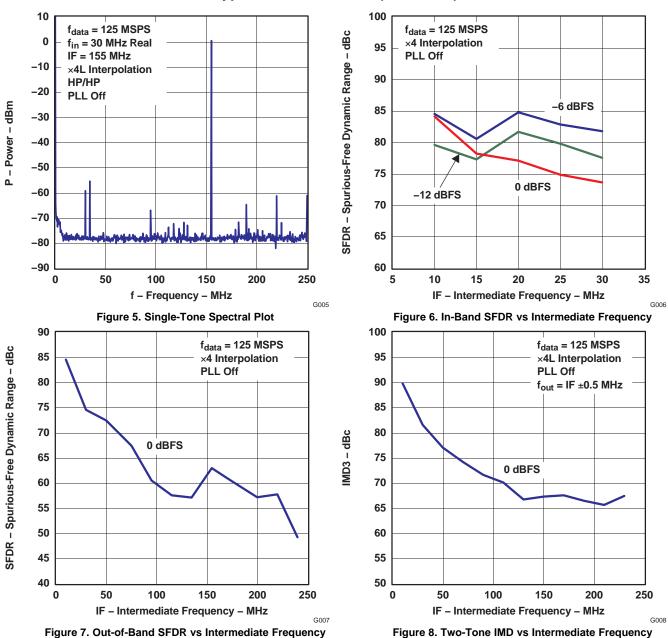

## ELECTRICAL CHARACTERISTICS (AC SPECIFICATIONS)<sup>(1)</sup>

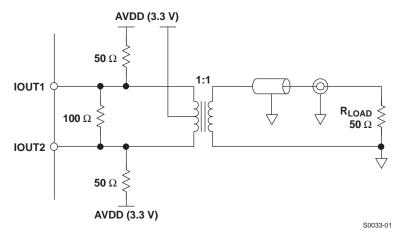

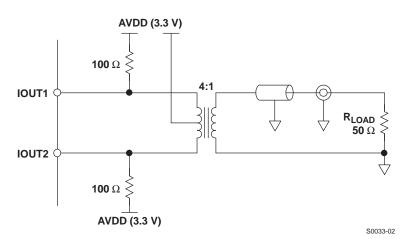

over recommended operating free-air temperature range, AVDD = 3.3 V, CLKVDD = 3.3 V, PLLVDD = 0 V (= 3.3 V for PLL clock mode), IOVDD = 3.3 V, DVDD = 1.8 V, IOUT<sub>FS</sub> = 19.2 mA, external clock mode, 4:1 transformer output termination,  $50-\Omega$  doubly terminated load (unless otherwise noted)

|                      | PARAMETER                                                          | TEST CONDITIONS                                                                                                                 | MIN               | TYP  | MAX | UNIT |

|----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------|------|-----|------|

| ANALOG               | OUTPUT                                                             |                                                                                                                                 |                   |      |     |      |

| f <sub>CLK</sub>     | Maximum output update rate                                         |                                                                                                                                 | 500               |      |     | MSPS |

| t <sub>s(DAC)</sub>  | Output settling time to 0.1%                                       | Transition: Code 0x0000 to 0xFFFF                                                                                               |                   | 10.4 |     | ns   |

| t <sub>pd</sub>      | Output propagation delay                                           |                                                                                                                                 |                   | 3    |     | ns   |

| t <sub>r(IOUT)</sub> | Output rise time 10% to 90%                                        |                                                                                                                                 |                   | 2    |     | ns   |

| t <sub>f(IOUT)</sub> | Output fall time 90% to 10%                                        |                                                                                                                                 |                   | 2    |     | ns   |

|                      | ORMANCE                                                            |                                                                                                                                 |                   |      |     |      |

|                      |                                                                    | X2, PLL off, CLK2 = 250 MHz, DAC A and DAC B on, IF = 5.1 MHz, first Nyquist zone < $f_{DATA}/2$                                |                   | 78   |     |      |

| SFDR                 | Spurious free dynamic range <sup>(2)</sup>                         | X4, PLL off, CLK2 = 500 MHz, DAC A and DAC B on, IF = 5.1 MHz, first Nyquist zone < $f_{DATA}/2$                                |                   | 77   |     | dBc  |

|                      |                                                                    | X4, CLK2 = 500 MHz, DAC A and DAC B on,<br>IF = 20.1 MHz, PLL on for MIN, PLL off for TYP,<br>first Nyquist zone < $f_{DATA}/2$ | 68 <sup>(3)</sup> | 76   |     |      |

|                      | Signal-to-noise ratio                                              | X4, PLL off, CLK2 = 500 MSPS, DAC A and DAC B on, single tone, 0 dBFS, IF = 20.1 MHz                                            |                   | 73   |     | dBc  |

|                      |                                                                    | X4 CMIX, PLL off, CLK2 = 500 MSPS, DAC A and DAC B on, IF = 70.1 MHz                                                            |                   | 65   |     |      |

| SNR                  |                                                                    | X4 CMIX, PLL off, CLK2 = 500 MSPS, DAC A and DAC B on, single tone, 0 dBFS, IF = 150.1 MHz                                      |                   | 57   |     |      |

|                      |                                                                    | X4 FMIX CMIX, PLL off, CLK2 = 500 MSPS, DAC A and DAC B on, single tone, 0 dBFS, IF = 180.1 MHz                                 |                   | 54   |     |      |

|                      |                                                                    | X4, PLL off, CLK2 = 500 MSPS, DAC A and DAC B on,<br>four tones, each –12 dBFS, IF = 24.7, 24.9, 25.1, 25.3<br>MHz              |                   | 73   |     |      |

|                      |                                                                    | X4, PLL off, CLK2 = 500 MSPS, DAC A and DAC B on,<br>IF = 20.1 and 21.1 MHz                                                     |                   | 79   |     |      |

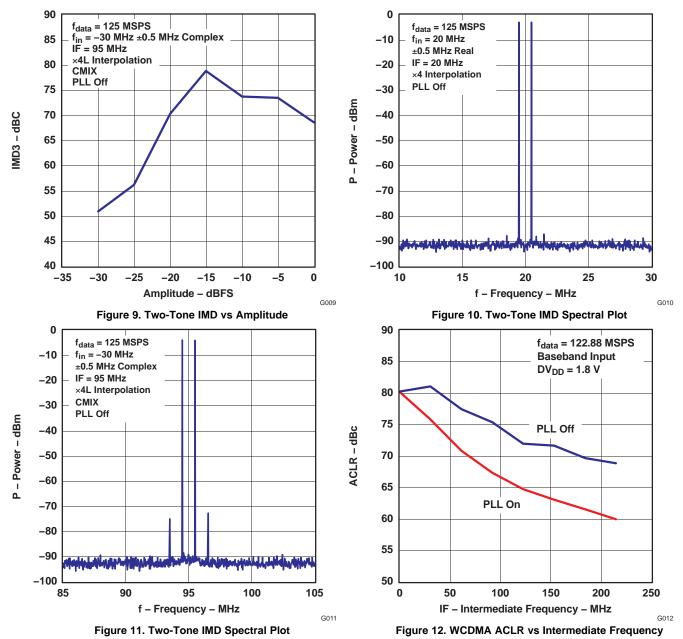

|                      | Third-order two-tone                                               | X4 CMIX, PLL off, CLK2 = 500 MSPS, DAC A and DAC B on, IF = 70.1 and 71.1 MHz                                                   |                   | 73   |     |      |

| IMD3                 | intermodulation (each tone at<br>–6 dBFS)                          | X4 CMIX, PLL off, CLK2 = 500 MSPS, DAC A and DAC B on, IF= 150.1 and 151.1 MHz                                                  |                   | 68   |     | dBc  |

|                      |                                                                    | X4 FMIX CMIX, PLL off, CLK2 = 500 MSPS, DAC A and DAC B on, IF = 180.1 and 181.1 MHz                                            |                   | 67   |     |      |

| IMD                  | Four-tone intermodulation to<br>Nyquist (each tone at –12<br>dBFS) | X4 CMIX, CLK2 = 500 MHz, f <sub>OUT</sub> = 149.2, 149.6, 150.4, and 150.8 MHz                                                  |                   | 66   |     | dBc  |

(1) Measured single ended into  $50-\Omega$  load.

(2) See the Non-Harmonic Clock Related Spurious Signals section for information on spurious products out of band (< f<sub>DATA</sub>/2).

(3) 1:1 transformer output termination.

## **ELECTRICAL CHARACTERISTICS (AC SPECIFICATIONS) (continued)**

over recommended operating free-air temperature range, AVDD = 3.3 V, CLKVDD = 3.3 V, PLLVDD = 0 V (= 3.3 V for PLL clock mode), IOVDD = 3.3 V, DVDD = 1.8 V, IOUT<sub>FS</sub> = 19.2 mA, external clock mode, 4:1 transformer output termination,  $50-\Omega$  doubly terminated load (unless otherwise noted)

|                      | PARAMETER                      | TEST CONDITIONS                                                                                  | MIN TYP MAX | UNIT |

|----------------------|--------------------------------|--------------------------------------------------------------------------------------------------|-------------|------|

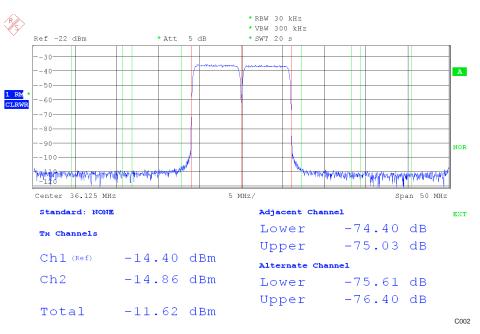

|                      |                                | Single carrier, baseband, X4, PLL clock mode, CLK1 = 122.88 MHz                                  | 78.4        |      |

|                      |                                | Single carrier, baseband, X4, PLL clock mode, CLK2 = 491.52 MHz                                  | 78.5        |      |

|                      |                                | Single carrier, IF = 153.6 MHz, X4 CMIX, external clock mode, CLK2 = 491.52 MHz                  | 70.9        |      |

|                      |                                | Two carrier, IF = 153.6 MHz, X4 CMIX, external clock mode, CLK2 = 491.52 MHz                     | 67.8        |      |

| ACI R <sup>(4)</sup> | Adiacent channel lackage ratio | Four carrier, baseband, X4, external clock mode,<br>CLK2 = 491.52 MHz                            | 76.1        | dBc  |

| ACLR                 | Adjacent channel leakage ratio | Four carrier, IF = 92.16 MHz, X4L, external clock mode, CLK2 = 491.52 MHz                        | 66.8        | uвс  |

|                      |                                | Single carrier, IF = 153.6 MHz, X4 CMIX, external clock mode, CLK2 = 491.52 MHz, DVDD = 2.1 V    | 72.2        |      |

|                      |                                | Two carrier, IF = 153.6 MHz, X4 CMIX, external clock mode, CLK2 = 491.52 MHz, DVDD = 2.1 V       | 69.3        |      |

|                      |                                | Four carrier, baseband, X4, external clock mode,<br>CLK2 = 491.52 MHz, DVDD = 2.1 V              | 68.5        |      |

|                      |                                | Four carrier, IF = 92.16 MHz, X4L, external clock mode,<br>CLK2 = 491.52 MHz, DVDD = 2.1 V       | 66.3        |      |

|                      |                                | 50-MHz offset, 1-MHz BW, single carrier, baseband,<br>X4, external clock mode, CLK2 = 491.52 MHz | 92          |      |

|                      | Noise floor                    | 50-MHz offset, 1-MHz BW, four carrier, baseband, X4, external clock mode, CLK2 = 491.52 MHz      | 81          | 10   |

|                      |                                | 50-MHz offset, 1-MHz BW, single carrier, baseband,<br>X4, PLL clock mode, CLK1 = 122.88 MHz      | 88          | dBc  |

|                      |                                | 50-MHz offset, 1-MHz BW, four carrier, baseband,<br>X4, PLL clock mode, CLK1 = 122.88 MHz        | 81          |      |

(4) W-CDMA with 3.84-MHz BW, 5-MHz spacing, centered at IF. TESTMODEL 1, 10 ms

## **ELECTRICAL CHARACTERISTICS (DIGITAL SPECIFICATIONS)**

over recommended operating free-air temperature range, AVDD = 3.3 V, CLKVDD = 3.3 V, PLLVDD = 3.3 V, IOVDD =  $3.3 \text{$

|                 | PARAMETER                | TEST CONDITIONS              | MIN         | TYP | MAX      | UNIT |

|-----------------|--------------------------|------------------------------|-------------|-----|----------|------|

| CMOS I          | NTERFACE                 | I                            | ł           |     | 1        |      |

| V <sub>IH</sub> | High-level input voltage |                              | 2           | 3   |          | V    |

| VIL             | Low-level input voltage  |                              | 0           | 0   | 0.8      | V    |

| V <sub>IH</sub> | High-level input voltage | IOVDD = 1.8 V                | 1.26        |     |          | V    |

| VIL             | Low-level input voltage  | IOVDD = 1.8 V                |             |     | 0.54     | V    |

| I <sub>IH</sub> | High-level input current |                              | -40         |     | 40       | μA   |

| IIL             | Low-level input current  |                              | -40         |     | 40       | μΑ   |

|                 | Input capacitance        |                              |             | 5   |          | pF   |

| N/              |                          | $I_{load} = -100 \ \mu A$    | IOVDD - 0.2 |     |          |      |

| V <sub>OH</sub> | PLLLOCK, SDO, SDIO       | I <sub>load</sub> = -8 mA    | 0.8 IOVDD   |     |          | V    |

| N/              |                          | I <sub>load</sub> = 100 μA   |             |     | 0.2      | V    |

| V <sub>OL</sub> | PLLLOCK, SDO, SDIO       | I <sub>load</sub> = 8 mA     |             | 0.  | 22 IOVDD | v    |

|                 |                          | External or dual-clock modes | 0           |     | 250      | MODO |

|                 | Input data rate          | PLL clock mode               | 2.5         |     | 160      | MSPS |

## ELECTRICAL CHARACTERISTICS (DIGITAL SPECIFICATIONS) (continued)

over recommended operating free-air temperature range, AVDD = 3.3 V, CLKVDD = 3.3 V, PLLVDD = 3.3 V, IOVDD = 3.3 V, DVDD = 1.8 V, IOUT<sub>FS</sub> = 19.2 mA (unless otherwise noted)

|                             | PARAMETER                                                                                    | TEST CONDITIONS                                                                                                                                | MIN             | TYP MAX                     | UNIT    |

|-----------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------|---------|

| PLL                         |                                                                                              |                                                                                                                                                |                 |                             |         |

|                             | Phase noise                                                                                  | At 600-kHz offset, measured at DAC output,<br>25-MHz, 0-dBFS tone, f <sub>DATA</sub> = 125 MSPS,<br>4× interpolation, pll_freq = 1, pll_kv = 0 |                 | 133                         | dBc/Hz  |

|                             | Filase huise                                                                                 | At 6-MHz offset, measured at DAC output,<br>25 MHz 0-dBFS tone, 125 MSPS,<br>4× interpolation, pll_freq = 1, pll_kv = 0                        |                 | 148.5                       | UDC/112 |

|                             |                                                                                              | pll_freq = 0, pll_kv = 1                                                                                                                       | 370             |                             |         |

|                             | VCO maximum frequency                                                                        | pll_freq = 0, pll_kv = 0                                                                                                                       | 480             |                             | MHz     |

|                             | VCO maximum requency                                                                         | pll_freq = 1, pll_kv = 1                                                                                                                       | 495             |                             | IVII 12 |

|                             |                                                                                              | pll_freq = 1, pll_kv = 0                                                                                                                       | 520             |                             |         |

|                             |                                                                                              | pll_freq = 0, pll_kv = 1                                                                                                                       |                 | 225                         |         |

|                             |                                                                                              | $pll_freq = 0, pll_kv = 0$                                                                                                                     |                 | 200                         | MHz     |

|                             | VCO minimum frequency                                                                        | pll_freq = 1, pll_kv = 1                                                                                                                       |                 | 480                         |         |

|                             |                                                                                              | pll_freq = 1, pll_kv = 0                                                                                                                       |                 | 480                         |         |

| NCO and Q                   | MC BLOCKS                                                                                    |                                                                                                                                                |                 |                             |         |

|                             | QMC clock rate                                                                               |                                                                                                                                                |                 | 320                         | MHz     |

|                             | NCO clock rate                                                                               |                                                                                                                                                |                 | 320                         | MHz     |

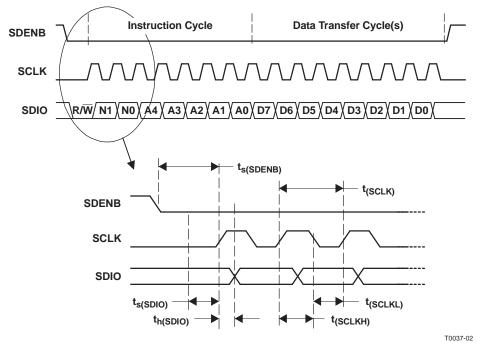

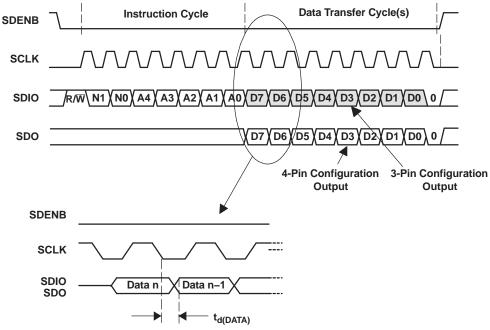

| SERIAL PO                   | RT TIMING                                                                                    |                                                                                                                                                |                 |                             |         |

| t <sub>s(SDENB)</sub>       | Setup time, SDENB to rising edge of SCLK                                                     |                                                                                                                                                | 20              |                             | ns      |

| t <sub>s(SDIO)</sub>        | Setup time, SDIO valid to rising edge of SCLK                                                |                                                                                                                                                | 10              |                             | ns      |

| t <sub>h(SDIO)</sub>        | Hold time, SDIO valid to rising edge of SCLK                                                 |                                                                                                                                                | 5               |                             | ns      |

| t <sub>SCLK</sub>           | Period of SCLK                                                                               |                                                                                                                                                | 100             |                             | ns      |

| t <sub>SCLKH</sub>          | High time of SCLK                                                                            |                                                                                                                                                | 40              |                             | ns      |

| t <sub>SCLK</sub>           | Low time of SCLK                                                                             |                                                                                                                                                | 40              |                             | ns      |

| t <sub>d(Data)</sub>        | Data output delay after falling edge of SCLK                                                 |                                                                                                                                                |                 | 10                          | ns      |

| CLOCK INF                   | PUT (CLK1/CLK1C, CLK2/CLK2C)                                                                 |                                                                                                                                                |                 |                             | -       |

|                             | Duty cycle                                                                                   |                                                                                                                                                | 40%             | 60%                         |         |

|                             | Differential voltage                                                                         |                                                                                                                                                | 0.4             | 1                           | V       |

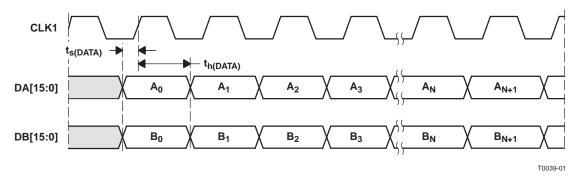

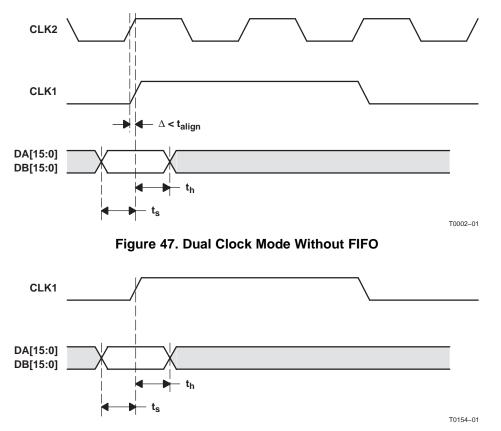

|                             | RALLEL DATA INPUT: CLK1 LATCHING MO<br>– See Figure 45, Dual Clock Mode FIFO Disa            | DES<br>abled – See Figure 47, Dual Clock Mode With Fl                                                                                          | FO Enabled – Se | e Figure 48)                | 1       |

| t <sub>s(DATA)</sub>        | Setup time, DATA valid to rising edge of CLK1                                                |                                                                                                                                                | 0.5             |                             | ns      |

| t <sub>h(DATA)</sub>        | Hold time, DATA valid after rising edge of<br>CLK1                                           |                                                                                                                                                | 1.5             |                             | ns      |

| t_align                     | Maximum offset between CLK1 and CLK2<br>rising edges – dual clock mode with FIFO<br>disabled |                                                                                                                                                |                 | $\frac{1}{2f_{CLK2}} - 0.5$ | ns      |

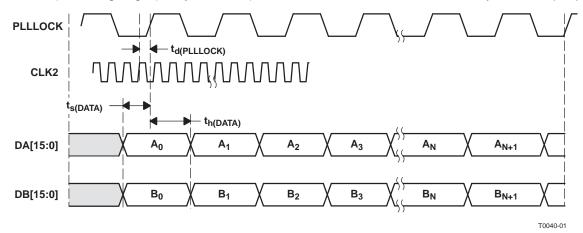

| Timing Par                  |                                                                                              | on PLLLOCK Rising Edge, CLK2 Clock Input,                                                                                                      | See Figure 43 ) |                             | 1       |

| t <sub>s(DATA)</sub>        | Setup time, DATA valid to rising edge of<br>PLLLOCK                                          | 72-Ω load on PLLLOCK                                                                                                                           | 0.5             |                             | ns      |

| t <sub>h(DATA)</sub>        | Hold time, DATA valid after rising edge of<br>PLLLOCK                                        | 72-Ω load on PLLLOCK                                                                                                                           | 1.5             |                             | ns      |

| t <sub>delay(Plllock)</sub> | Delay from CLK2 rising edge to PLLLOCK<br>rising edge                                        | $72-\Omega$ load on PLLLOCK. Note that PLLLOCK delay increases with a lower-impedance load.                                                    |                 | 4.5                         | ns      |

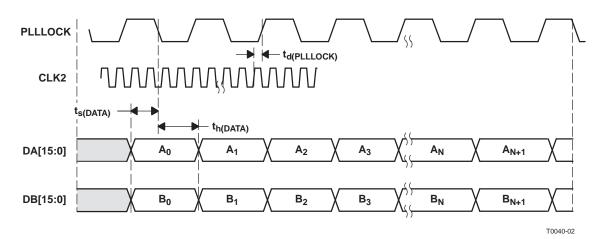

| Timing Par                  | allel Data Input (External Clock Mode, Latch                                                 | on PLLLOCK Falling Edge, CLK2 Clock Input,                                                                                                     | See Figure 44)  |                             |         |

| t <sub>s(DATA)</sub>        | Setup time, DATA valid to falling edge of<br>PLLLOCK                                         | High-impedance load on PLLLOCK                                                                                                                 | 0.5             |                             | ns      |

| t <sub>h(DATA)</sub>        | Hold time, DATA valid after falling edge of<br>PLLLOCK                                       | High-impedance load on PLLLOCK                                                                                                                 | 1.5             |                             | ns      |

| t <sub>delay(Plllock)</sub> | Delay from CLK2 rising edge to PLLLOCK<br>rising edge                                        | High-impedance load on PLLLOCK. Note that<br>PLLLOCK delay increases with a                                                                    |                 | 4.5                         | ns      |

TRUMENTS www.ti.com

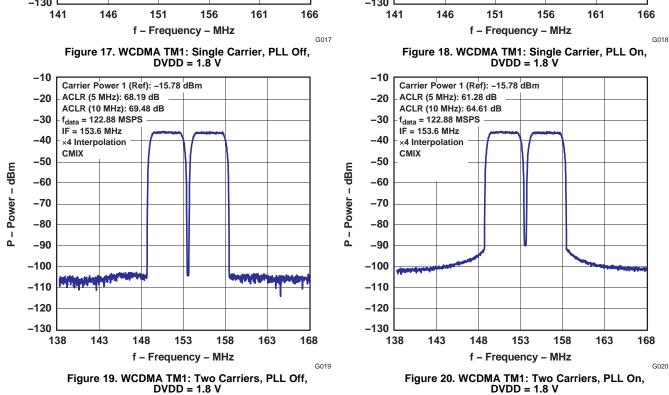

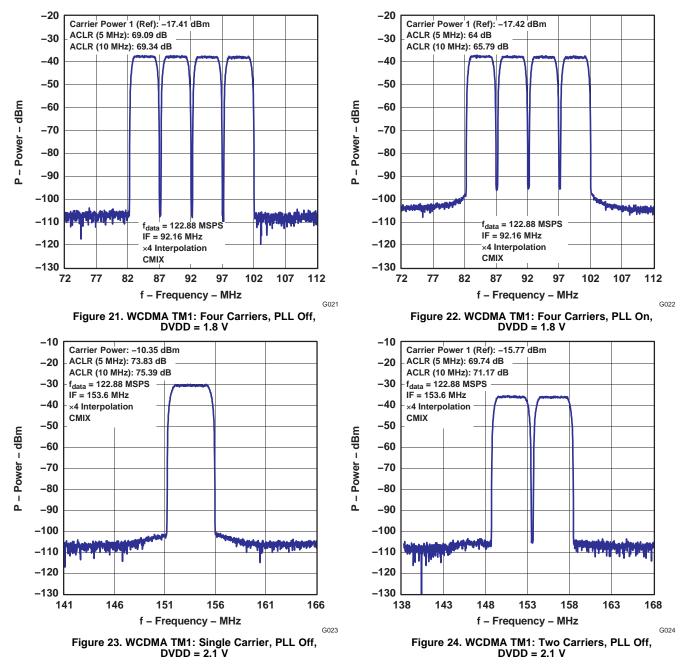

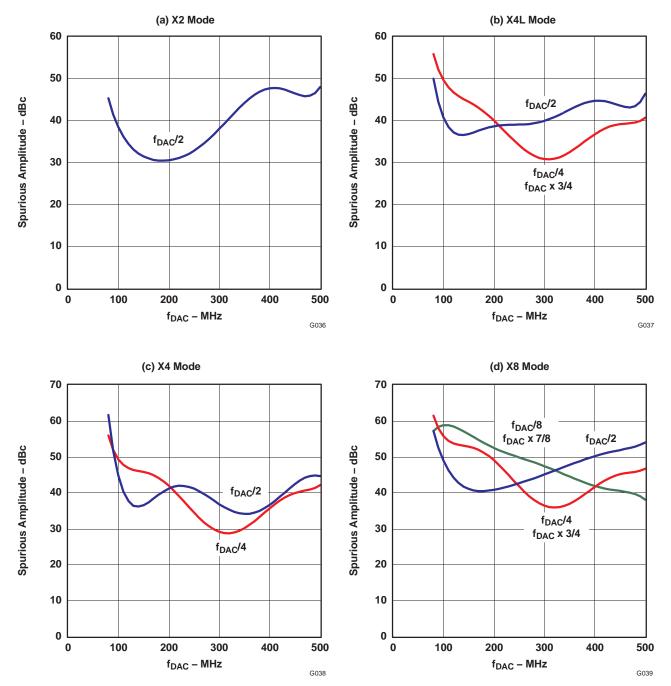

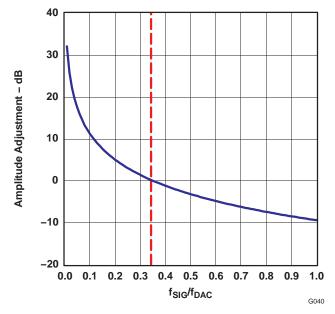

## **Typical Characteristics (continued)**

IEXAS

www.ti.com

#### SLWS164E-FEBRUARY 2005-REVISED SEPTEMBER 2006

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

### **Typical Characteristics (continued)**

IEXAS FRUMENTS

P - Power - dBm

## **Typical Characteristics (continued)**

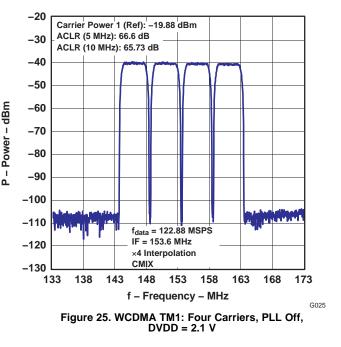

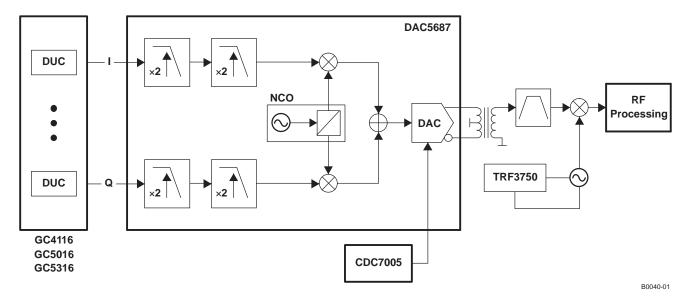

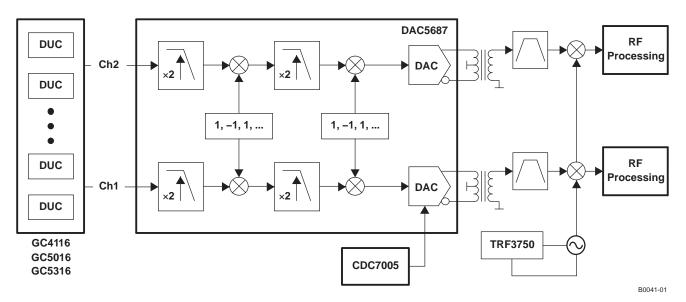

## **Test Methodology**

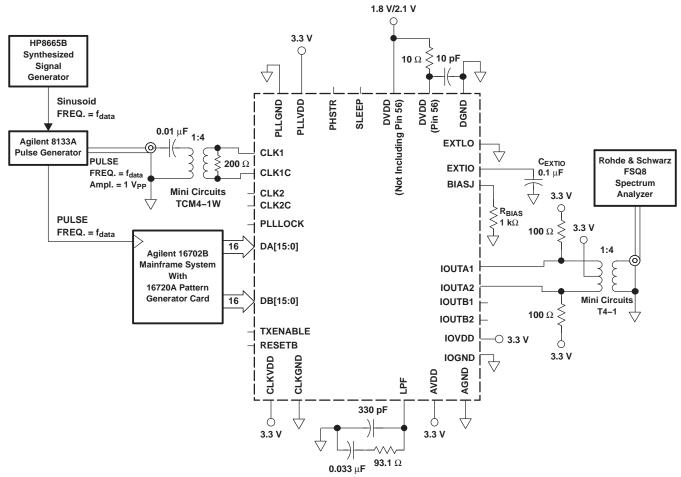

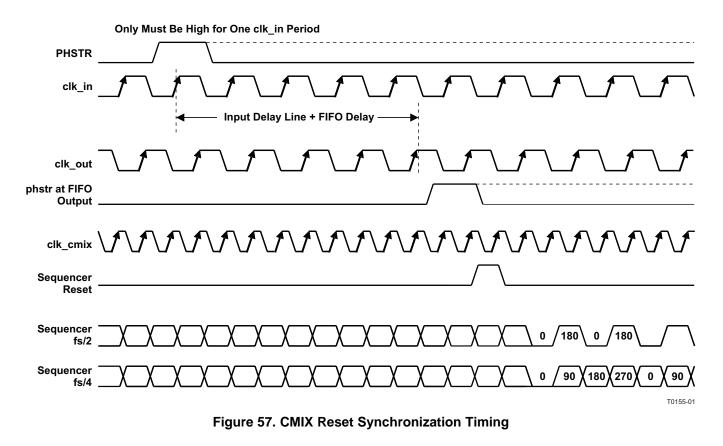

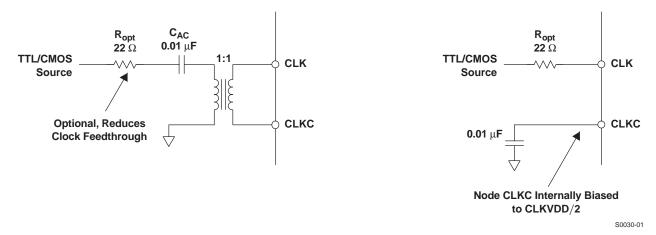

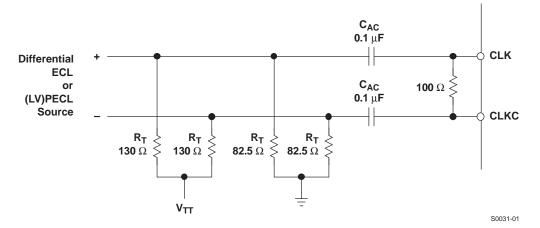

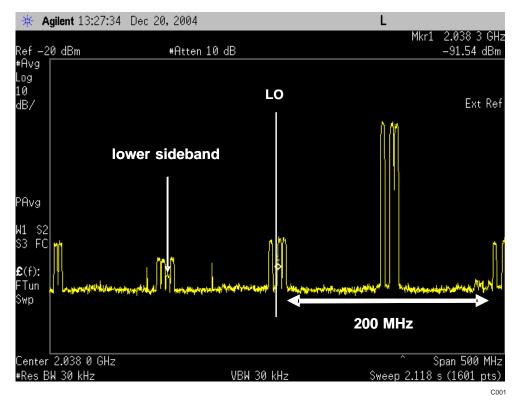

Typical ac specifications in external clock mode were characterized with the DAC5687EVM using the test configuration shown in Figure 26. The DAC sample-rate clock  $f_{DAC}$  is generated by an HP8665B signal generator. An Agilent 8133A pulse generator is used to divide  $f_{DAC}$  for the data-rate clock  $f_{DATA}$  for the Agilent 16702A pattern-generator clock and provide adjustable skew to the DAC input clock. The 8133A  $f_{DAC}$  output is set to 1 V<sub>PP</sub>, equivalent to 2-V<sub>PP</sub> differential at CLK2/CLK2C pins. Alternatively, the DAC5687 PLLLOCK output can be used for the pattern generator clock.

The DAC5687 output is characterized with a Rohde & Schwarz FSQ8 spectrum analyzer. For WCDMA signal characterization, it is important to use a spectrum analyzer with high IP3 and noise subtraction capability so that the spectrum analyzer does not limit the ACPR measurement. For all specifications, both DACA and DACB are measured and the lowest value used as the specification.

B0039-01

Figure 26. DAC5687 Test Configuration for External Clock Mode

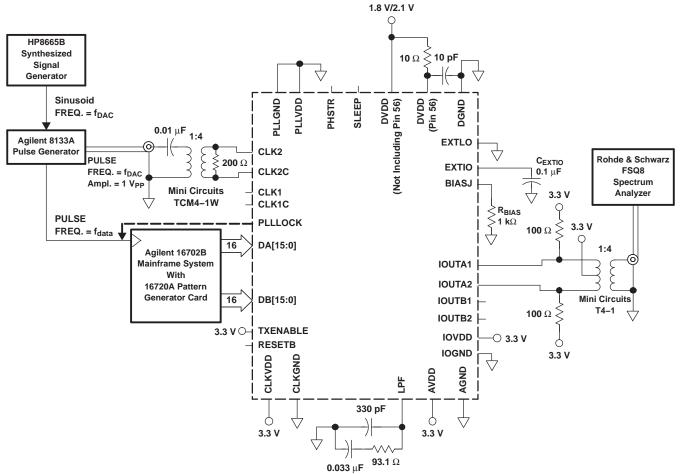

PLL clock mode was characterized using the test configuration shown in Figure 27. The DAC data rate clock  $f_{DATA}$  is generated by an HP8665B signal generator. An Agilent 8133A pulse generator is used to generate a clock  $f_{DATA}$  for the Agilent 16702A pattern-generator clock and provide adjustable skew to the DAC input clock. The 8133A  $f_{DAC}$  output is set to 1 V<sub>PP</sub>, equivalent to 2-V<sub>PP</sub> differential at CLK1/CLK1C pins. Alternatively, the DAC5687 PLLLOCK output can be used for the pattern-generator clock.

B0039-02

Figure 27. DAC5687 Test Configuration for PLL Clock Mode

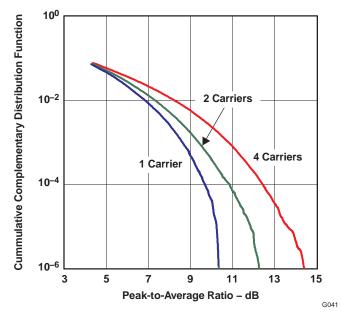

WCDMA test-model-1 test vectors for the DAC5687 characterization were generated in accordance with the 3GPP Technical Specification. Chip-rate data was generated using the test-model-1 block in the Agilent ADS. For multicarrier signals, different random seeds and PN offsets were used for each carrier. A Matlab<sup>™</sup> script performed pulse shaping, interpolation to the DAC input data rate, frequency offsets, rounding, and scaling. Each test vector is 10 ms long, representing one frame. Special care is taken to assure that the end of the file wraps smoothly to the beginning of the file.

The cumulative complementary distribution function (CCDF) for the 1-, 2-, and 4-carrier test vectors is shown in Figure 28. The test vectors are scaled such that the absolute maximum data point is 0.95 (–0.45 dB) of full scale. No peak reduction is used.

## DETAILED DESCRIPTION

#### Modes of Operation

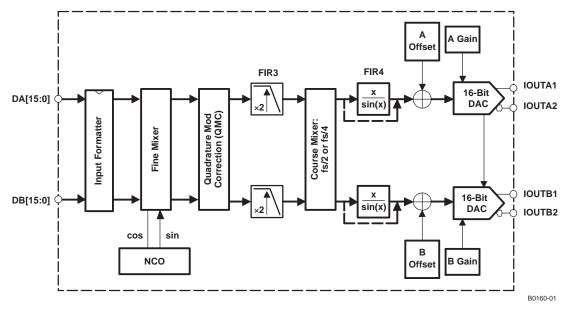

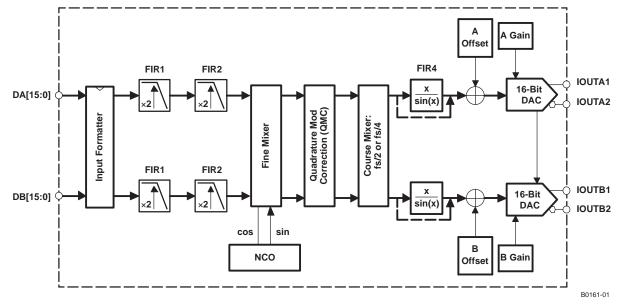

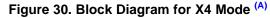

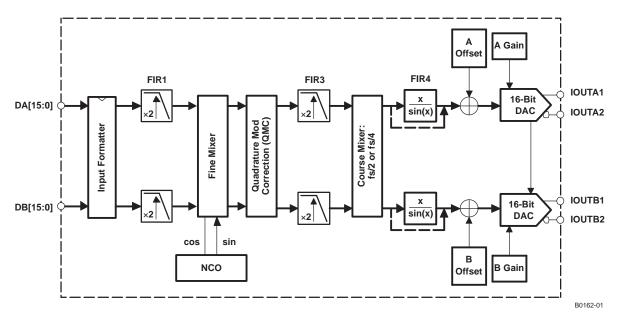

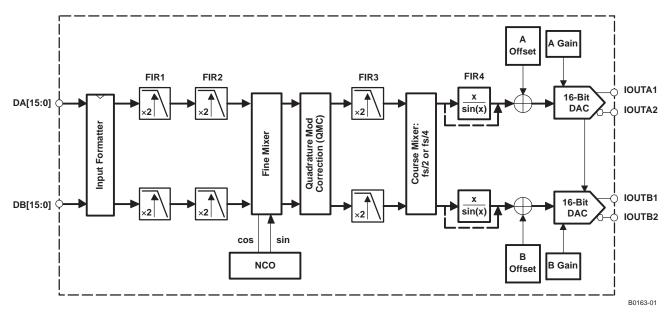

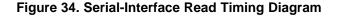

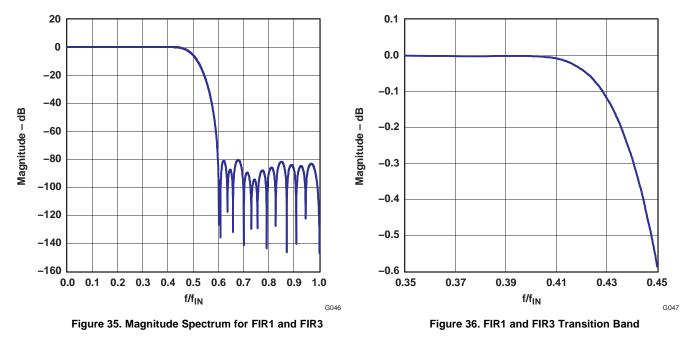

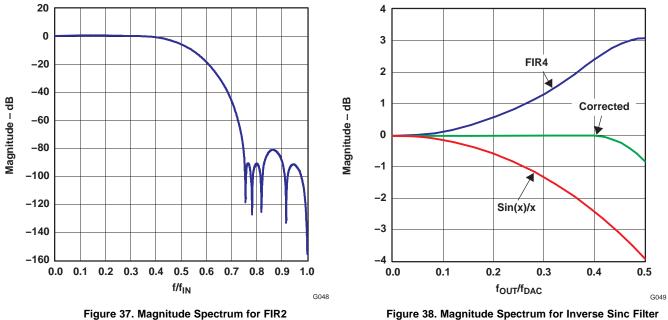

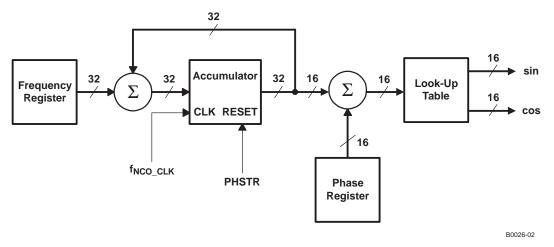

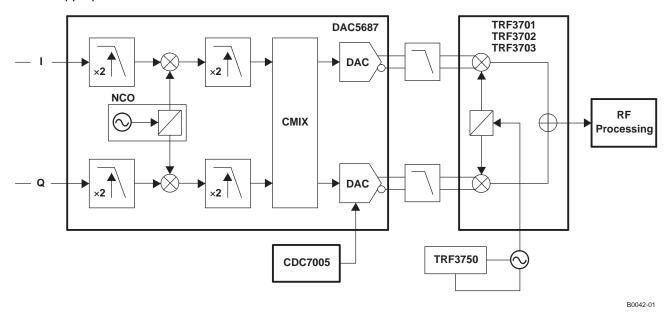

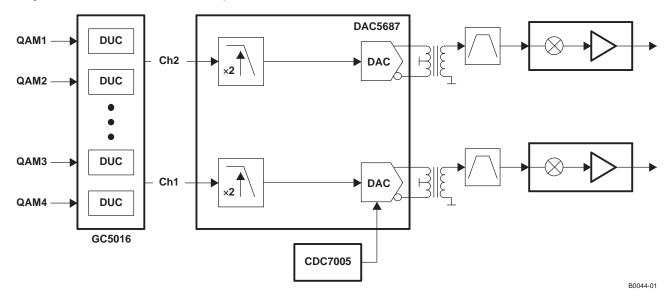

The DAC5687 has six digital signal processing blocks: FIR1 and FIR2 (interpolate-by-two digital filters), FMIX (fine frequency mixer), QMC (quadrature modulation phase correction), FIR3 (interpolate-by-two digital filter) and CMIX (coarse frequency mixer). The modes of operation, listed in Table 1, enable or bypass the blocks to produce different results. The modes are selected by registers CONFIG1, CONFIG2, and CONFIG3 (0x02, 0x03, and 0x04). Block diagrams for each mode (X2, X4, X4L, and X8) are shown in Figure 29 through Figure 32.

| MODE                   | FIR1 | FIR2 | FMIX | QMC               | FIR3 | CMIX |

|------------------------|------|------|------|-------------------|------|------|

| FULL BYPASS            | -    | -    | -    | -                 | -    | -    |

| X2                     | -    | -    | -    | -                 | ON   | -    |

| X2 FMIX                | -    | -    | ON   | -                 | ON   | -    |

| X2 QMC                 | -    | -    | -    | ON                | ON   | _    |

| X2 FMIX QMC            | -    | -    | ON   | ON                | ON   | -    |

| X2 CMIX                | -    | -    | -    | -                 | ON   | ON   |

| X2 FMIX CMIX           | -    | -    | ON   | -                 | ON   | ON   |

| X2 QMC CMIX            | -    | -    | -    | ON <sup>(1)</sup> | ON   | ON   |

| X2 FMIX QMC CMIX       | -    | -    | ON   | ON <sup>(1)</sup> | ON   | ON   |

| X4                     | ON   | ON   | -    | -                 | -    | -    |

| X4 FMIX <sup>(2)</sup> | ON   | ON   | ON   | -                 | _    | _    |

| X4 QMC <sup>(2)</sup>  | ON   | ON   | -    | ON                | -    | -    |

| X4 FMIX QMC            | ON   | ON   | ON   | ON                | -    | -    |

| X4 CMIX                | ON   | ON   | -    | -                 | -    | ON   |

| X4L                    | ON   | -    | -    | -                 | ON   | -    |

#### Table 1. DAC5687 Modes of Operation

(1) The QMC phase correction is eliminated by the CMIX, so the QMC phase should be set to zero. The QMC gain settings can still be used to adjust the signal path gain as needed.

f<sub>DAC</sub> limited to maximum clock rate for the NCO and QMC (see Electrical Characteristics (AC Specifications)).

(2)

20

| Table 1. DACS007 Modes of Operation (continued) |      |      |      |                   |      |      |  |  |  |

|-------------------------------------------------|------|------|------|-------------------|------|------|--|--|--|

| MODE                                            | FIR1 | FIR2 | FMIX | QMC               | FIR3 | CMIX |  |  |  |

| X4L FMIX                                        | ON   | -    | ON   | -                 | ON   | -    |  |  |  |

| X4L QMC                                         | ON   | -    | -    | ON                | ON   | -    |  |  |  |

| X4L FMIX QMC                                    | ON   | -    | ON   | ON                | ON   | -    |  |  |  |

| X4L CMIX                                        | ON   | -    | -    | -                 | ON   | ON   |  |  |  |

| X4L FMIX CMIX                                   | ON   | -    | ON   |                   | ON   | ON   |  |  |  |

| X4L QMC CMIX                                    | ON   | _    | -    | ON <sup>(2)</sup> | ON   | ON   |  |  |  |

| X4L FMIX QMC CMIX                               | ON   | _    | ON   | ON <sup>(2)</sup> | ON   | ON   |  |  |  |

| X8                                              | ON   | ON   | -    | -                 | ON   | -    |  |  |  |

| X8 FMIX                                         | ON   | ON   | ON   | -                 | ON   | -    |  |  |  |

| X8 QMC                                          | ON   | ON   | -    | ON                | ON   | -    |  |  |  |

| X8 FMIX QMC                                     | ON   | ON   | ON   | ON                | ON   | -    |  |  |  |

| X8 CMIX                                         | ON   | ON   | -    | _                 | ON   | ON   |  |  |  |

| X8 FMIX CMIX                                    | ON   | ON   | ON   | -                 | ON   | ON   |  |  |  |

| X8 QMC CMIX                                     | ON   | ON   | -    | ON <sup>(1)</sup> | ON   | ON   |  |  |  |

| X8 FMIX QMC CMIX                                | ON   | ON   | ON   | ON <sup>(1)</sup> | ON   | ON   |  |  |  |

#### Table 1. DAC5687 Modes of Operation (continued)

Figure 29. Block Diagram for X2 Mode

A. FMIX or QMC block cannot be enabled with CMIX block.

Figure 31. Block Diagram for X4L Mode

Figure 32. Block Diagram for X8 Mode

## **Programming Registers**

| Name             | Address | Default | Bit 7<br>(MSB)                             | Bit 6            | Bit 5         | Bit 4        | Bit 3        | Bit 2    | Bit 1        | Bit 0<br>(LSB)   |

|------------------|---------|---------|--------------------------------------------|------------------|---------------|--------------|--------------|----------|--------------|------------------|

| VERSION          | 0x00    | 0x03    | sleep_daca                                 | sleep_dacb       | hpla          | hplb         | unused       |          | version(     | (2:0)            |

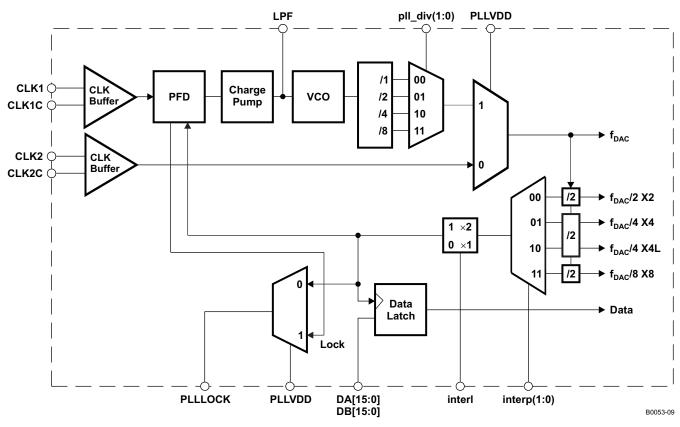

| CONFIG0          | 0x01    | 0x00    | pll_div                                    | /(1:0)           | pll_freq      | pll_kv       | interp(      | 1:0)     | inv_plllock  | fifo_bypass      |

| CONFIG1          | 0x02    | 0x00    | qflag                                      | interl           | dual_clk      | twos         | rev_abus     | rev_bbus | fir_bypass   | full_bypass      |

| CONFIG2          | 0x03    | 0x80    | nco                                        | nco_gain         | qmc           |              | cm_mo        | de(3:0)  |              | invsinc          |

| CONFIG3          | 0x04    | 0x00    | sif_4pin                                   | dac_ser_dat<br>a | half_rate     | unused       | usb          |          | counter_mo   | ode(2:0)         |

| SYNC_CNTL        | 0x05    | 0x00    | sync_phstr sync_nco sync_cm sync_fifo(2:0) |                  |               |              | unused       | unused   |              |                  |

| SER_DATA_0       | 0x06    | 0x00    |                                            | dac_data(7:0)    |               |              |              |          |              |                  |

| SER_DATA_1       | 0x07    | 0x00    |                                            |                  |               | dac_         | data(15:8)   |          |              |                  |

| Factory use only | 0x08    | 0x00    |                                            |                  |               |              |              |          |              |                  |

| NCO_FREQ_0       | 0x09    | 0x00    |                                            | freq(7:0)        |               |              |              |          |              |                  |

| NCO_FREQ_1       | 0x0A    | 0x00    |                                            |                  |               | fre          | eq(15:8)     |          |              |                  |

| NCO_FREQ_2       | 0x0B    | 0x00    |                                            | freq(23:16)      |               |              |              |          |              |                  |

| NCO_FREQ_3       | 0x0C    | 0x40    |                                            | freq(31:24)      |               |              |              |          |              |                  |

| NCO_PHASE_0      | 0x0D    | 0x00    |                                            | phase(7:0)       |               |              |              |          |              |                  |

| NCO_PHASE_1      | 0x0E    | 0x00    |                                            | phase(15:8)      |               |              |              |          |              |                  |

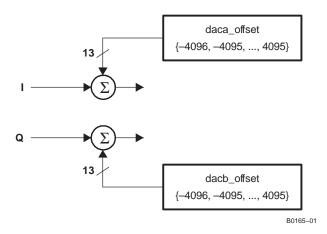

| DACA_OFFSET_0    | 0x0F    | 0x00    |                                            | daca_offset(7:0) |               |              |              |          |              |                  |

| DACB_OFFSET_0    | 0x10    | 0x00    |                                            |                  |               | dacb_        | _offset(7:0) |          |              |                  |

| DACA_OFFSET_1    | 0x11    | 0x00    |                                            | daca             | _offset(12:8) |              |              | unused   | unused       | unused           |

| DACB_OFFSET_1    | 0x12    | 0x00    |                                            | dacb             | _offset(12:8) |              |              | unused   | unused       | unused           |

| QMCA_GAIN_0      | 0x13    | 0x00    |                                            |                  |               | qmc_         | gain_a(7:0)  |          |              |                  |

| QMCB_GAIN_0      | 0x14    | 0x00    |                                            |                  |               | qmc_         | gain_b(7:0)  |          |              |                  |

| QMC_PHASE_0      | 0x15    | 0x00    |                                            |                  |               | qmc_         | phase(7:0)   |          |              |                  |

| QMC_PHASE_GAIN_1 | 0x16    | 0x00    | qmc_pha                                    | ase(9:8)         | qn            | nc_gain_a(1  | 10:8)        |          | qmc_gain_    | b(10:8)          |

| DACA_GAIN_0      | 0x17    | 0x00    |                                            |                  |               | daca         | _gain(7:0)   |          |              |                  |

| DACB_GAIN_0      | 0x18    | 0x00    |                                            |                  |               | dacb         | _gain(7:0)   |          |              |                  |

| DACA_DACB_GAIN_1 | 0x19    | 0xFF    |                                            | daca_gain(       | 11:8)         |              |              | dact     | o_gain(11:8) |                  |

| Factory use only | 0x1A    | 0x00    |                                            |                  |               |              |              |          |              |                  |

| ATEST            | 0x1B    | 0x00    |                                            | a                | atest(4:0)    |              | ·            | phstr_   | del(1:0)     | unused           |

| DAC_TEST         | 0x1C    | 0x00    |                                            |                  | facto         | ory use only |              |          |              | phstr_clkdiv_sel |

| Factory use only | 0x1D    | 0x00    |                                            |                  |               |              |              |          |              |                  |

| Factory use only | 0x1E    | 0x00    |                                            |                  |               |              |              |          |              |                  |

| Factory use only | 0x1F    | 0x00    |                                            |                  |               |              |              |          |              |                  |

**REGISTER MAP**

## Register Name: VERSION—Address: 0x00, Default = 0x03 BIT 7

| DIT | 0 |

|-----|---|

| ווס | U |

|     |   |

| sleep_daca | sleep_dacb | hpla | hplb | unused | version(2:0) |   |   |

|------------|------------|------|------|--------|--------------|---|---|

| 0          | 0          | 0    | 0    | 0      | 0            | 1 | 1 |

sleep\_daca: DAC A sleeps when set, operational when cleared.

**sleep\_dacb:** DAC B sleeps when set, operational when cleared.

hpla: A-side first FIR filter in high-pass mode when set, low-pass mode when cleared.

hplb: B-side first FIR filter in high-pass mode when set, low-pass mode when cleared.

version(2:0): A hardwired register that contains the version of the chip. Read-only.

#### Register Name: CONFIG0—Address: 0x01, Default = 0x00

BIT 7

FXAS *IRUMENTS* vww.ti.com

| pll_di | v(1:0) | pll_freq | pll_kv | interp(1:0) |   | inv_plllock | fifo_bypass |

|--------|--------|----------|--------|-------------|---|-------------|-------------|

| 0      | 0      | 0        | 0      | 0           | 0 | 0           | 0           |

**pll div(1:0):** PLL VCO divider;  $\{00 = 1, 01 = 2, 10 = 4, 11 = 8\}$ .

**pll freq:** PLL VCO center frequency; {0 = low center frequency, 1 = high center frequency}.

**pll\_kv:** PLL VCO gain; {0 = high gain, 1 = low gain}.

interp(1:0): FIR interpolation;  $\{00 = X2, 01 = X4, 10 = X4L, 11 = X8\}$ . X4 uses lower power than X4L, but  $f_{DAC} =$ 320 MHz maximum when NCO or QMC is used.

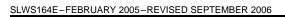

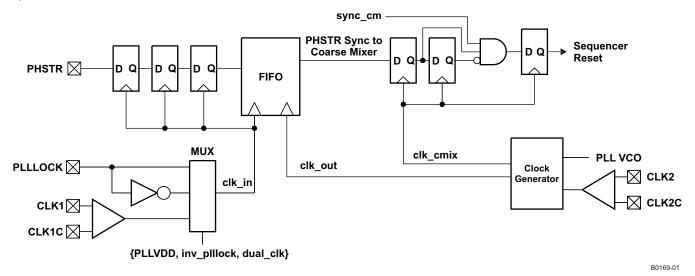

inv\_plllock: Multifunction bit, depending on clock mode

fifo\_bypass: When set, the internal four-sample FIFO is disabled. When cleared, the FIFO is enabled.