# AUDIO DSP WITH ANALOG INTERFACE

Check for Samples: TAS3204

#### Introduction 1

- 1.1 Features

- Digital Audio Processor

- Fully Programmable With the Graphical, Drag-and-Drop PurePath Studio™ Software Development Environment

- 135-MHz Operation

- 48-Bit Data Path With 76-Bit Accumulator

- Hardware Single-Cycle Multiplier (28 × 48)

- Five Simultaneous Operations Per Clock Cycle

- Usable 768 Words Data RAM (48 Bit), Usable 1k Coefficient RAM (28 Bit)

- Usable 2.5K Program RAM

- 122 ms at 48 kHz, 5.8k Words 24-Bit Delay Memory

- Slave Mode F<sub>s</sub> is 44.1 kHz and 48 kHz

- Master Mode F<sub>s</sub> is 48 kHz

- Analog Audio Input/Output

- Two 3:1 Stereo Analog Input MUXes

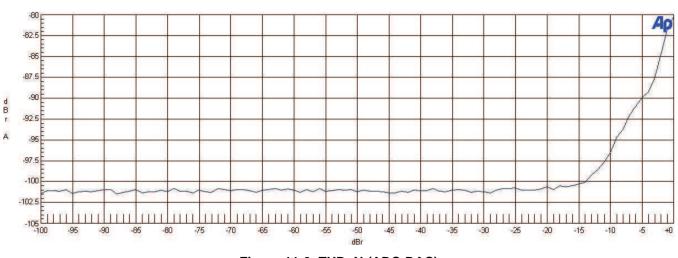

- Four Differential ADCs (102 dB DNR, Typical)

- Four Differential DACs (105 dB DNR, Typical)

- Digital Audio Input/Output

- Two Synchronous Serial Audio Inputs (Four Channels)

- Two Synchronous Serial Audio Outputs (Four Channels)

- Input and Output Data Formats: 16-, 20-, or 24-Bit Data Left, Right, and I<sup>2</sup>S

- System Control Processor

- Embedded 8051 WARP Microprocessor

- Programmable Using Standard 8051 C Compilers

- Up to Four Programmable GPIO Pins

- General Features

- Two I<sup>2</sup>C Ports for Slave or Master Download

- Single 3.3-V Power Supply

- Integrated Regulators

## 1.2 Applications

- MP3 Player/Music Phone Docks

- Speaker Bars

- Mini/Micro-Component Systems

- **Musical Instruments**

- Speaker Equalization

- **Studio Monitors**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PurePath Studio is a trademark of Texas Instruments.

www.ti.com

## 1.3 Description

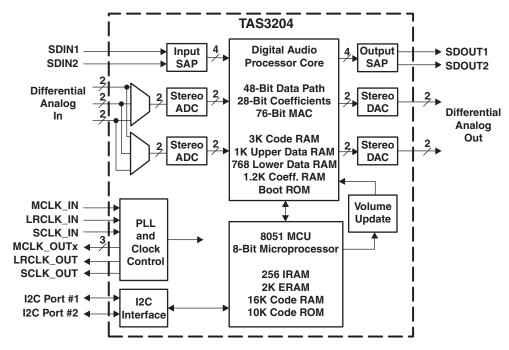

The TAS3204 is a highly-integrated audio system-on-chip (SOC) consisting of a fully-programmable, 48-bit digital audio processor, a 3:1 stereo analog input MUX, four ADCs, four DACs, and other analog functionality. The TAS3204 is programmable with the graphical PurePath Studio<sup>™</sup> suite of DSP code development software. PurePath Studio is a highly intuitive, drag-and-drop environment that minimizes software development effort while allowing the end user to utilize the power and flexibility of the TAS3204's digital audio processing core.

TAS3204 processing capability includes speaker equalization and crossover, volume/bass/treble control, signal mixing/MUXing/splitting, delay compensation, dynamic range compression, and many other basic audio functions. Audio functions such as matrix decoding, stereo widening, surround sound virtualization and psychoacoustic bass boost are also available with either third-party or TI royalty-free algorithms.

The TAS3204 contains a custom-designed, fully-programmable 135-MHz, 48-bit digital audio processor. A 76-bit accumulator ensures that the high precision necessary for quality digital audio is maintained during arithmetic operations.

Four differential 102 dB DNR ADCs and four differential 105 dB DNR DACs ensure that high quality audio is maintained through the whole signal chain as well as increasing robustness against noise sources such as TDMA interference.

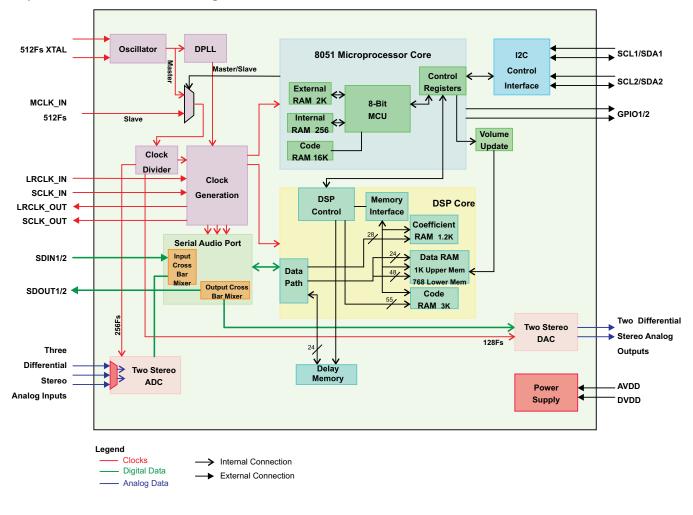

The TAS3204 is composed of eight functional blocks:

- 1. Clocking System

- 2. Digital Audio Interface

- 3. Analog Audio Interface

- 4. Power supply

- 5. Clocks, digital PLL

- 6. I<sup>2</sup>C control interface

- 7. 8051 MCUcontroller

- 8. Audio DSP digital audio processing

### **Expanded Functional Block Diagram**

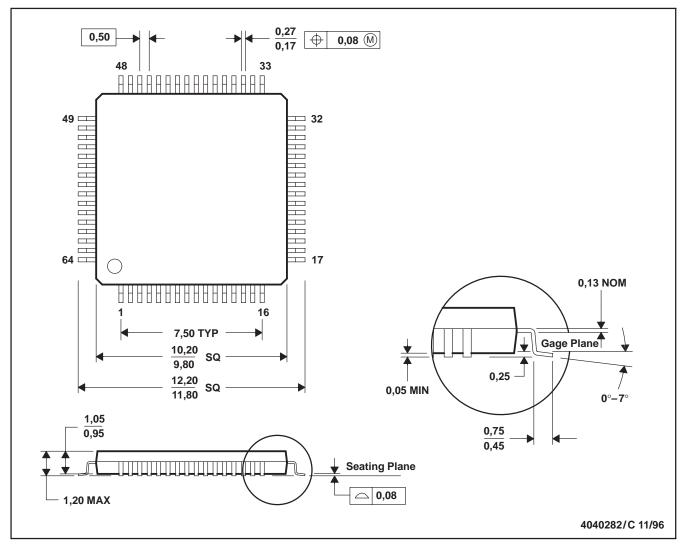

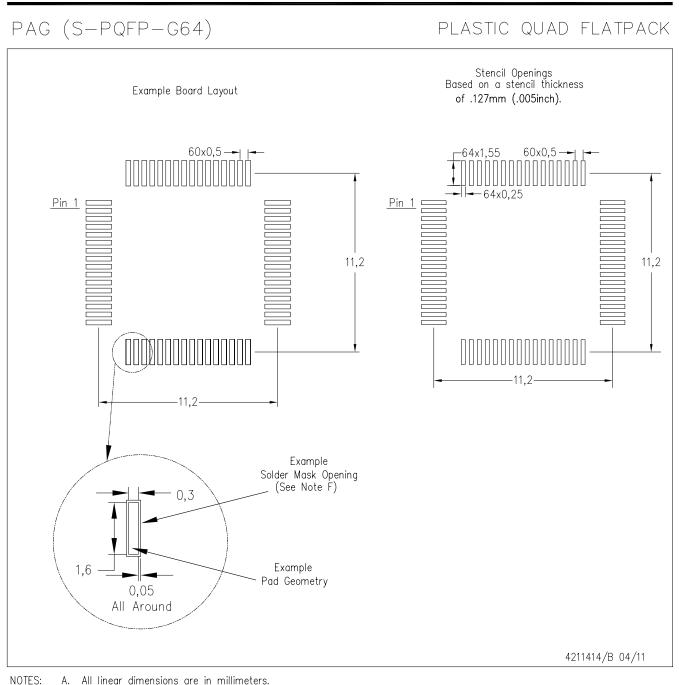

## 1.4 Ordering Information

| T <sub>A</sub> | PLASTIC 64-PIN PQFP (PN) <sup>(1)(2)</sup> |  |

|----------------|--------------------------------------------|--|

| 0°C to 70°C    | TAS3204PAG                                 |  |

(1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at <a href="http://www.ti.com">www.ti.com</a>.

## TAS3204

SLES197C-APRIL 2007-REVISED MARCH 2011

| 1   | Intro | duction                                  | . <u>1</u>      |

|-----|-------|------------------------------------------|-----------------|

|     | 1.1   | Features                                 | . <u>1</u>      |

|     | 1.2   | Applications                             | _               |

|     | 1.3   | Description                              |                 |

|     | 1.4   | Ordering Information                     |                 |

| 2   | Phys  | ical Characteristics                     | . <u>5</u>      |

|     | 2.1   | Terminal Assignments                     | . <u>5</u>      |

|     | 2.2   | Terminal Descriptions                    | _               |

| 3   | TAS   | 3204 Clocking System                     | . <u>8</u>      |

|     | 3.1   | Core Clock Management                    | • <u>8</u>      |

|     | 3.2   | SAP Clock Management                     | _               |

| 4   | 0     | al Audio Interface                       | <u>11</u>       |

| _   | 4.1   | Serial Audio Port (SAP)                  | 11              |

| 5   |       | og Audio Interface                       | <u>17</u>       |

|     | 5.1   | Analog to Digital Converters ADCs        | <u>17</u>       |

|     | 5.2   | Digital to Analog Converters DACs        | <u>17</u>       |

|     | 5.3   | Analog Reference System                  | <u>17</u>       |

| 6   |       | edded MCUcontroller                      | <u>18</u>       |

|     | 6.1   | MCU Addressing Modes                     | <u>18</u>       |

| -   | 6.2   | Boot Up Sequence                         | <u>19</u>       |

| 7   | -     | al Audio Processor                       | <u>20</u>       |

|     | 7.1   | Audio Digital Signal Processor Core      | <u>22</u>       |

|     | 7.2   | DAP Instructions Set                     | 22              |

| _   | 7.3   | DAP Data Word Structure                  | 23              |

| 8   |       | control Interface                        | <u>25</u>       |

|     | 8.1   | General I <sup>2</sup> C Operations      | <u>25</u>       |

|     | 8.2   | I <sup>2</sup> C Master Interface        | <u>26</u>       |

|     | 8.3   | I <sup>2</sup> C Slave Mode Operation    | 31              |

| 9   |       | 3204 Control Pins                        | <u>35</u>       |

|     | 9.1   | Reset (RESET) - Power-Up Sequence        | <u>35</u>       |

|     | 9.2   | Voltage Regulator Enable (VREG_EN)       | <u>35</u>       |

|     | 9.3   | Power Down (PDN)                         | <u>35</u>       |

|     | 9.4   | I <sup>2</sup> C Bus Control (CS0)       | <u>36</u>       |

| 4.0 | 9.5   | Programmable I/O (GPIO)                  | <u>36</u>       |

| 10  | -     | rithm and Software Development Tools for | 20              |

| 11  | TAS:  | 3204                                     | <u>38</u><br>39 |

|     | Elect |                                          | 23              |

|     |       |                                          |                 |

### www.ti.com

|    | 11.1               | Absolute Maximum Ratings                                                                                                                                       | <u>39</u> |

|----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|    | 11.2               | Package Dissipation Ratings                                                                                                                                    | <u>39</u> |

|    | 11.3               | Recommended Operating Conditions                                                                                                                               | <u>39</u> |

|    | 11.4               | Electrical Characteristics                                                                                                                                     | <u>40</u> |

|    | 11.5               | Audio Specifications                                                                                                                                           | <u>40</u> |

|    | 11.6               | Timing Characteristics                                                                                                                                         | <u>43</u> |

|    | 11.7               | Master Clock                                                                                                                                                   | <u>43</u> |

|    | 11.8<br>11.9       | Serial Audio Port, Slave Mode<br>Serial Audio Port Master Mode Signals (TAS3204)                                                                               | <u>44</u> |

|    | 11.10              | Pin-Related Characteristics of the SDA and SCL $1/2$ During the $5/2$ Mark $1/2$ During the $5/2$ Mark $1/2$ During the $1/2$                                  | <u>45</u> |

|    | 11.11              | I/O Stages for F/S-Mode I <sup>2</sup> C-Bus Devices<br>Bus-Related Characteristics of the SDA and SCL<br>I/O Stages for F/S-Mode I <sup>2</sup> C-Bus Devices | <u>46</u> |

|    | 11.12              | Reset Timing                                                                                                                                                   | <u>48</u> |

| 12 | I <sup>2</sup> C R | egister Map                                                                                                                                                    | <u>49</u> |

|    | 12.1               | Clock Control Register (0x00)                                                                                                                                  | <u>50</u> |

|    | 12.2               | MCUcontroller Clock Control Register                                                                                                                           | <u>50</u> |

|    | 12.3               | Status Register (0x02)                                                                                                                                         | <u>51</u> |

|    | 12.4               | I <sup>2</sup> C Memory Load Control and Data Registers (0x04 and 0x05)                                                                                        | <u>52</u> |

|    | 12.5               | Memory Access Registers (0x06 and 0x07)                                                                                                                        | <u>53</u> |

|    | 12.6               | Device Version (0x08)                                                                                                                                          | <u>54</u> |

|    | 12.7               | Analog Power Down Control (0x10 and 0x11)                                                                                                                      | <u>54</u> |

|    | 12.8               | Analog Input Control (0x12)                                                                                                                                    | <u>55</u> |

|    | 12.9<br>12.10      | Dynamic Element Matching (0x13)<br>Current Control Select (0x14, 0x15, 0x17, 0x18)                                                                             | <u>55</u> |

|    |                    |                                                                                                                                                                | <u>56</u> |

|    | 12.11              | DAC Control (0x1A, 0x1B, 0x1D)                                                                                                                                 | <u>60</u> |

|    | 12.12              | ADC and DAC Reset (0x1E)                                                                                                                                       | <u>62</u> |

|    | 12.13              | ADC Input Gain Control (0x1F)                                                                                                                                  | <u>62</u> |

|    | 12.14              | MCLK_OUT Divider (0x21 and 0x22)                                                                                                                               | <u>63</u> |

|    | 12.15<br>12.16     | Digital Cross Bar (0x30 to 0x3F)<br>Extended Special Function Registers (ESFR) Map                                                                             | <u>63</u> |

| 10 | امما               | instion Information                                                                                                                                            | <u>65</u> |

| 13 | ••                 | Schemation                                                                                                                                                     | <u>70</u> |

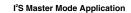

|    | 13.1<br>13.2       | Schematics                                                                                                                                                     | 70<br>71  |

|    |                    |                                                                                                                                                                | <u> </u>  |

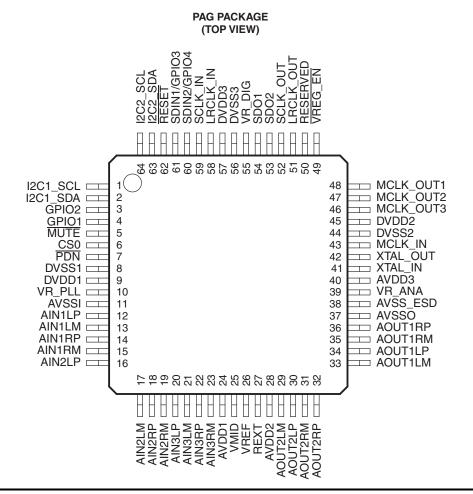

## 2 Physical Characteristics

## 2.1 Terminal Assignments

## Texas **NSTRUMENTS**

www.ti.com

#### 22 **Terminal Descriptions**

| .2 Terminal Descriptions |        |                                 |                                    |                                                                                           |  |  |

|--------------------------|--------|---------------------------------|------------------------------------|-------------------------------------------------------------------------------------------|--|--|

|                          | AL NO. | INPUT/<br>OUTPUT <sup>(1)</sup> | PULLUP/<br>PULLDOWN <sup>(2)</sup> | DESCRIPTION                                                                               |  |  |

| AIN1LM                   | 13     |                                 | Pull to VMID <sup>(3)</sup>        | Analog channel 1 left negative input                                                      |  |  |

| AIN1LM<br>AIN1LP         | 13     | Analog Input<br>Analog Input    |                                    | Analog channel 1 left positive input                                                      |  |  |

| AIN1RM                   | 12     | Analog Input                    | Pull to VMID <sup>(3)</sup>        | Analog channel 1 right negative input                                                     |  |  |

| AINTRM<br>AINTRP         | 13     | Analog Input<br>Analog Input    |                                    | Analog channel 1 right positive input                                                     |  |  |

| AIN1KI<br>AIN2LM         | 14     | Analog Input                    | Pull to VMID <sup>(3)</sup>        | Analog channel 2 left negative input                                                      |  |  |

| AIN2LM<br>AIN2LP         | 16     | Analog Input<br>Analog Input    |                                    | Analog channel 2 left positive input                                                      |  |  |

| AIN2LF<br>AIN2RM         | 10     | Analog Input                    | Pull to VMID <sup>(3)</sup>        | Analog channel 2 right negative input                                                     |  |  |

| AIN2RM<br>AIN2RP         | 19     | 0 1                             |                                    |                                                                                           |  |  |

| AIN3LM                   | 21     | Analog Input                    | Pull to VMID <sup>(3)</sup>        | Analog channel 2 right positive input                                                     |  |  |

|                          |        | Analog Input                    |                                    | Analog channel 3 left negative input                                                      |  |  |

| AIN3LP                   | 20     | Analog Input                    | Pull to VMID <sup>(3)</sup>        | Analog channel 3 left positive input                                                      |  |  |

| AIN3RM                   | 23     | Analog Input                    |                                    | Analog channel 3 right negative input                                                     |  |  |

| AIN3RP                   | 22     | Analog Input                    |                                    | Analog channel 3 right positive input                                                     |  |  |

| AOUT1LM                  | 33     | Analog Output                   |                                    | Analog channel 1 left negative output                                                     |  |  |

| AOUT1LP                  | 34     | Analog Output                   |                                    | Analog channel 1 left positive output                                                     |  |  |

| AOUT1RM                  | 35     | Analog Output                   |                                    | Analog channel 1 right negative output                                                    |  |  |

| AOUT1RP                  | 36     | Analog Output                   |                                    | Analog channel 1 right positive output                                                    |  |  |

| AOUT2LM                  | 29     | Analog Output                   |                                    | Analog channel 2 left negative output                                                     |  |  |

| AOUT2LP                  | 30     | Analog Output                   |                                    | Analog channel 2 left positive output                                                     |  |  |

| AOUT2RM                  | 31     | Analog Output                   |                                    | Analog channel 2 right negative output                                                    |  |  |

| AOUT2RP                  | 32     | Analog Output                   |                                    | Analog channel 2 right positive output                                                    |  |  |

| AVDBit 1                 | 24     | Power                           |                                    | 3.3-V analog power. This pin must be decoupled according to good design practices.        |  |  |

| AVSS1                    | 11     | Power                           |                                    | Analog ground                                                                             |  |  |

| AVDBit 2                 | 28     | Power                           |                                    | 3.3-V analog power. This pin must be decoupled according to good design practices.        |  |  |

| AVSS2                    | 37     | Power                           |                                    | Analog ground                                                                             |  |  |

| AVDBit 3                 | 40     | Power                           |                                    | 3.3-V analog power supply. This pin must be decoupled according to good design practices. |  |  |

| AVSS3                    | 38     | Power                           |                                    | Analog ground                                                                             |  |  |

| CS0                      | 6      | Digital Input                   |                                    | I <sup>2</sup> C chip select                                                              |  |  |

| DVDBit 1                 | 9      | Power                           |                                    | 3.3-V digital power. This pin must be decoupled according to good design practices.       |  |  |

| DVSS1                    | 8      | Power                           |                                    | Digital ground                                                                            |  |  |

| DVDBit 2                 | 45     | Power                           |                                    | 3.3-V digital power. This pin must be decoupled according to good design practices.       |  |  |

| DVSS2                    | 44     | Power                           |                                    | Digital ground                                                                            |  |  |

| DVDBit 3                 | 57     | Power                           |                                    | 3.3-V digital power. This pin must be decoupled according to good design practices.       |  |  |

| DVSS3                    | 56     | Power                           |                                    | Digital ground                                                                            |  |  |

| GPIO1                    | 4      | Digital IO                      |                                    | General purpose input/output pin #1.                                                      |  |  |

| GPIO2                    | 3      | Digital IO                      |                                    | General purpose input/output pin #2                                                       |  |  |

| I2C1_SCL                 | 1      | Digital Input                   |                                    | Slave I <sup>2</sup> C serial control data interface input/output.                        |  |  |

| I2C1_SDA                 | 2      | Digital I/O                     |                                    | Slave I <sup>2</sup> C serial clock input.                                                |  |  |

| I2C2_SCL                 | 64     | Digital Input                   |                                    | Master I <sup>2</sup> C serial control data interface input/output.                       |  |  |

I = input; O = output

All pullups are 20-μA *weak* pullups, and all pulldowns are 20-μA *weak* pulldowns. The pullups and pulldowns are included to ensure proper input logic levels if the terminals are left unconnected (pullups  $\rightarrow$  logic 1 input; pulldowns  $\rightarrow$  logic 0 input). Devices that drive inputs with pullups must be able to sink 20  $\mu$ A while maintaining a logic-0 drive level. Devices that drive inputs with pulldowns must be able to source 20  $\mu$ A while maintaining a logic-1 drive level.

Pull to VMID when analog input is in single-ended mode. (3)

6 Physical Characteristics

| TERMINAL    |     | INPUT/ PULLUP/                                |          |                                                                                                                                                                                                                                                                                          |  |  |

|-------------|-----|-----------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO. | OUTPUT <sup>(1)</sup> PULLDOWN <sup>(2)</sup> |          | DESCRIPTION                                                                                                                                                                                                                                                                              |  |  |

| I2C2_SDA    | 63  | Digital I/O                                   |          | Master I <sup>2</sup> C serial clock input.                                                                                                                                                                                                                                              |  |  |

| LRCLK_IN    | 58  | Digital Input                                 | Pulldown | Left/right (frame) clock input for I <sup>2</sup> S interface                                                                                                                                                                                                                            |  |  |

| LRCLK_OUT   | 51  | Digital Output                                |          | Left/right (frame) clock output for I <sup>2</sup> S interface                                                                                                                                                                                                                           |  |  |

| MCLK_IN     | 43  | Digital Input                                 | Pulldown | Master clock input for I <sup>2</sup> S interface. Frequency = 512 x $F_s$                                                                                                                                                                                                               |  |  |

| MCLK_OUT1   | 48  | Digital Output                                |          | Master clock output for I <sup>2</sup> S interface Frequency = 256 x $F_s$                                                                                                                                                                                                               |  |  |

| MCLK_OUT2   | 47  | Digital Output                                |          | Programmable master clock output divider                                                                                                                                                                                                                                                 |  |  |

| MCLK_OUT3   | 46  | Digital Output                                |          | Programmable master clock output divider                                                                                                                                                                                                                                                 |  |  |

| MUTE        | 5   | Digital Input                                 | Pulldown | This pin needs to be programmed as mute pin in the application code.<br>In has no function in default after reset.                                                                                                                                                                       |  |  |

| PDN         | 7   | Digital Input                                 |          | Powerdown active LOW. After successful boot, its function is defined by the boot code.                                                                                                                                                                                                   |  |  |

| RESERVED    | 50  | N/A                                           | Pulldown | Pin must be connected to ground                                                                                                                                                                                                                                                          |  |  |

| RESET       | 62  | Digital Input                                 | Pullup   | Device reset. This pin is active low.                                                                                                                                                                                                                                                    |  |  |

| REXT        | 27  | Analog Output                                 |          | This pin must be connected to a 22 k $\Omega$ (1% tolerance) external resistor to ground to set analog currents. Trace capacitance must be kept low.                                                                                                                                     |  |  |

| SCLK_IN     | 59  | Digital Input                                 |          | Serial (bit) clock input for I <sup>2</sup> S interface                                                                                                                                                                                                                                  |  |  |

| SCLK_OUT    | 52  | Digital Output                                |          | Serial (bit) clock output for I <sup>2</sup> S interface                                                                                                                                                                                                                                 |  |  |

| SDIN1/GPIO3 | 61  | Digital I/O                                   | Pullup   | Serial data input #1 for I <sup>2</sup> S interface / general purpose input/output #3                                                                                                                                                                                                    |  |  |

| SDIN2/GPIO4 | 60  | Digital I/O                                   | Pullup   | Serial data input #2 for I <sup>2</sup> S interface / general purpose input/output #4                                                                                                                                                                                                    |  |  |

| SDOUT1      | 54  | Digital Output                                |          | Serial data output #1 for I <sup>2</sup> S interface                                                                                                                                                                                                                                     |  |  |

| SDOUT2      | 53  | Digital Output                                |          | Serial data output #2 for I <sup>2</sup> S interface                                                                                                                                                                                                                                     |  |  |

| VMID        | 25  | Analog Output                                 |          | Analog mid supply reference. This pin must be decoupled with a $0.1\text{-}\mu\text{F}$ low-ESR capacitor and an external $10\text{-}\mu\text{F}$ filter cap. $^{(4)}$                                                                                                                   |  |  |

| VR_ANA      | 39  | Power                                         |          | Voltage reference for analog supply. A pin-out of the internally regulated 1.8 V power. A 0.1- $\mu$ F low ESR capacitor and a 4.7- $\mu$ F filter capacitor must be connected between this terminal and AVSS. This terminal must not be used to power external devices. <sup>(4)</sup>  |  |  |

| VR_DIG      | 55  | Power                                         |          | Voltage reference for digital supply. A pin-out of the internally regulated 1.8 V power. A 0.1- $\mu$ F low ESR capacitor and a 4.7- $\mu$ F filter capacitor must be connected between this terminal and DVSS. This terminal must not be used to power external devices. <sup>(4)</sup> |  |  |

| VR_PLL      | 10  | Power                                         |          | Voltage reference for DPLL supply. A pin-out of internally regulated 1.8-V power supply. A 0.1- $\mu$ F low-ESR capacitor and a 4.7- $\mu$ F filter capacitor must be connected between this terminal and DVSS. This terminal must not be used to power external devices. <sup>(4)</sup> |  |  |

| VREF        | 26  | Analog Output                                 |          | Band gap output. A 0.1- $\mu F$ low ESR capacitor should be connected between this terminal and AVSS. This terminal must not be used to power external devices. $^{(4)}$                                                                                                                 |  |  |

| VREG_EN     | 49  | Digital Input                                 |          | Voltage regulator enable active low.                                                                                                                                                                                                                                                     |  |  |

| XTAL_IN     | 41  | Digital Input                                 |          | Crystal input. Frequency = 512 x Fs                                                                                                                                                                                                                                                      |  |  |

| XTAL_OUT    | 42  | Digital Output                                |          | Crystal output. Frequency = 512 x Fs                                                                                                                                                                                                                                                     |  |  |

(4) If desired, low ESR capacitance values can be implemented by paralleling two or more ceramic capacitors of equal value. Paralleling capacitors of equal value provide an extended high frequency supply decoupling.

## 3 TAS3204 Clocking System

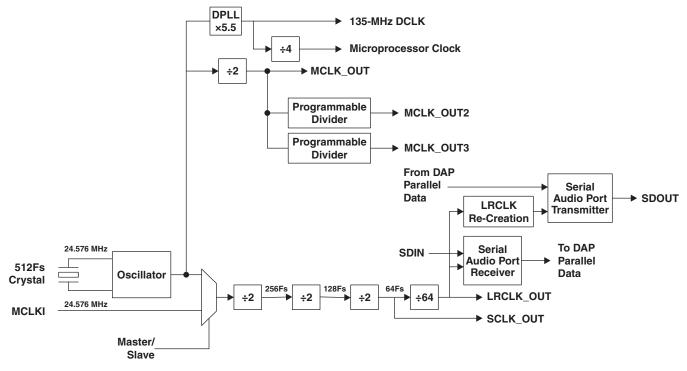

Clock management for the TAS3204 consists of two control structures:

- Core Clock management

- Oversees the selection of the clock frequencies for the 8051 MCU, the I<sup>2</sup>C controller, and the audio DSP core

- The master clock (MCLK\_IN or XTAL\_IN) is the source for these clocks.

- In most applications, the master clock drives an on-chip digital phase-locked loop (DPLL), and the DPLL output drives the MCU and audio DSP clocks.

- DPLL bypass mode is also available, in which the high-speed master clock directly drives the MCU and audio DSP clocks.

- Serial Audio Port (SAP) clock management

- Oversees SAP master/slave mode

- Controls output of SCLKOUT, and LRCLK in the SAP master mode

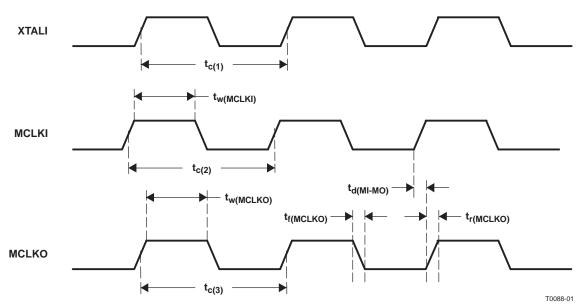

Figure 3-1 shows a block diagram of the TAS3204 clocking scheme.

Figure 3-1. Clock Generation

## 3.1 Core Clock Management

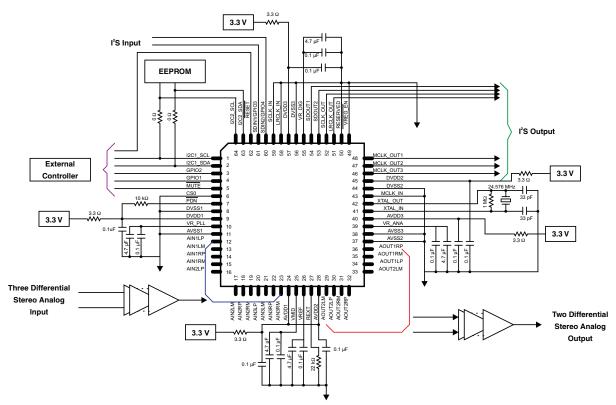

The TAS3204 DSP, MCU, and I2C Controller core clocks are derived from the on chip oscillator provided that an external crystal and associated circutry are provided.

- DSP clock operates at a fixed frequency of 2816 x Fs

- MCU clock operates at a fixed frequency of 704 x Fs.

- I<sup>2</sup>controller core operates at a fixed frequency of (256 x Fs).

## 3.2 SAP Clock Management

The Serial Audio Port in the TAS3204 can be clocked in two modes of operation: Master and Slave. By default, the TAS3204 is configured in master mode.

**Clock Master operation:** In Clock Master operation, the onboard oscillator provides the reference for the SAP clock outputs provided an external crystal is present.

- LRCLK\_OUT fixed at a frequency of 48 kHz (Fs).

- SCLK\_OUT is fixed at a frequency of (64 x Fs).

- MCLK\_OUT is fixed at a frequency of (256 x Fs).

- In master mode, the external ASRC converts incoming serial audio data to 48-kHz sample rate synchronous to the internally generated serial audio data clocks.

**Clock Slave operation:** In Clock Slave operation, the SAP clock inputs are provided externally (that is, by a system controller) and passed through to the SAP Outputs. The MCLK\_IN signal is internally divided down and sent directly to the ADC and DAC blocks, therefore analog audio performace is dependant on the quality of the MCLK\_IN signal. As a result, degradation in analog performance is to be expected if the quality of MCLK\_IN (that is, jitter, phase noise, etc) is not robust.

DISCLAIMER: Analog performance is not ensured in slave mode, as the analog performance depends upon the quality of the MCLK\_IN. The TAS3204 is not robust with respect to MCLK\_IN errors (glitches, etc.); if the MCLK\_IN frequency changes under operation, the device must be reset.

- MCLK\_IN (512 × Fs),

- SCLK\_IN (64 × Fs), and

- LRCLK\_IN (Fs) are supplied externally by an clocking device.

- •

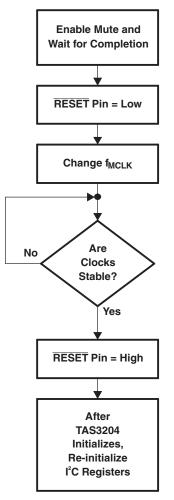

When the TAS3204 is used in a system in which the master clock frequency ( $f_{MCLK}$ ) can change, the TAS3204 must be reset during the frequency change. In these cases, the procedure shown in Figure 3-2 should be used.

In slave mode, all incoming serial audio data must be synchronous to an incoming LRCLK\_IN of 44.1 kHz or 48 kHz.

The TAS3204 only supports dynamic sample-rate changes between any of the supported sample frequencies when a fixed-frequency master clock is provided. During dynamic sample-rate changes, the TAS3204 remains in normal operation and the register contents are preserved. To avoid producing audio artifacts during the sample-rate changes, a volume or mute control can be included in the application firmware that mutes the output signal during the sample-rate change. The fixed-frequency clock can be provided by a crystal attached to XTAL\_IN and XTAL\_OUT or an external 3.3-V fixed-frequency TTL source attached to MCLK\_IN.

Changing the sample rate on the fly in slave mode should be handled by a host system controller. The TAS3204 does not include any internal clock error or click/pop detection managment. Customer specific DAP filter coefficients must be uploaded by a host system controller when changing the sample rate.

www.ti.com

Figure 3-2. Master Clock Frequency (f<sub>MCLK</sub>) Change Procedure

| F <sub>S</sub> Sample<br>Rate (kHz) | Ch Per<br>SDIN                             | MCLK/<br>LRCLK<br>Ratio<br>(× f <sub>S</sub> ) | MCLK<br>Freq<br>(MHz) | SCLKIN<br>Rate<br>(× f <sub>S</sub> ) | SCLK_IN<br>Freq<br>(MHz) | SCLK_OUT<br>Rate<br>(× f <sub>S</sub> ) | Ch Per<br>SDOUT | LRCLK<br>(F <sub>S</sub> ) | PLL<br>Multiplier | F <sub>DSPCLK</sub><br>(MHz) | f <sub>dspclk</sub> /f <sub>s</sub> |

|-------------------------------------|--------------------------------------------|------------------------------------------------|-----------------------|---------------------------------------|--------------------------|-----------------------------------------|-----------------|----------------------------|-------------------|------------------------------|-------------------------------------|

|                                     | Slave Mode, 2 Channels In, 2 Channels Out  |                                                |                       |                                       |                          |                                         |                 |                            |                   |                              |                                     |

| 44.1                                | 2                                          | 512                                            | 22.579                | 64                                    | 2.822                    | 64                                      | 2               | 64                         | 5.5               | 124.2                        | 2816                                |

| 48                                  | 2                                          | 256                                            | 24.576                | 64                                    | 3.072                    | 64                                      | 2               | 64                         | 5.5               | 135.2                        | 2816                                |

|                                     | Master Mode, 2 Channels In, 2 Channels Out |                                                |                       |                                       |                          |                                         |                 |                            |                   |                              |                                     |

| 48                                  | 2                                          | 256                                            | 24.576                | N/A                                   | N/A                      | 64                                      | 2               | 64                         | 5.5               | 135.2                        | 2816                                |

## 4 Digital Audio Interface

## 4.1 Serial Audio Port (SAP)

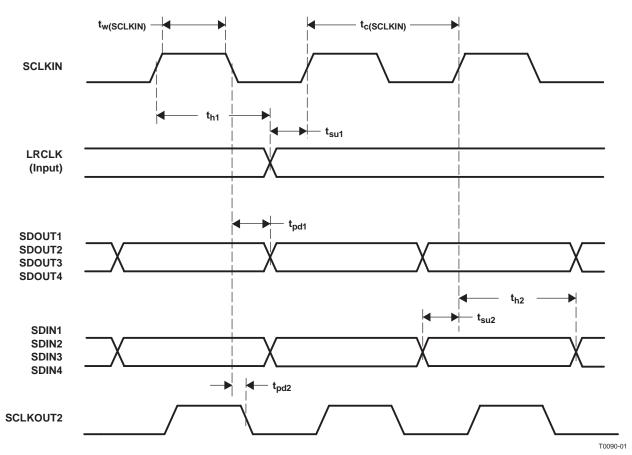

The TAS3204 can accept four channels of 16, 20, or 24 bit digial serial audio in the I<sup>2</sup>S, discrete left justified, or discrete right justified formats.

The TAS3204 can provide four channels of 16, 20, or 24 bit digital serial audio in I<sup>2</sup>S, discrete left justified, or discrete right justified format. Output data rate is the same data rate as the input. The SDOUT output uses the SCLK\_OUT and LRCLK\_OUT signals to provide synchronization.

The TAS3204 supported data formats are listed in Table 4-1.

| Input SAP (SDIN1, SDIN2)   | Output SAP (SDOUT1, SDOUT2) |

|----------------------------|-----------------------------|

| 2-channel I <sup>2</sup> S | 2-channel I <sup>2</sup> S  |

| 2-channel left-justified   | 2-channel left-justified    |

| 2-channel right-justified  | 2-channel right-justified   |

## Table 4-1. Supported Data Formats

| Mode      | Input<br>Control<br>IM[3:0] | Output<br>Control<br>OM[3:0] | Serial Format    | Word Lengths | Data<br>Rates<br>(kHz) | MAX<br>SCLK<br>(MHz) |

|-----------|-----------------------------|------------------------------|------------------|--------------|------------------------|----------------------|

|           | 0000                        | 0000                         | Left-justified   | 16, 20, 24   |                        |                      |

| 2-channel | 0001                        | 0001                         | Right-justified  | 16, 20, 24   | 32–48                  | 3.072                |

|           | 0010                        | 0010                         | l <sup>2</sup> S | 16, 20, 24   |                        |                      |

### Table 4-2. Serial Data Input and Output Formats

# TAS3204

Texas Instruments

www.ti.com

SLES197C-APRIL 2007-REVISED MARCH 2011

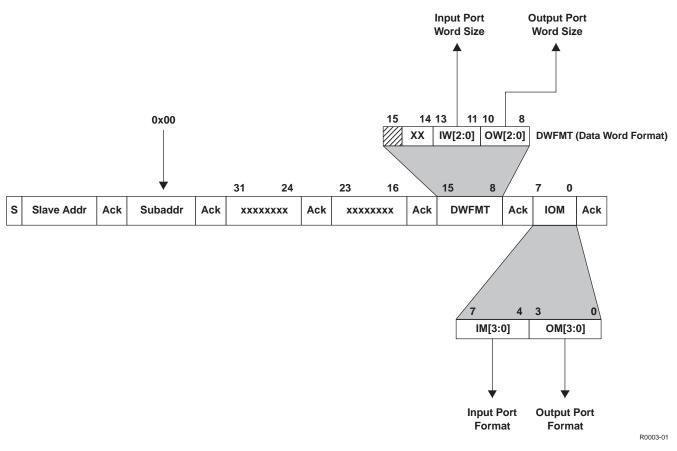

## Figure 4-1. Serial Data Controls

| IW1, OW1 | IW0, OW0 | FORMAT      |

|----------|----------|-------------|

| 0        | 0        | Reserved    |

| 0        | 1        | 16-bit data |

| 1        | 0        | 20-bit data |

| 1        | 1        | 24-bit data |

Following a reset, ensure that the clock register (0x00) is written before performing volume, treble, or bass updates.

Commands to reconfigure the SAP can be accompanied by mute and unmute commands for quiet operation. However, care must be taken to ensure that the mute command has completed before the SAP is commanded to reconfigure. Similarly, the TAS3204 should not be commanded to unmute until after the SAP has completed a reconfiguration. The reason for this is that an SAP configuration change while a volume or bass or treble update is taking place can cause the update not to be completed properly.

When the TAS3204 is transmitting serial data, it uses the negative edge of SCLK to output a new data bit. The TAS3204 samples incoming serial data on the rising edge of SCLK.

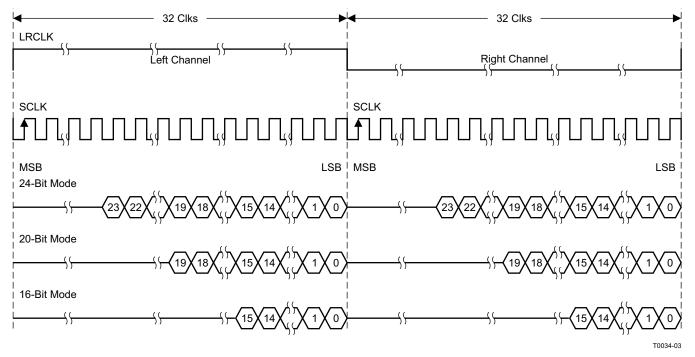

## 4.1.1 2-Channel I<sup>2</sup>S Timing

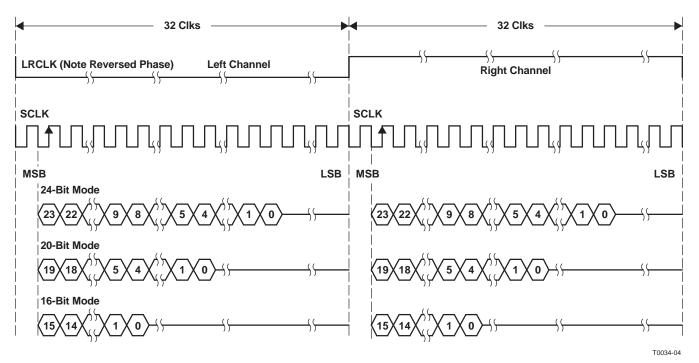

In 2-channel I<sup>2</sup>S timing, LRCLK is LOW when left-channel data is transmitted and HIGH when right-channel data is transmitted. SCLK is a bit clock running at 64 ×  $f_S$  which clocks in each bit of the data. There is a delay of one bit clock from the time the LRCLK signal changes state to the first bit of data on the data lines. The data is written MSB first and is valid on the rising edge of the bit clock. The TAS3204 masks unused trailing data-bit positions.

2-Channel I<sup>2</sup>S (Philips Format) Stereo Input/Output

Figure 4-2. I<sup>2</sup>S 64f<sub>S</sub> Format

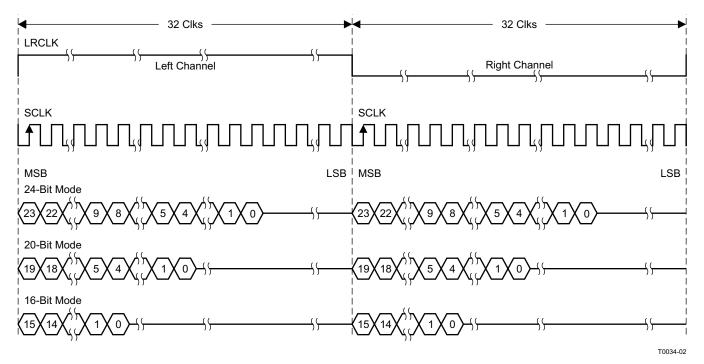

## 4.1.2 2-Channel Left-Justified Timing

In 2-channel left-justified timing, LRCLK is HIGH when left-channel data is transmitted and LOW when right-channel data is transmitted. SCLK is a bit clock running at 64 ×  $f_S$ , which clocks in each bit of the data. The first bit of data appears on the data lines at the same time LRCLK toggles. The data is written MSB first and is valid on the rising edge of the bit clock. The TAS3204 masks unused trailing data-bit positions.

2-Channel Left-Justified Stereo Input

Figure 4-3. Left-Justified 64f<sub>S</sub> Format

## 4.1.3 2-Channel Right-Justified Timing

In 2-channel right-justified (RJ) timing, LRCLK is HIGH when left-channel data is transmitted and LOW when right-channel data is transmitted. SCLK is a bit clock running at  $64 \times f_S$  which clocks in each bit of the data. The first bit of data appears on the data lines 8 bit-clock periods (for 24-bit data) after LRCLK toggles. In the RJ mode, the last bit clock before LRCLK transitions always clocks the LSB of data. The data is written MSB first and is valid on the rising edge of the bit clock. The TAS3204 masks unused leading data-bit positions.

2-Channel Right-Justified (Sony Format) Stereo Input

Figure 4-4. Right-Justified 64f<sub>s</sub> Format

## 4.1.4 SAP Input to SAP Output—Processing Flow

All SAP data format options other than  $I^2S$  result in a two-sample delay from input to output. If  $I^2S$  formatting is used for both the input SAP and the output SAP, the polarity of LRCLK must be inverted. However, if  $I^2S$  format conversions are performed between input and output, the delay becomes either 1.5 samples or 2.5 samples, depending on the processing clock frequency selected for the audio DSP core relative to the sample rate of the incoming data.

The I<sup>2</sup>S format uses the falling edge of LRCLK to begin a sample period, whereas all other formats use the rising edge of LRCLK to begin a sample period. This means that the input SAP and audio DSP core operate on sample windows that are 180° out of phase with respect to the sample window used by the output SAP. This phase difference results in the output SAP outputting a new data sample at the midpoint of the sample period used by the audio DSP core to process the data. If the processing cycle completes all processing tasks before the midpoint of the processing sample period, the output SAP outputs this processed data. However, if the processing time extends past the midpoint of the processing sample period. In the former case, the delay from input to output is 1.5 samples. In the latter case, the delay from input to output is 2.5 samples.

Copyright © 2007-2011, Texas Instruments Incorporated

The delay from input to output can thus be either 1.5 or 2.5 sample times when data format conversions are performed that involve the  $I^2S$  format. However, which delay time is obtained for a particular application is determinable and fixed for that application, providing care is taken in the selection of MCLK\_IN/XTAL\_IN with respect to the incoming sample clock, LRCLK.

## 5 Analog Audio Interface

## 5.1 Analog to Digital Converters ADCs

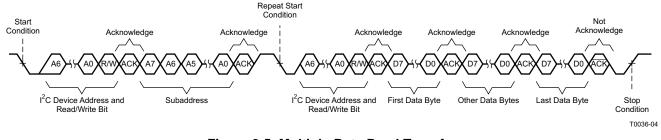

The TAS3204 has three differential analog stereo inputs that can be sent to either of two ADCs to be converted to digital data. The input multiplexers include a preamplifier. This amplifier is driving the ADCs, and it is digitally controlled with changes synchronized with the sample clock of the ADC. Minimal crosstalk between selected channels and unselected channels is maintained. When inputs are not needed they are configured for minimal noise. Also included in this module are two fully differential over sampled stereo ADCs. The ADCs are sigma-delta modulators with 256 times over-sampling ratio. Because of the over-sampling nature of the audio ADCs and integrated digital decimation filters, requirements for analog anti-aliasing filtering are relaxed. Filter performance for the ADCs are specified under physical characteristics.

## 5.2 Digital to Analog Converters DACs

The TAS3204 has two stereo audio DACs, each of which consists of a digital interpolation filter, digital sigma-delta modulator and an analog reconstruction filter. Each DAC can operate a maximum sampling frequency of 48 kHz. Each DAC upsamples the incoming data by 128 and performs interpolation filtering and processing on this data before conversion to a stereo analog output signal. The sigma-delta modulator always operates at a rate of 128x xFs, which ensures that quantization noise generated within the modulator stays low within the frequency band below Fs/2.4 at all sample rates. The digital interpolation filters for interpolation from Fs to 8xFs are included in the audio DSP upper memory (reserved for analog processing), while interpolation from 8xFs to 128 x Fs is done in a dedicated hardware sample and hold filter. The TAS3204 includes two stereo line driver outputs. All line drivers are capable of driving up to a 10-k $\Omega$  load. Each stereo output can be in power-down mode when not used. Popless operation is achieved by conforming to start and stop sequences in the device controller code.

## 5.3 Analog Reference System

This module provides all internal references needed by the analog modules. It also provides bias currents for all analog blocks. External decoupling capacitors are needed along with an external 1% tolerance resistor to set the internal bias currents. It includes a band-gap reference and several voltage buffers and a tracking current reference. The TAS3204 also uses an internally generated mid supply that is used to rereference all analog inputs and is present on all analog outputs. VMID is the analog mid supply and can be used when buffered externally to rereference the analog inputs and outputs. The voltage reference REXT requires a  $22 \cdot k\Omega$  1% resistor to ground. The reference system can be powered down separately.

## 6 Embedded MCUcontroller

The 8051 MCUcontroller receives and distributes I<sup>2</sup>C data, and participates in most processing tasks requiring multiframe processing cycles. The MCU has its own data RAM for storing intermediate values and queuing I<sup>2</sup>C commands, a fixed boot-program ROM, and a program RAM. The MCU boot program cannot be altered. The MCU controller has specialized hardware for master and slave interface operation, volume updates, and a programmable interval timer interrupt. For more information see the *TAS3108/TAS3108IA Firmware Programmer's Guide* (SLEU067).

Once the MCUcontroller program memory has been loaded, it cannot be updated until the TAS3204 has been reset.

## 6.1 MCU Addressing Modes

The 256 bytes of internal data memory address space is accessible using indirect addressing instructions (including stack operations). However, only the lower 128 bytes are accessible using direct addressing. The upper 128 bytes of direct address Data Memory space are used to access Extended Special Function Registers (ESFRs).

## 6.1.1 Register Banks

There are four directly addressable register banks, only one of which may be selected at one time. The register banks occupy Internal Data Memory addresses from 00 hex to 1F hex.

## 6.1.2 Bit Addressing

The 16 bytes of Internal Data Memory that occupy addresses from 20 hex to 2F hex are bit addressable. SFRs that have addresses of the form 1XXXX000 binary are also bit addressable.

## 6.1.3 External Data Memory

External data memory occupies a  $2K \times 8$  address space. This space contains the External Special Function Data Registers (ESFRs). The ESFR permit access and control of the hardware features and internal interfaces of the TAS3204.

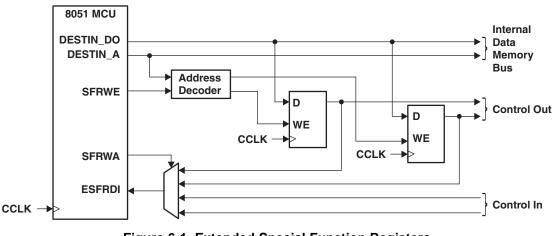

## 6.1.4 Extended Special Function Registers

ESFRs provide signals needed for the M8051 to control the different blocks in the device. ESFR is an extension to the M8051. Figure 6-1 shows how these registers are arranged.

Figure 6-1. Extended Special Function Registers

## 6.1.5 Memory Mapped Registers for DAP Data Memory

The following memory mapped registers are used for communication with the digital audio processor.

|         | -           |                                      |

|---------|-------------|--------------------------------------|

| Address | Register    | Comment                              |

| 0x0300  | Dither Seed | Sets the dither seed value           |

| 0x0301  | PC Start    | Sets the starting address of the DAP |

| 0x0302  | Reserved    | Reserved                             |

### **Table 6-1. Memory Mapped Registers**

Note that TAS3204 has the same memory mapped registers distinction of upper and lower memory for these registers.

## 6.2 Boot Up Sequence

On power up of the TAS3204 or immediatly following a reset, the slave interface is disabled and the master interface is enabled. Using the master interface, the TAS3204 automatically tests to see if an I<sup>2</sup>C EEPROM is at address 1010x. The value x can be chip select, other information, or don't cares, depending on the EEPROM selected. If an EEPROM is present and it contains the correct header information and one or more blocks of program/memory data, the TAS3204 loads the program, coefficient, and/or data memories from the EEPROM. If a EEPROM is present, the download is complete when a header is read that has a zero-length data segment. At this point, the TAS3204 disables the master I<sup>2</sup>C interface, enables the slave I<sup>2</sup>C interface, and starts normal operation.

If no EEPROM is present or if an error occurred during the EEPROM read, TAS3204 disables the master I<sup>2</sup>C interface, enables the slave I<sup>2</sup>C interface, and loads the default configuration stored in the ROM. In this default configuration, the TAS3204 streams audio from input to output if the GPIO pin is LOW.

The master and slave interfaces do not operate simultaneously.

٠

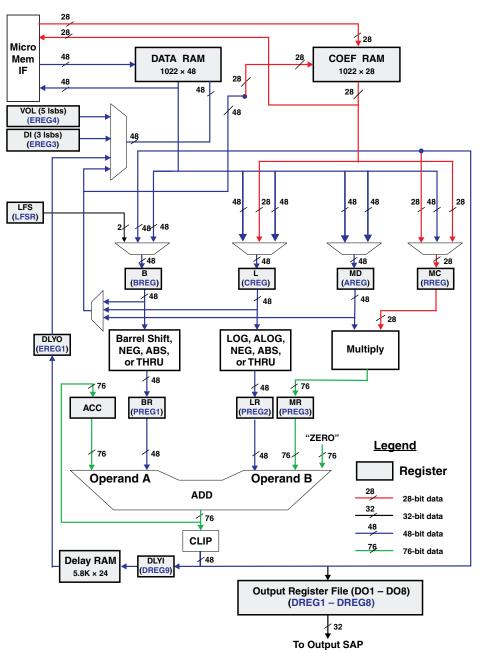

## 7 Digital Audio Processor

The DAP arithmetic unit is a fixed-point computational engine consisting of an arithmetic unit and data and coefficient memory blocks. The primary features of the DAP are:

- Two pipe parallel processing architecture

- 48-bit data path with 76-bit accumulator

- Hardware single cycle multiplier (28×48)

- Three 48-bit general-purpose data registers and one 28-bit coefficient register

- Four simultaneous operations per machine cycle

- Shift right, shift left and bi-modal clip

- Log2/Alog2

- Magnitude Truncation

- Hardware acceleration units

- Soft volume controller

- Delay memory

- Dither generator

- log2/2× estimator

- 1024 + 768 dual port ports words of data (24 and 48 bits, respectively)

- 1228 words of coefficient memory (28 bits)

- 3K word of program RAM (55 bits)

- 5.88K words of 24-bits delay memory (1.22 ms)

- Coefficient RAM, data RAM, LFSR seed, program counter, and memory pointers are all mapped into the same memory space for convenient addressing by the MCUcontroller.

- Memory interface block contains four pointers, two for data memory and two for coefficient memory.

Figure 7-1. DSP Core Block Diagram

## 7.1 Audio Digital Signal Processor Core

The audio digital signal processor core arithmetic unit is a fixed-point computational engine consisting of an arithmetic unit and data and coefficient memory blocks. The audio processing structure, which can include mixers, multiplexers, volume, bass and treble, equalizers, dynamic range compression, or third-party algorithms, is running in the DAP. The 8051 MCUcontroller has access to DAP resources such as coefficient RAM and is able to support the DAP with certain tasks; for example, a volume ramp. The primary blocks of the audio DSP core are:

- 48-bit data path with 76-bit accumulator

- DSP controller

- Memory interface

- Coefficient RAM (1K×28)

- Data RAM 24-bit upper memory (1Kx24), 48-bit lower memory (768x48)

- Program RAM (3K×55)

The DAP is discussed in detail in the following sections.

## 7.2 DAP Instructions Set

Please see this information in the TAS3xxx Audio DSP Instruction Set Reference Guide

### www.ti.com

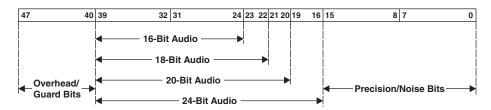

## 7.3 DAP Data Word Structure

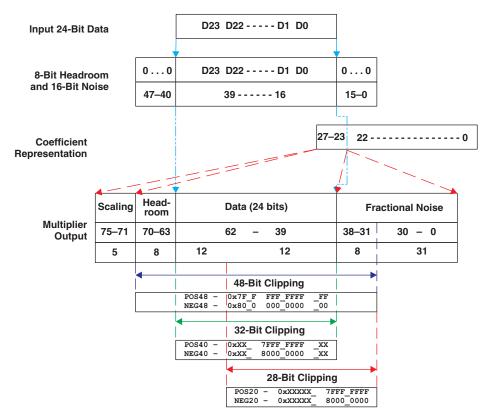

Figure 7-2 shows the data word structure of the DAP arithmetic unit. Eight bits of overhead or guard bits are provided at the upper end of the 48-bit DAP word, and 16 bits of computational precision or noise bits are provided at the lower end of the 48-bit word. The incoming digital audio words are all positioned with the most significant bit abutting the 8-bit overhead/guard boundary. The sign bit in bit 39 indicates that all incoming audio samples are treated as signed data samples The arithmetic engine is a 48-bit (25.23 format) processor consisting of a general-purpose 76-bit arithmetic logic unit and function-specific arithmetic blocks. Multiply operations (excluding the function-specific arithmetic blocks) always involve 48-bit DAP words and 28-bit coefficients (usually I<sup>2</sup>C programmable coefficients). If a group of products is to be added together, the 76-bit product of each multiplication is applied to a 76-bit adder, where a DSP-like multiply-accumulate (MAC) operation takes place. Biquad filter computations use the MAC operation to maintain precision in the intermediate computational stages.

Figure 7-2. Arithmetic Unit Data Word Structure

To maximize the linear range of the 76-bit ALU, saturation logic is not used. In MAC computations, intermediate overflows are permitted, and it is assumed that subsequent terms in the computation flow correct the overflow condition (see Figure 7-3). The DAP memory banks include a dual port data RAM for storing intermediate results, a coefficient RAM, and a fixed program ROM. Only the coefficient RAM, assessable via the  $l^2C$  bus, is available to the user.

|          |   | 1 | 0           | 1 | 1       | 0       | 1       | 1 | 1           | (-73)  | -   | 73  |

|----------|---|---|-------------|---|---------|---------|---------|---|-------------|--------|-----|-----|

|          | + | 1 | <br>  1<br> | 0 | 0       | 1<br>   | 1<br>   | 0 | <br>  1<br> | (-51)  | + · | -51 |

|          |   | 1 | 0           | 0 | 0       | 0       | <br>  1 | 0 | 0           | (-124) | -1  | 24  |

|          | + | 1 | <b>1</b>    | 0 | 1       | 0       | 0       | 1 | <b>1</b>    | (-45)  | + - | 45  |

| Rollover | [ | 0 | 1           | 0 | 1       | 0       | 1       | 1 | 1           | (57)   |     | 57  |

|          | + | 0 | 0           | 1 | 1       | 1       | 0       | 1 | 1           | (59)   | +   | 59  |

|          |   | 1 | 0           | 0 | <br>  1 | <br>  0 | 0       | 1 | 0           | (-110) | -1  | 10  |

Figure 7-3. DSP ALU Operation With Intermediate Overflow

# TAS3204

SLES197C-APRIL 2007-REVISED MARCH 2011

www.ti.com

Figure 7-4. DAP Data-Path Data Representation

## 8 I<sup>2</sup>C Control Interface

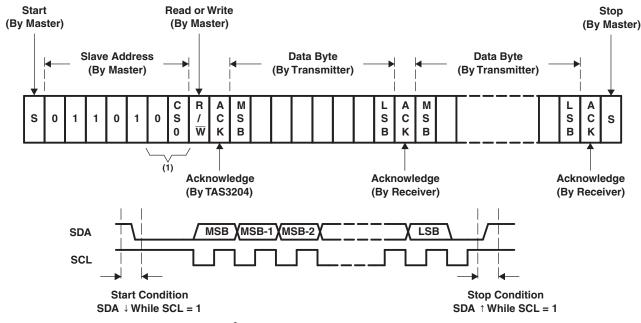

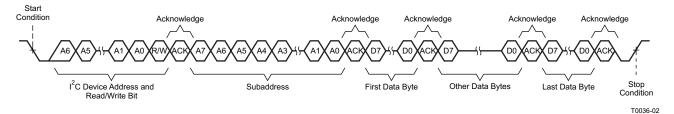

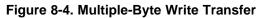

The TAS3204 also two I<sup>2</sup>C interfaces that is compatible with the I<sup>2</sup>C bus protocol. The Master I<sup>2</sup>C supports 375-kbps data transfer rates for multiple 4-byte write and read operations (maximum is 20 bytes). The master I<sup>2</sup>C interface is used to load program and data from an external I<sup>2</sup>C EEPROM. The slave I<sup>2</sup>C interface supports both 100 kbps and 400 kbps data transfer rates for multiply 4 byte write and read operations (maximum 20 bytes). The slave I<sup>2</sup>C interface is used to program the registers of the device or to read the device status registers. Additionally, the slave I<sup>2</sup>C can be used to replace the information loaded by the I<sup>2</sup>C master interface.

## 8.1 General I<sup>2</sup>C Operations

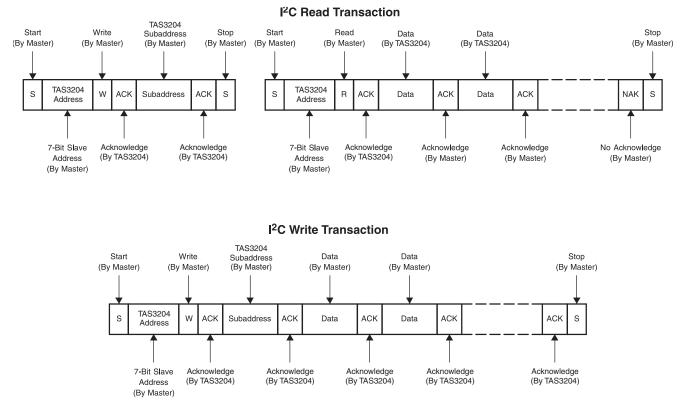

The I<sup>2</sup>C bus employs two signals, SDA (serial data) and SCL (serial clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially one bit at a time. The address and data are transferred in byte (8-bit) format with the most-significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a start condition on the bus and ends with the master device driving a start conditions. A HIGH-to-LOW transition on SDA while the clock is HIGH to indicate a start and stop conditions. A HIGH-to-LOW transition smust occur within the low time of the clock period. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The slave holds SDA LOW during acknowledge clock period to indicate an acknowledgement. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (one byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pullup resistor must be used for the SDA and SCL signals to set the HIGH level for the bus.

There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. Figure 8-1 shows the TAS3204 read and write operation sequences.

As shown in Figure 8-1, an  $I^2C$  read transaction requires that the master device first issue a write transaction to give the TAS3204 the subaddress to be used in the read transaction that follows. This subaddress assignment write transaction is then followed by the read transaction. For write transactions, the subaddress is supplied in the first byte of data written, and this byte is followed by the data to be written. For  $I^2C$  write transactions, the subaddress must always be included in the data written. There cannot be a separate write transaction to supply the subaddress, as was required for read transactions. If a subaddress-assignment-only write transaction is followed by a second write transaction supplying the data, erroneous behavior results. The first byte in the second write transaction is interpreted by the TAS3204 as another subaddress replacing the one previously written.

# TAS3204

Texas Instruments

## SLES197C-APRIL 2007-REVISED MARCH 2011

www.ti.com

Figure 8-1. I<sup>2</sup>C Subaddress Access Protocol

## 8.2 I<sup>2</sup>C Master Interface

IIn the master mode, the I<sup>2</sup>C bus is used to:.

- Load the program and coefficient data

- MCU program memory

- MCU extended memory

- Audio DSP core program memory

- Audio DSP core coefficient memory

- Audio DSP core data memory

The TAS3204, when operating as an I<sup>2</sup>C master, can execute a complete download of any internal memory or any section of any internal memory without requiring any wait states.

When the TAS3204 operates as an I<sup>2</sup>C master, the TAS3204 generates a repeated start without an intervening stop command while downloading program and memory data from EEPROM. When a repeated start is sent to the EEPROM in read mode, the EEPROM enters a sequential read mode to transfer large blocks of data quickly.

The first action of the TAS3204 as master is to transmit a start condition along with the device address of the I<sup>2</sup>C EEPROM with the read/write bit cleared (0) to indicate a write. The EEPROM acknowledges the address byte, and the TAS3204 sends a subaddress byte, which the EEPROM acknowledges. Most EEPROMs have at least 2-byte addresses and acknowledge as many as are appropriate. At this point, the EEPROM sends a last acknowledge and becomes a slave transmitter. The TAS3204 acknowledges each byte repeatedly to continue reading each data byte that is stored in memory.

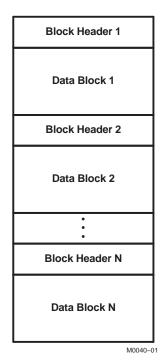

The memory load information starts with reading the header and data information that starts at subaddress 0 of the EEPROM. This information must then be stored in sequential memory addresses with no intervening gaps. The data blocks are contiguous blocks of data that immediately follow the header locations.

### SLES197C-APRIL 2007-REVISED MARCH 2011

The TAS3204 memory data can be stored and loaded in (almost) any order. Additionally, this addressing scheme permits portions of the TAS3204 internal memories to be loaded.

### I<sup>2</sup>C EEPROM Memory Map

Figure 8-2. EEPROM Address Map

The TAS3204 sequentially reads EEPROM memory and loads its internal memory unless it does not find a valid memory header block, is not able to read the next memory location because the end of memory was reached, detects a checksum error, or reads an end-of-program header block. When it encounters an invalid header or read error, the TAS3204 attempts to read the header or memory location three times before it determines that it has an error. If the TAS3204 encounters a checksum error it attempts to reread the entire block of memory two more times before it determines that it has an error.

Once the MCU program memory has been loaded, it cannot be reloaded until the TAS3204 has been reset.

If an error is encountered, TAS3204 terminates its memory-load operation, loads the default configuration, and disables further master I<sup>2</sup>C bus operations.

If an end-of-program data block is read, the TAS3204 has completed the initial program load.

The I<sup>2</sup>C master mode uses the starting and ending I<sup>2</sup>C checksums to verify a proper EEPROM download. The first 16-bit data word received from the EEPROM, the I<sup>2</sup>C checksum at subaddress 0x00, is stored and compared against the 16-bit data word received for the last subaddress, the ending I<sup>2</sup>C checksum, and the checksum that is computed during the download. These three values must be equal. If the read and computed values do not match, the TAS3204 sets the memory read error bits in the status register and repeats the download from the EEPROM two more times. If the comparison check fails the third time, the TAS3204 sets the MCU program to the default value.

Table 8-1 shows the format of the EEPROM or other external memory load file. Each line of the file is a byte (in ASCII format). The checksum is the summation of all the bytes (with beginning and ending checksum fields = 00). The final checksum inserted into the checksum field is the lowest significant four bytes of the checksum.

Example:

Copyright © 2007–2011, Texas Instruments Incorporated

Given the following example MCU data or program block (must be a multiple of 4 bytes for these blocks): 0x10 0x20 0x30 0x40 0x50 0x60 0x70 0x80

The checksum = 0x10 + 0x20 + 0x30 + 0x30 + 0x40 + 0x50 + 0x60 + 0x70 + 0x80 = 0x240, so

the values put in the checksum fields are MS byte = 0x02 and LS byte = 0x40.

If the checksum is >FFFFh, then the 2-byte checksum field is the least-significant 2 bytes.

For example, if the checksum is 0x1D 45B6, the checksum field is MS byte = 0x45 and LS byte = 0xB6.

#### STARTING SIZE DATA BLOCK FORMAT NOTES BYTE 12-Byte Header Block Checksum code Most Significant Byte Checksum of bytes 2 through N + 12. 0 2 Bytes If this is a termination header, this value is 00 00 Checksum code Least Significant Byte Header ID byte 1 = 0x00 Must be 0x001F for the TAS3204 to load as part of 2 2 Bytes initialization. Any other value terminates the initialization Header ID byte 2 = 0x1F memory load sequence. 0x00 - MCU program memory - or - termination header 0x01 - MCU external data memory 0x02 - Audio DSP core program memory 0x03 – Audio DSP core coefficient memory 4 Memory to be loaded 1 Byte 0x04 - Audio DSP core data memory 0x05-06 - Audio DSP upper program memory 0x07 - Audio DSP Upper Coefficient Memory 0x08-FF - Reserved for future expansion 5 0x00 Reserved 1 Byte Start TAS3204 memory address Most Significant Byte 6 2 Bytes If this is a termination header, this value is 0000. Start TAS3204 memory address Least Significant Byte Total number of bytes transferred Most Significant Byte 12 + data bytes + last checksum bytes. If this is a 2 Bytes 8 termination header, this value is 0000. Total number of bytes transferred Least Significant Byte 10 0x00 1 Byte Unused 11 0x00 1 Byte Unused Data Block for MCU Program or Data Memory (Following 12-Byte Header) Data Byte 1 (LSB) Data Byte 2 12 4 Bytes MCU Bytes 1-4 Data Byte 3 Data byte 4 (MSB) Data byte 5 Data byte 6 16 MCU Bytes 5-8 4 Bytes Data byte 7 Data byte 8 Data byte 4x(Z - 1) + 1Data byte 4x(Z - 1) + 2N + 8 4 Bytes MCU Bytes N-N+4 Data byte 4x(Z - 1) + 3Data byte 4x(Z - 1) + 4 = N

## Table 8-1. TAS3204 Master I<sup>2</sup>C Memory Block Structures

TAS3204

SLES197C-APRIL 2007-REVISED MARCH 2011

www.ti.com

Table 8-1. TAS3204 Master I<sup>2</sup>C Memory Block Structures (continued)

| STARTING<br>BYTE  | DATA BLOCK FORMAT                     | SIZE            | NOTES                                                       |  |  |

|-------------------|---------------------------------------|-----------------|-------------------------------------------------------------|--|--|

|                   | 0x00                                  |                 |                                                             |  |  |

| N + 12            | 0x00                                  | 4 Bytes         | Dependence of the star 2 through N + 11                     |  |  |

| N + 12            | Checksum code MS Byte                 | 4 bytes         | Repeated checksum bytes 2 through N + 11                    |  |  |

|                   | Checksum code LS Byte                 |                 |                                                             |  |  |

| Data Block for Au | dio DSP Core Coefficient Memory (Foll | owing 12-Byte H | leader)                                                     |  |  |

|                   | Data byte 1 (LS byte)                 |                 | Coefficient word 1 (valid data in Bit 27-Bit 0) Bit 7-Bit 0 |  |  |

| 12                | Data byte 2                           | 4 bytes         | Bit 15–Bit 8                                                |  |  |

| 12                | Data byte 3                           | 4 bytes         | Bit 23–Bit 16                                               |  |  |

|                   | Data byte 4 (MS byte)                 |                 | Bit 31–Bit 24                                               |  |  |

|                   | Data byte 5                           |                 |                                                             |  |  |

| 16                | Data byte 6                           | 1 hutaa         | Coofficient word 2                                          |  |  |

| 16                | Data byte 7                           | 4 bytes         | Coefficient word 2                                          |  |  |

|                   | Data byte 8                           |                 |                                                             |  |  |

|                   | :                                     |                 |                                                             |  |  |

|                   | Data byte 4×(Z − 1) + 1               |                 |                                                             |  |  |

|                   | Data byte $4x(Z - 1) + 2$             | 1 hutaa         | Coefficient word 7                                          |  |  |

| N + 8             | Data byte $4x(Z - 1) + 3$             | 4 bytes         | Coefficient word Z                                          |  |  |

|                   | Data byte $4x(Z - 1) + 4 = N$         |                 |                                                             |  |  |

|                   | 0x00                                  |                 |                                                             |  |  |

| N - 40            | 0x00                                  | 4 hudaa         | Demosterial characteristics of the such N + 44              |  |  |

| N + 12            | Checksum code MS byte                 | 4 bytes         | Repeated checksum bytes 2 through N + 11                    |  |  |

|                   | Checksum code LS byte                 |                 |                                                             |  |  |

| Data Block for Au | dio DSP Core Data Memory (Following   | 12-Byte Header  |                                                             |  |  |

|                   | Data byte 1 (LS byte)                 |                 | Data word 1 Bit 7–Bit 0                                     |  |  |

|                   | Data byte 2                           |                 | Bit 15–Bit 8                                                |  |  |

| 12                | Data byte 3                           | 6 hutaa         | Bit 23–Bit 16                                               |  |  |

| 12                | Data byte 4                           | 6 bytes         | Bit 31–Bit 24                                               |  |  |

|                   | Data byte 5                           |                 | Bit 39–Bit 32                                               |  |  |

|                   | Data byte 6 (MS byte)                 |                 | Bit 47–Bit 40                                               |  |  |

|                   | Data byte 7                           |                 |                                                             |  |  |

|                   | Data byte 8                           |                 |                                                             |  |  |

| 18                | Data byte 9                           | 6 bytee         | Dete 2                                                      |  |  |

| 10                | Data byte 10                          | 6 bytes         | Data 2                                                      |  |  |

|                   | Data byte 11                          |                 |                                                             |  |  |

|                   | Data byte 12                          |                 |                                                             |  |  |

|                   | :                                     |                 |                                                             |  |  |

|                   | Data byte 6×(Z – 1) + 1               |                 |                                                             |  |  |

|                   | Data byte $6x(Z - 1) + 2$             |                 |                                                             |  |  |

| NIC               | Data byte $6x(Z - 1) + 3$             | 6 hite-         | Data Z                                                      |  |  |

| N + 6             | Data byte $6 \times (Z - 1) + 4$      | 6 bytes         | Data Z                                                      |  |  |

|                   | Data byte $6 \times (Z - 1) + 5$      |                 |                                                             |  |  |

|                   |                                       |                 |                                                             |  |  |

## Table 8-1. TAS3204 Master I<sup>2</sup>C Memory Block Structures (continued)

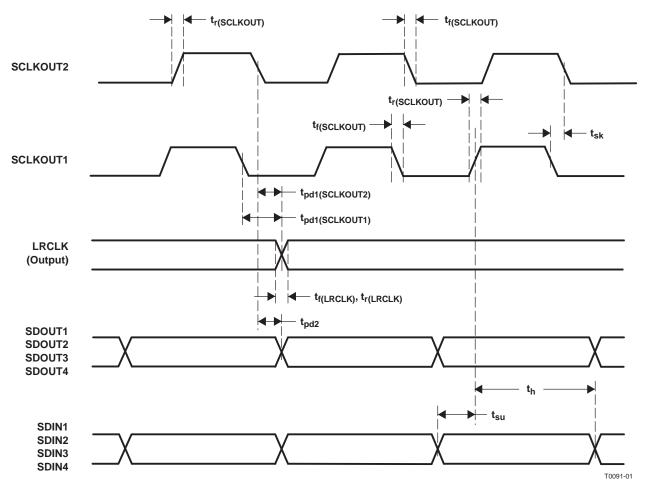

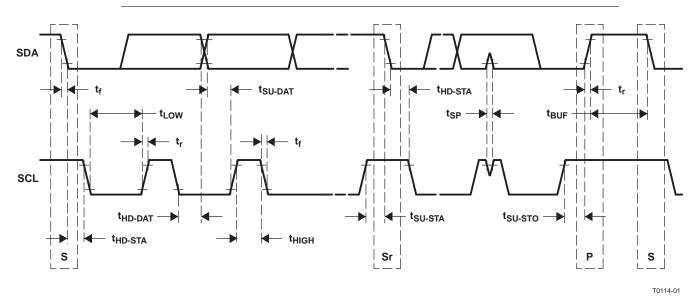

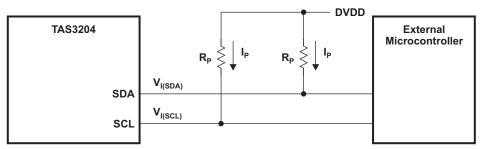

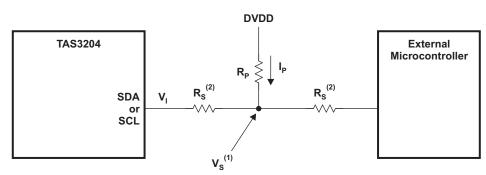

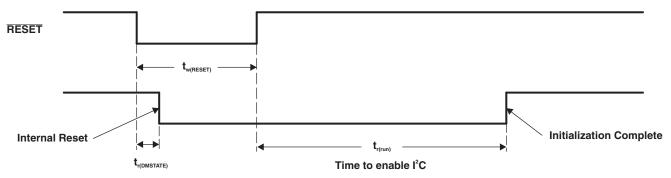

| STARTING<br>BYTE       | DATA BLOCK FORMAT                           | SIZE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NOTES                                                   |  |  |