Order

Now

TCA8418

SCPS215F-SEPTEMBER 2009-REVISED JULY 2017

Support &

Community

2.0

# TCA8418 I<sup>2</sup>C Controlled Keypad Scan IC With Integrated ESD Protection

Technical

Documents

## 1 Features

- Operating Power-Supply Voltage Range of 1.65-V to 3.6-V

- Supports 80 Buttons With Use of 18 GPIOs

- Supports QWERTY Keypad Operation Plus GPIO Expansion

- Low Standby (Idle) Current Consumption: 3 μA

- Supports 1-MHz Fast Mode Plus I<sup>2</sup>C Bus

- 10 Byte FIFO to Store 10 Key Presses and Releases

- Open-Drain Active-Low Interrupt Output

- Integrated Debounce Time of 50 μs

- Schmitt-Trigger Action Allows Slow Input Transition and Better Switching Noise Immunity at the SCL and SDA Inputs: Typical  $\rm V_{hys}$  at 1.8 V is 0.18 V

- Latch-Up Performance Exceeds 200 mA Per JESD 78, Class II

- ESD Protection Exceeds JESD 22 on all 18 GPIO Pins and non GPIO pins

- 2000-V Human Body Model (A114-A)

- 1000-V Charged Device Model (C101)

## 2 Applications

Tools &

Software

- Smart Phones

- Tablets

- HMI Panels

- GPS Devices

- MP3 Players

- Digital Cameras

## **3** Description

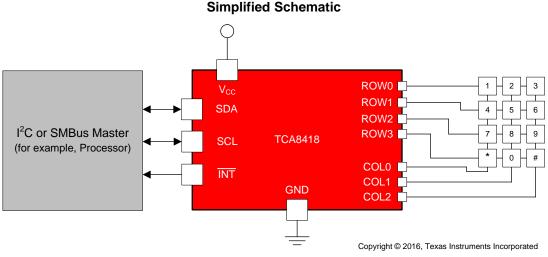

The TCA8418 is a keypad scan device with integrated ESD protection. It can operate from 1.65 V to 3.6 V and has 18 general purpose inputs/outputs (GPIO) that can be used to support up to 80 keys via the  $I^2C$  interface.

The key controller debounces inputs and maintains a 10 byte FIFO of key-press and release events which can store up to 10 keys with overflow wrap capability. An interrupt ( $\overline{INT}$ ) output can be configured to alert key presses and releases either as they occur, or at maximum rate.

#### Device Information<sup>(1)</sup>

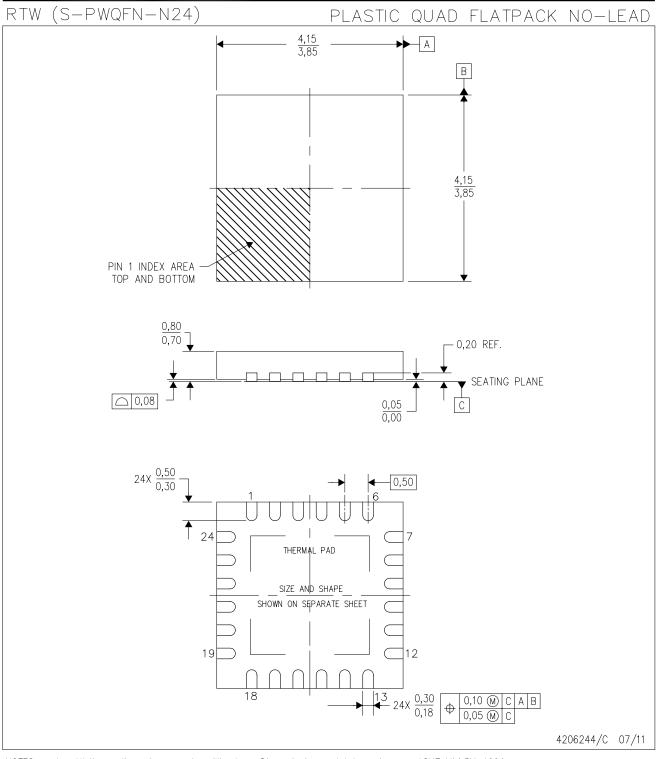

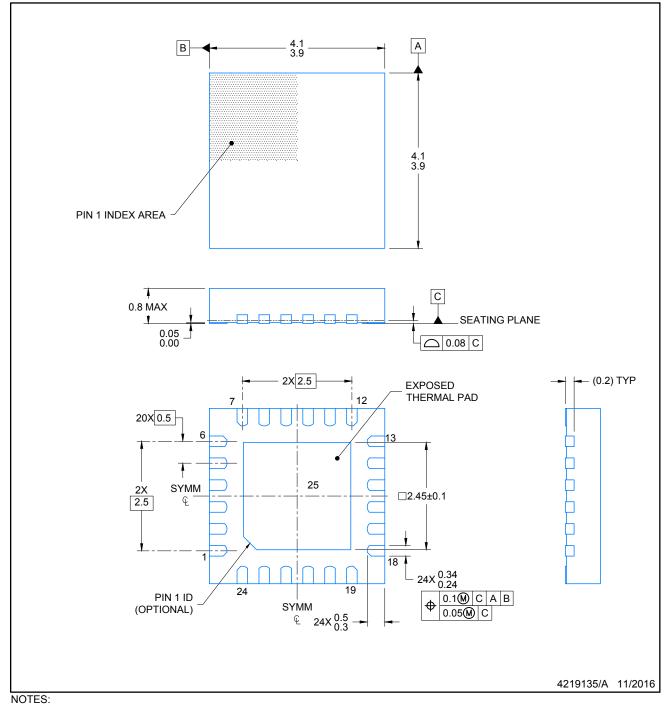

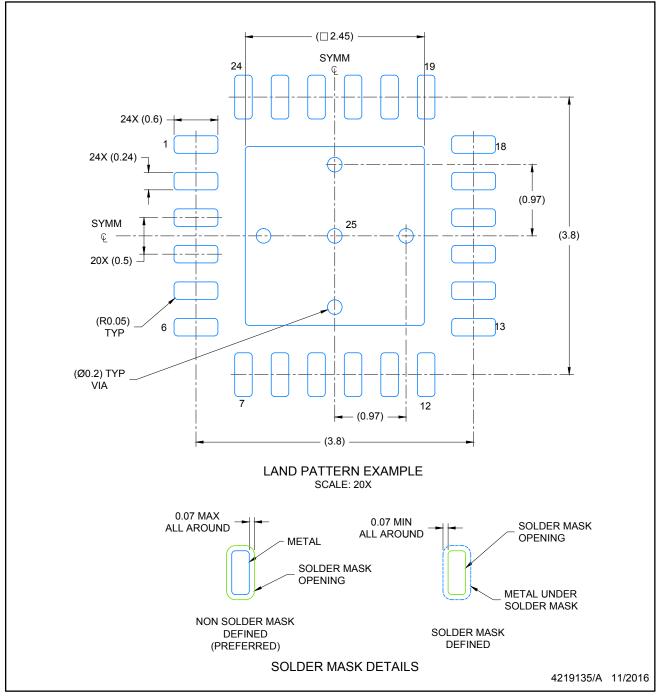

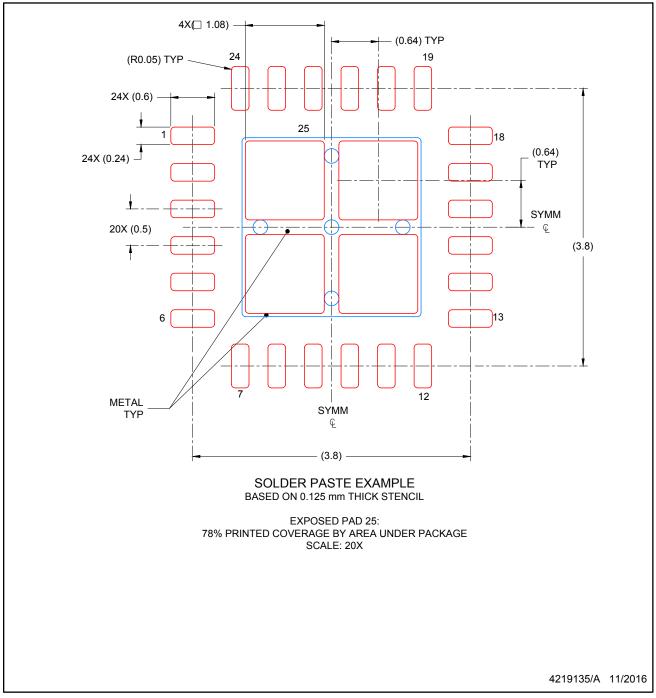

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| TCA8418     | WQFN (24) | 4.00 mm × 4.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

Only 7 GPIOs are shown out of the full 18 GPIOs

1

2

3 4

5

6

7

8

2

# **Table of Contents**

| Features 1                                         |    | 8.2 Functional Block Diagram                         | 15 |

|----------------------------------------------------|----|------------------------------------------------------|----|

| Applications 1                                     |    | 8.3 Feature Description                              | 15 |

| Description 1                                      |    | 8.4 Device Functional Modes                          | 20 |

| Revision History                                   |    | 8.5 Programming                                      | 21 |

| Pin Configuration and Functions                    |    | 8.6 Register Maps                                    | 25 |

| Specifications                                     | 9  | Application and Implementation                       | 37 |

| 6.1 Absolute Maximum Ratings                       |    | 9.1 Application Information                          | 37 |

| 6.2 ESD Ratings                                    |    | 9.2 Typical Application                              | 39 |

| 6.3 Recommended Operating Conditions               | 10 | Power Supply Recommendations                         | 42 |

| 6.4 Thermal Information                            | 11 | Layout                                               | 44 |

| 6.5 Electrical Characteristics                     |    | 11.1 Layout Guidelines                               | 44 |

| 6.6 I <sup>2</sup> C Interface Timing Requirements |    | 11.2 Layout Example                                  | 44 |

| 6.7 Reset Timing Requirements                      | 12 | Device and Documentation Support                     | 45 |

| 6.8 Switching Characteristics                      |    | 12.1 Receiving Notification of Documentation Updates | 45 |

| 6.9 Keypad Switching Characteristics               |    | 12.2 Community Resources                             | 45 |

| 6.10 Typical Characteristics 8                     |    | 12.3 Trademarks                                      | 45 |

| Parameter Measurement Information                  |    | 12.4 Electrostatic Discharge Caution                 | 45 |

| Detailed Description                               |    | 12.5 Glossary                                        | 45 |

| 8.1 Overview                                       | 13 | Mechanical, Packaging, and Orderable                 |    |

|                                                    |    | Information                                          | 45 |

|    | 8.3  | Feature Description                             | 15 |

|----|------|-------------------------------------------------|----|

|    | 8.4  | Device Functional Modes                         | 20 |

|    | 8.5  | Programming                                     | 21 |

|    | 8.6  | Register Maps                                   | 25 |

| 9  | App  | lication and Implementation                     | 37 |

|    | 9.1  | Application Information                         | 37 |

|    | 9.2  | Typical Application                             | 39 |

| 10 | Pow  | ver Supply Recommendations                      | 42 |

| 11 | Lay  | out                                             | 44 |

|    | 11.1 | Layout Guidelines                               | 44 |

|    | 11.2 | Layout Example                                  | 44 |

| 12 | Dev  | ice and Documentation Support                   | 45 |

|    | 12.1 | Receiving Notification of Documentation Updates | 45 |

|    | 12.2 | Community Resources                             | 45 |

|    | 12.3 | Trademarks                                      | 45 |

|    | 12.4 | Electrostatic Discharge Caution                 | 45 |

|    | 12.5 | Glossary                                        | 45 |

| 13 | Mec  | hanical, Packaging, and Orderable               |    |

|    | Info | mation                                          | 45 |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision E (November 2015) to Revision F

Changed the WQFN Body Size From: 4.00 mm x 3.00 mm To: 4.00 mm x 4.00 mm and deleted the DSBGA (25)

#### Changes from Revision D (July 2014) to Revision E

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section ......1

#### Changes from Revision B (March 2010) to Revision C Page

#### XAS STRUMENTS

www.ti.com

## Page

Page

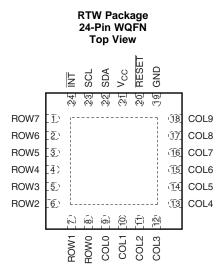

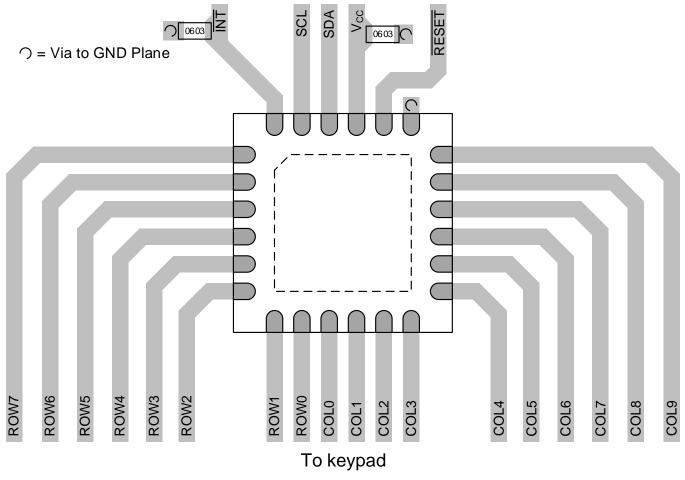

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN  |                 | ТҮРЕ | DESCRIPTION                                                                                                     |  |  |  |

|------|-----------------|------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME | NO.             | ITPE | DESCRIPTION                                                                                                     |  |  |  |

| 1    | ROW7            | I/O  | GPIO or row 7 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                      |  |  |  |

| 2    | ROW6            | I/O  | GPIO or row 6 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                      |  |  |  |

| 3    | ROW5            | I/O  | GPIO or row 5 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                      |  |  |  |

| 4    | ROW4            | I/O  | GPIO or row 4 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                      |  |  |  |

| 5    | ROW3            | I/O  | GPIO or row 3 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                      |  |  |  |

| 6    | ROW2            | I/O  | GPIO or row 2 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                      |  |  |  |

| 7    | ROW1            | I/O  | GPIO or row 1 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                      |  |  |  |

| 8    | ROW0            | I/O  | GPIO or row 0 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                      |  |  |  |

| 9    | COL0            | I/O  | GPIO or column 0 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                   |  |  |  |

| 10   | COL1            | I/O  | GPIO or column 1 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                   |  |  |  |

| 11   | COL2            | I/O  | GPIO or column 2 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                   |  |  |  |

| 12   | COL3            | I/O  | GPIO or column 3 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                   |  |  |  |

| 13   | COL4            | I/O  | GPIO or column 4 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                   |  |  |  |

| 14   | COL5            | I/O  | GPIO or column 5 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                   |  |  |  |

| 15   | COL6            | I/O  | GPIO or column 6 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                   |  |  |  |

| 16   | COL7            | I/O  | GPIO or column 7 in keypad matrix. If unused, connect to $V_{\mbox{CC}}$ through a pull-up resistor.            |  |  |  |

| 17   | COL8            | I/O  | GPIO or column 8 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                   |  |  |  |

| 18   | COL9            | I/O  | GPIO or column 9 in keypad matrix. If unused, connect to $V_{CC}$ through a pull-up resistor.                   |  |  |  |

| 19   | GND             | -    | Ground                                                                                                          |  |  |  |

| 20   | RESET           | I    | Active-low reset input. Connect to V <sub>CC</sub> through a pull-up resistor, if no active connection is used. |  |  |  |

| 21   | V <sub>CC</sub> | -    | Supply voltage of 1.65 V to 3.6 V                                                                               |  |  |  |

| 22   | SDA             | I/O  | Serial data bus. Connect to $V_{CC}$ through a pull-up resistor.                                                |  |  |  |

| 23   | SCL             | I    | Serial clock bus. Connect to V <sub>CC</sub> through a pull-up resistor.                                        |  |  |  |

| 24   | INT             | 0    | Active-low interrupt output. Open drain structure. Connect to $V_{CC}$ through a pull-up resistor.              |  |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  |                                                              |                                                                                             |                         | MIN  | MAX | UNIT |

|------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------|------|-----|------|

| $V_{CC}$         | Supply voltage range                                         |                                                                                             |                         | -0.5 | 4.6 | V    |

| VI               | Input voltage range <sup>(2)</sup>                           |                                                                                             |                         | -0.5 | 4.6 | V    |

| V                | Voltage range applied to any output                          | Voltage range applied to any output in the high-impedance or power-off state <sup>(2)</sup> |                         |      | 4.6 | V    |

| Vo               | Output voltage range in the high or low state <sup>(2)</sup> |                                                                                             |                         | -0.5 | 4.6 | V    |

| I <sub>IK</sub>  | Input clamp current                                          | V <sub>I</sub> < 0                                                                          | V <sub>1</sub> < 0      |      | ±20 | mA   |

| I <sub>OK</sub>  | Output clamp current                                         | V <sub>0</sub> < 0                                                                          | V <sub>O</sub> < 0      |      | ±20 | mA   |

|                  |                                                              | P port, SDA                                                                                 |                         |      | 50  |      |

| IOL              | Continuous output Low current                                | INT                                                                                         | $V_0 = 0$ to $V_{CC}$   |      | 25  | mA   |

| I <sub>OH</sub>  | Continuous output High current                               | P port                                                                                      | $V_{O} = 0$ to $V_{CC}$ |      | 50  |      |

| T <sub>stg</sub> | Storage temperature range                                    |                                                                                             |                         | -65  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

#### 6.2 ESD Ratings

|                    |                         |                                                                                        | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>            | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins $^{\rm (2)}$ | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

|                 |                                |                                 | MIN                 | MAX                 | UNIT |

|-----------------|--------------------------------|---------------------------------|---------------------|---------------------|------|

| V <sub>CC</sub> | Supply voltage                 | 1.65                            | 3.6                 | V                   |      |

| VIH             | High-level input voltage       | SCL, SDA, ROW0–7, COL0–9, RESET | $0.7 \times V_{CC}$ | 3.6                 | V    |

| V <sub>IL</sub> | Low-level input voltage        | SCL, SDA, ROW0–7, COL0–9, RESET | -0.5                | $0.3 \times V_{CC}$ | V    |

| I <sub>OH</sub> | High-level output current      | ROW0–7, COL0–9                  |                     | 10                  | mA   |

| I <sub>OL</sub> | Low-level output current       | ROW0–7, COL0–9                  |                     | 25                  | mA   |

| T <sub>A</sub>  | Operating free-air temperature |                                 | -40                 | 85                  | °C   |

#### 6.4 Thermal Information

|                       |                                              | TCA8418    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTW (WQFN) | UNIT |

|                       |                                              | 24 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 38.9       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 40.6       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 17.2       | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.9        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 17.2       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 6.6        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 6.5 Electrical Characteristics

over recommended operating free-air temperature range,  $V_{CC}$  = 1.65 V to 3.6 V (unless otherwise noted)

|                       | PARAMETER                                          | TE                                         | ST CONDITIONS               |                                    | V <sub>cc</sub> | MIN  | TYP MAX | UNIT |

|-----------------------|----------------------------------------------------|--------------------------------------------|-----------------------------|------------------------------------|-----------------|------|---------|------|

| V <sub>IK</sub>       | Input diode clamp voltage                          | I <sub>I</sub> = -18 mA                    |                             |                                    | 1.65 V to 3.6 V | -1.2 |         | V    |

| V <sub>POR</sub><br>r | Power-on reset voltage, $V_{CC}$ rising            | V <sub>I</sub> = V <sub>CC</sub> or GND, I | 0                           |                                    | 1.65 V to 3.6 V | 1.03 | 1.43    | V    |

| V <sub>POR</sub>      | Power-on reset voltage, V <sub>CC</sub><br>falling |                                            | 1.03 V 10 3.0 V             | 0.76                               | 1.15            | v    |         |      |

|                       |                                                    | $I_{OH} = -1 \text{ mA}$                   |                             |                                    | 1.65 V          | 1.25 |         |      |

| V <sub>OH</sub>       |                                                    |                                            |                             |                                    | 1.65 V          | 1.2  |         |      |

|                       |                                                    | $I_{OH} = -8 \text{ mA}$                   |                             |                                    | 2.3 V           | 1.8  |         |      |

|                       | ROW0–7, COL0–9 high-level<br>output voltage        |                                            |                             |                                    | 3 V             | 2.6  |         | V    |

|                       | ealpai rellage                                     |                                            |                             |                                    | 1.65 V          | 1.1  |         |      |

|                       |                                                    | I <sub>OH</sub> = -10 mA                   |                             |                                    | 2.3 V           | 1.7  |         |      |

|                       |                                                    |                                            |                             |                                    | 3 V             | 2.5  |         |      |

|                       |                                                    | I <sub>OL</sub> = 1 mA                     |                             |                                    | 1.65 V          |      | 0.4     |      |

|                       |                                                    |                                            |                             |                                    | 1.65 V          |      | 0.45    |      |

|                       |                                                    | I <sub>OL</sub> = 8 mA                     |                             |                                    | 2.3 V           |      | 0.25    |      |

| / <sub>OL</sub>       | ROW0-7, COL0-9 low-level<br>output voltage         |                                            |                             |                                    | 3 V             |      | 0.25    | V    |

|                       |                                                    | I <sub>OL</sub> = 10 mA                    |                             | 1.65 V                             |                 | 0.6  |         |      |

|                       |                                                    |                                            |                             | 2.3 V                              |                 | 0.3  |         |      |

|                       |                                                    |                                            |                             |                                    |                 |      | 0.25    |      |

|                       | SDA                                                | V <sub>OL</sub> = 0.4 V                    |                             |                                    |                 | 3    |         |      |

| OL                    | INT and CAD_INT                                    | V <sub>OL</sub> = 0.4 V                    |                             |                                    | 1.65 V to 3.6 V | 3    |         | mA   |

| I                     | SCL, SDA, ROW0–7, COL0–9,<br>RESET                 | $V_{I} = V_{CCI}$ or GND                   |                             |                                    | 1.65 V to 3.6 V |      | 1       | μA   |

| R <sub>INT</sub>      | Internal pull-up resistor value                    | ROW0-7, COL0-9                             | )                           |                                    |                 |      | 105     | kΩ   |

|                       |                                                    |                                            | f <sub>SCL</sub> = 0 kHz    | Oscillator<br>OFF                  | 1.65 V to 3.6 V |      | 10      |      |

|                       |                                                    |                                            |                             | Oscillator<br>ON                   |                 |      | 18      |      |

|                       |                                                    |                                            | f <sub>SCL</sub> = 400 kHz  |                                    | 1.65 V          |      | 50      | -    |

|                       |                                                    | V <sub>I</sub> on SDA,                     | -30L -00 - 11 -             | 1 key press                        | 3.6 V           |      | 90      | -    |

|                       |                                                    | ROW0–7,                                    | f <sub>SCL</sub> = 1 MHz    |                                    | 1.65 V          |      | 65      | -    |

| сс                    | Supply current                                     | $COL0-9 = V_{CC}$ or $GND$ ,               |                             |                                    | 3.6 V           |      | 153     | μA   |

|                       |                                                    | $I_{O} = 0, I/O =$                         | $f_{SCL} = 400 \text{ kHz}$ | GPI low                            |                 |      | 55      | 4    |

|                       |                                                    | inputs,                                    | f <sub>SCL</sub> = 1 MHz    | (pull-up<br>enable) <sup>(1)</sup> | -               |      | 65      | -    |

|                       |                                                    |                                            | f <sub>SCL</sub> = 400 kHz  | GPI low                            | 1.65 V to 3.6 V |      | 15      |      |

|                       |                                                    |                                            | f <sub>SCL</sub> = 1 MHz    | (pull-up<br>disable)               | 1.00 1 10 0.0 1 |      | 24      |      |

|                       |                                                    |                                            | f <sub>SCL</sub> = 400 kHz  | 1 GPO                              |                 |      | 55      | -    |

|                       |                                                    |                                            | f <sub>SCL</sub> = 1 MHz    | active                             |                 |      | 65      |      |

| 2                     | SCL                                                | $V_I = V_{CCI}$ or GND                     |                             |                                    | 1.65 V to 3.6 V |      | 6 8     | pF   |

| -, -                  | SDA                                                |                                            |                             |                                    | 165 1/ +0 26 1/ |      | 10 12.5 | ᆔ    |

| C <sub>io</sub>       | ROW0-7, COL0-9                                     | $V_{IO} = V_{CC}$ or GND                   |                             |                                    | 1.65 V to 3.6 V |      | 56      | pF   |

(1) Assumes that one GPIO is enabled.

SCPS215F-SEPTEMBER 2009-REVISED JULY 2017

www.ti.com

STRUMENTS

EXAS

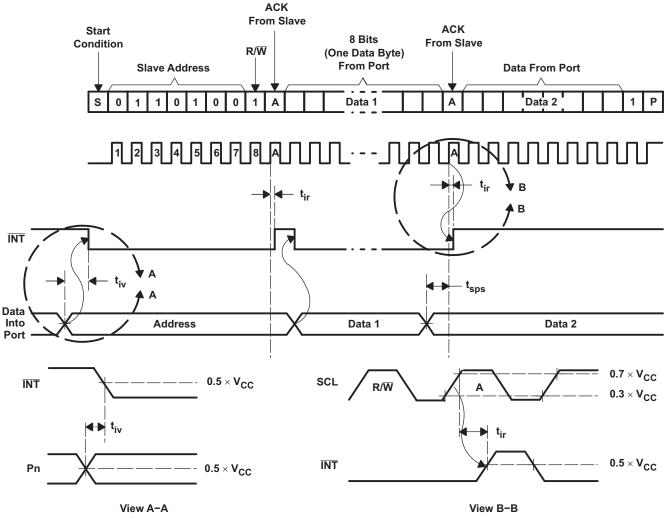

## 6.6 I<sup>2</sup>C Interface Timing Requirements

over recommended operating free-air temperature range (unless otherwise noted) (see Figure 16)

|                       |                                                                            | STANDARD I<br>I <sup>2</sup> C BUS |      | FAST MODE<br>I <sup>2</sup> C BUS     |     | FAST MODE PLUS (FM+)<br>I <sup>2</sup> C BUS |      | UNIT |

|-----------------------|----------------------------------------------------------------------------|------------------------------------|------|---------------------------------------|-----|----------------------------------------------|------|------|

|                       |                                                                            | MIN                                | MAX  | MIN                                   | MAX | MIN                                          | MAX  |      |

| f <sub>scl</sub>      | I <sup>2</sup> C clock frequency                                           | 0                                  | 100  | 0                                     | 400 | 0                                            | 1000 | kHz  |

| t <sub>sch</sub>      | I <sup>2</sup> C clock high time                                           | 4                                  |      | 0.6                                   |     | 0.26                                         |      | μS   |

| t <sub>scl</sub>      | I <sup>2</sup> C clock low time                                            | 4.7                                |      | 1.3                                   |     | 0.5                                          |      | μS   |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                                                |                                    | 50   |                                       | 50  |                                              | 50   | ns   |

| t <sub>sds</sub>      | I <sup>2</sup> C serial data setup time                                    | 250                                |      | 100                                   |     | 50                                           |      | ns   |

| t <sub>sdh</sub>      | I <sup>2</sup> C serial data hold time                                     | 0                                  |      | 0                                     |     | 0                                            |      | ns   |

| t <sub>icr</sub>      | I <sup>2</sup> C input rise time                                           |                                    | 1000 | $20 + 0.1C_{b}$ <sup>(1)</sup>        | 300 |                                              | 120  | ns   |

| t <sub>icf</sub>      | I <sup>2</sup> C input fall time                                           |                                    | 300  | 20 + 0.1C <sub>b</sub> <sup>(1)</sup> | 300 |                                              | 120  | ns   |

| t <sub>ocf</sub>      | I <sup>2</sup> C output fall time; 10 pF to 400 pF bus                     |                                    | 300  | 20 + 0.1C <sub>b</sub> <sup>(1)</sup> | 300 |                                              | 120  | μS   |

| t <sub>buf</sub>      | I <sup>2</sup> C bus free time between Stop and Start                      | 4.7                                |      | 1.3                                   |     | 0.5                                          |      | μS   |

| t <sub>sts</sub>      | I <sup>2</sup> C Start or repeater Start condition setup time              | 4.7                                |      | 0.6                                   |     | 0.26                                         |      | μS   |

| t <sub>sth</sub>      | I <sup>2</sup> C Start or repeater Start condition hold time               | 4                                  |      | 0.6                                   |     | 0.26                                         |      | μS   |

| t <sub>sps</sub>      | I <sup>2</sup> C Stop condition setup time                                 | 4                                  |      | 0.6                                   |     | 0.26                                         |      | μS   |

| t <sub>vd(data)</sub> | Valid data time; SCL low to SDA output valid                               |                                    | 1    |                                       | 0.9 |                                              | 0.45 | μS   |

| t <sub>vd(ack)</sub>  | Valid data time of ACK condition; ACK signal from SCL low to SDA (out) low |                                    | 1    |                                       | 0.9 |                                              | 0.45 | μS   |

(1)  $C_b$  = total capacitance of one bus line in pF

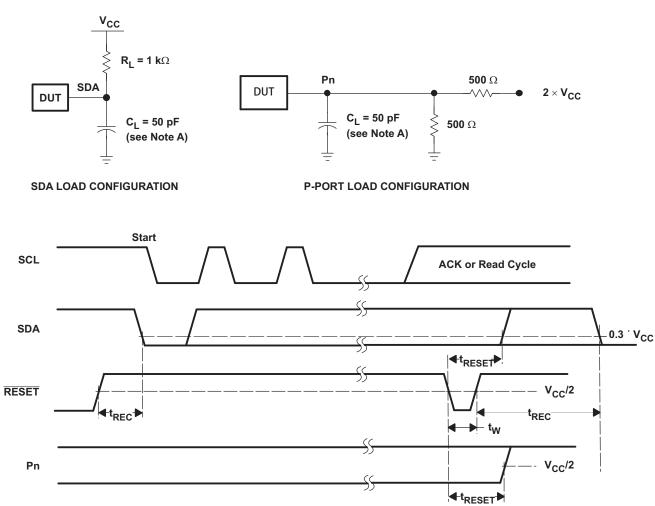

#### 6.7 Reset Timing Requirements

over recommended operating free-air temperature range (unless otherwise noted) (see Figure 19)

|                    |                      | STANDARD MODE, FAST<br>MODE, FAST MODE PLUS<br>(FM+)<br>I <sup>2</sup> C BUS | UNIT |

|--------------------|----------------------|------------------------------------------------------------------------------|------|

|                    |                      | MIN MAX                                                                      | Ī    |

| t <sub>W</sub>     | Reset pulse duration | 120 <sup>(1)</sup>                                                           | μS   |

| t <sub>REC</sub>   | Reset recovery time  | 120 <sup>(1)</sup>                                                           | μS   |

| t <sub>RESET</sub> | Time to reset        | 120 <sup>(1)</sup>                                                           | μS   |

(1) The GPIO debounce circuit uses each GPIO input which passes through a two-stage register circuit. Both registers are clocked by the same clock signal, presumably free-running, with a nominal period of 50 µs. When an input changes state, the new state is clocked into the first stage on one clock transition. On the next same-direction transition, if the input state is still the same as the previously clocked state, the signal is clocked into the second stage, and then on to the remaining circuits. Since the inputs are asynchronous to the clock, it will take anywhere from zero to 50 µs after the input transition to clock the signal into the first stage. Therefore, the total debounce time may be as long as 100 µs. Finally, to account for a slow clock, the spec further guard-banded at 120 µs.

## 6.8 Switching Characteristics

| PARAMETER       |                            | FROM                                   | то                | STANDARD MODE,<br>FAST MODE, FAST<br>MODE PLUS (FM+)<br>I <sup>2</sup> C BUS |     | UNIT |    |

|-----------------|----------------------------|----------------------------------------|-------------------|------------------------------------------------------------------------------|-----|------|----|

|                 |                            |                                        |                   |                                                                              | MIN | MAX  |    |

|                 |                            | Key event or Key<br>unlock or Overflow |                   | ĪNT                                                                          | 20  | 60   |    |

| t <sub>IV</sub> | Interrupt valid time       | GPI_INT with<br>Debounce_DIS_Low       | ROW0–7,<br>COL0–9 |                                                                              | 40  | 120  | μS |

|                 |                            | GPI_INT with<br>Debounce_DIS_High      |                   |                                                                              | 10  | 30   |    |

| t <sub>IR</sub> | Interrupt reset delay time |                                        | SCL               | INT                                                                          |     | 200  | ns |

| t <sub>PV</sub> | Output data valid          |                                        | SCL               | ROW0–7,<br>COL0–9                                                            |     | 400  | ns |

| t <sub>PS</sub> | Input data setup time      |                                        | P port            | SCL                                                                          | 0   |      | ns |

| t <sub>PH</sub> | Input data hold time       |                                        | P port            | SCL                                                                          | 300 |      | ns |

## 6.9 Keypad Switching Characteristics

| PARAMETER                      | STANDARD MODE, FAST MODE, FAST<br>MODE PLUS (FM+)<br>I <sup>2</sup> C BUS | UNIT |  |

|--------------------------------|---------------------------------------------------------------------------|------|--|

|                                | MIN MAX                                                                   |      |  |

| Key press to detection delay   | 25                                                                        | μs   |  |

| Key release to detection delay | 25                                                                        | μs   |  |

| Keypad unlock timer            | 7                                                                         | S    |  |

| Keypad interrupt mask timer    | 31                                                                        | s    |  |

| Debounce                       | 60                                                                        | ms   |  |

**TCA8418**

SCPS215F-SEPTEMBER 2009-REVISED JULY 2017

TEXAS INSTRUMENTS

www.ti.com

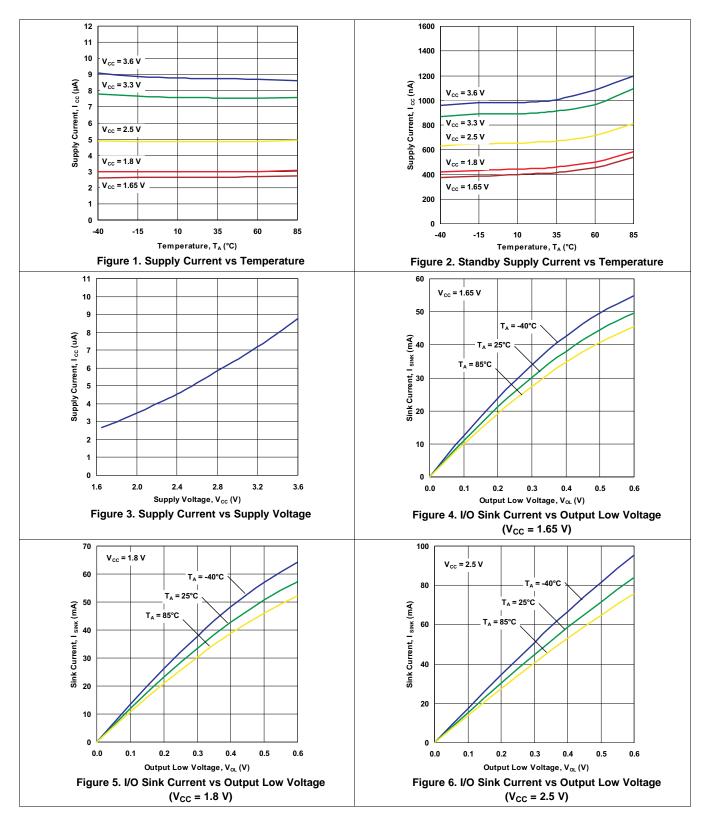

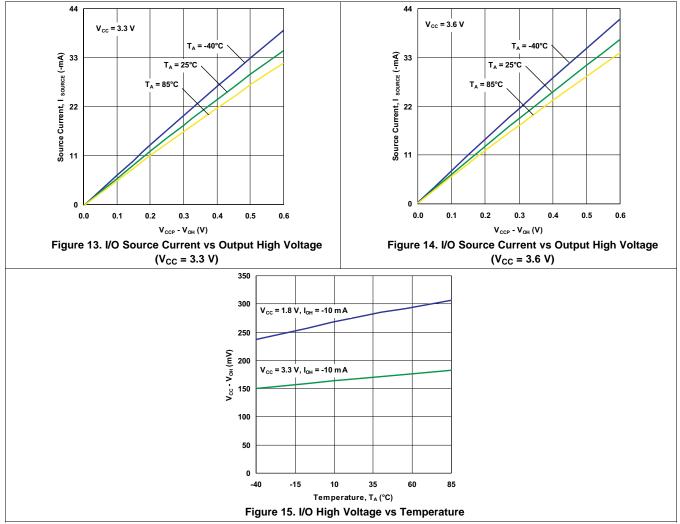

## 6.10 Typical Characteristics

$T_A = 25^{\circ}C$  (unless otherwise noted)

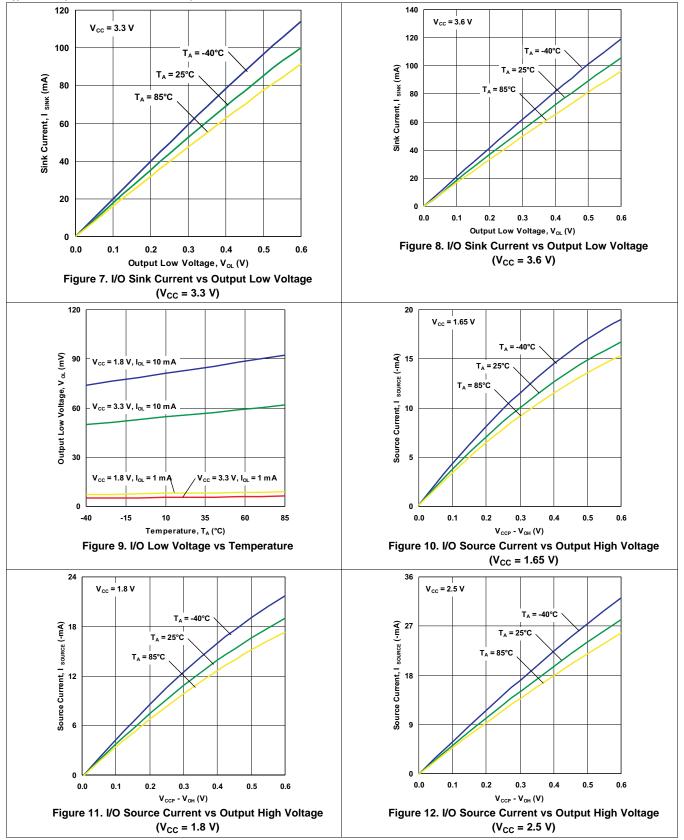

#### **Typical Characteristics (continued)**

$T_A = 25^{\circ}C$  (unless otherwise noted)

Copyright © 2009–2017, Texas Instruments Incorporated

## **Typical Characteristics (continued)**

$T_A = 25^{\circ}C$  (unless otherwise noted)

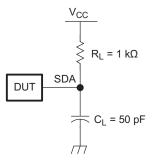

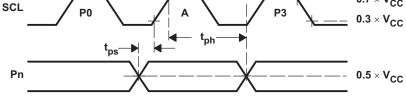

## 7 Parameter Measurement Information

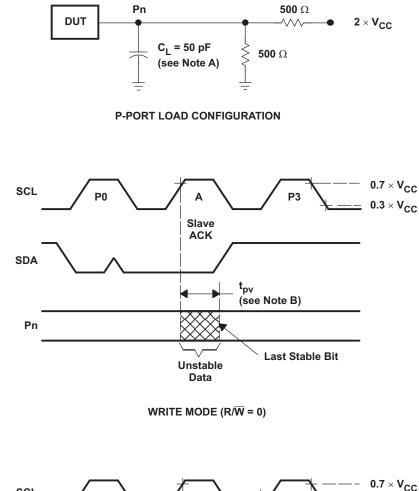

#### SDA LOAD CONFIGURATION

| BYTE | DESCRIPTION              |

|------|--------------------------|

| 1    | I <sup>2</sup> C address |

| 2, 3 | P-port data              |

- A.  $C_L$  includes probe and jig capacitance.  $t_{ocf}$  is measured with  $C_L$  of 10 pF or 400 pF.

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>0</sub> = 50  $\Omega$ , t<sub>r</sub>/t<sub>f</sub>  $\leq$  30 ns.

- C. All parameters and waveforms are not applicable to all devices.

## Figure 16. I<sup>2</sup>C Interface Load Circuit And Voltage Waveforms

NSTRUMENTS

Texas

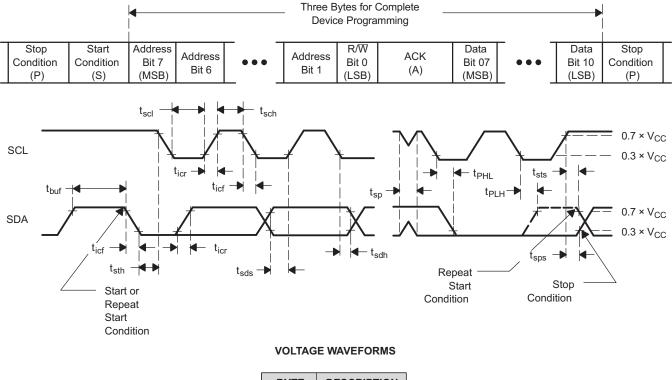

## Parameter Measurement Information (continued)

#### INTERRUPT LOAD CONFIGURATION

A. C<sub>L</sub> includes probe and jig capacitance.

B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>0</sub> = 50  $\Omega$ , t<sub>r</sub>/t<sub>f</sub>  $\leq$  30 ns.

C. All parameters and waveforms are not applicable to all devices.

#### Figure 17. Interrupt Load Circuit And Voltage Waveforms

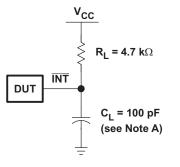

#### **Parameter Measurement Information (continued)**

#### READ MODE (R/W = 1)

- A. C<sub>L</sub> includes probe and jig capacitance.

- B.  $t_{pv}$  is measured from 0.7 × V<sub>CC</sub> on SCL to 50% I/O (Pn) output.

- C. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>0</sub> = 50  $\Omega$ , t<sub>r</sub>/t<sub>f</sub>  $\leq$  30 ns.

- D. The outputs are measured one at a time, with one transition per measurement.

- E. All parameters and waveforms are not applicable to all devices.

#### Figure 18. P Port Load Circuit And Timing Waveforms

INSTRUMENTS

EXAS

www.ti.com

#### **Parameter Measurement Information (continued)**

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z<sub>0</sub> = 50  $\Omega$ , t<sub>r</sub>/t<sub>f</sub>  $\leq$  30 ns.

- C. The outputs are measured one at a time, with one transition per measurement.

- D. I/Os are configured as inputs.

- E. All parameters and waveforms are not applicable to all devices.

#### Figure 19. Reset Load Circuits And Voltage Waveforms

## 8 Detailed Description

#### 8.1 Overview

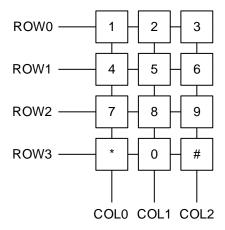

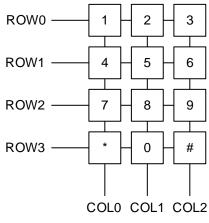

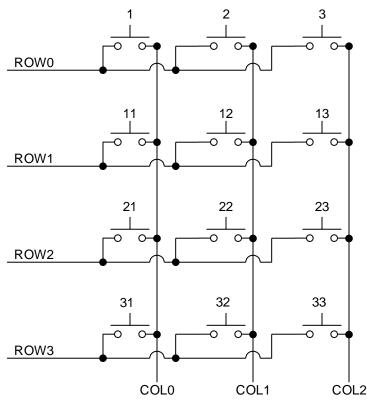

The TCA8418 supports up to 10 columnsTable 9 by 8 rows of keys, up to 80 keys. Any combination of these rows and columns can be configured to be added to the keypad matrix. This is done by setting the appropriate rows and columns to a value of 1 in the corresponding KP\_GPIO registers (seen in ). Once the rows and columns that are connected to the keypad matrix are added to the keypad array, then the TCA8418 will begin monitoring the keypad array, and any configured general purpose inputs (GPIs).

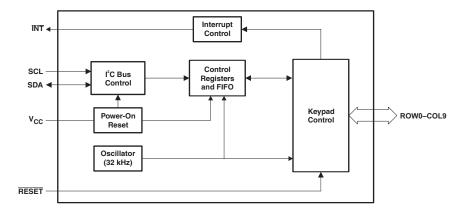

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Key Events

#### 8.3.1.1 Key Event Table

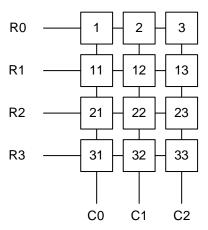

The TCA8418 can be configured to support many different configurations of keypad setups. All 18 GPIOs for the rows and columns can be used to support up to 80 keys in a key pad array. Another option is that all 18 GPIOs be used for GPIs to read 18 buttons which are not connected in an array. Any combination in between is also acceptable (for example, a 3 x 4 keypad matrix and using the remaining 11 GPIOs as a combination of inputs and outputs).

For both types of inputs (keypad matrix and a GPI), a key event can be added to the key event FIFO. The values that are added to the FIFO depend on the configuration (keypad array or GPI) and on which port the press was read on. The tables below show the values that correspond to both types of configurations.

Key values below are represented in decimal values, because the 10s place is used to mark the row, and the ones place is used to denote the column. It is more clear to see the numbering convention used when viewed in decimal values.

|    | C0 | C1 | C2 | C3 | C4 | C5 | C6 | C7 | C8 | C9 |

|----|----|----|----|----|----|----|----|----|----|----|

| R0 | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

| R1 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

| R2 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 |

| R3 | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 |

| R4 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 50 |

| R5 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 |

| R6 | 61 | 62 | 63 | 64 | 65 | 66 | 67 | 68 | 69 | 70 |

| R7 | 71 | 72 | 73 | 74 | 75 | 76 | 77 | 78 | 79 | 80 |

#### Table 1. Key Event Table (Keypad Array)

**NSTRUMENTS**

**EXAS**

#### Table 2. Key Event Table (Row GPI Events)

| R0 | R1 | R2 | R3  | R4  | R5  | R6  | R7  |

|----|----|----|-----|-----|-----|-----|-----|

| 97 | 98 | 99 | 100 | 101 | 102 | 103 | 104 |

#### Table 3. Key Event Table (Column GPI Events)

| C0  | C1  | C2  | C3  | C4  | C5  | C6  | C7  | C8  | C9  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 105 | 106 | 107 | 108 | 109 | 110 | 111 | 112 | 113 | 114 |

#### 8.3.1.2 General Purpose Input (GPI) Events

A column or row configured as GPI can be programmed to be part of the *Key Event Table*, hence becomes also capable of generating Key Event Interrupt. A Key Event Interrupt caused by a GPI follow the same process flow as a Key Event Interrupt caused by a Key press.

GPIs configured as part of the Key Event Table allows for single key switches to be monitored as well as other GPI interrupts. As part of the Event Table, GPIs are represented with decimal value of 97 and run through decimal value of 114. R0-R7 are represented by 97-104 and C0-C9 are represented by 105-114

For a GPI that is set as active high, and is enabled in the Key Event Table, the state-machine will add an event to the event count and event table whenever that GPI goes high. If the GPI is set to active low, a transition from high to low will be considered a press and will also be added to the event count and event table. Once the interrupt state has been met, the state machine will internally set an interrupt for the opposite state programmed in the register to avoid polling for the released state, hence saving current. Once the released state is achieved, it will add it to the event table. The press and release will still be indicated by bit 7 in the event register.

The GPI Events can also be used as unlocked sequences. When the GPI\_EM bit is set, GPI events will not be tracked when the keypad is locked. GPI\_EM bit must be cleared for the GPI events to be tracked in the event counter and table when the keypad is locked.

#### 8.3.1.3 Key Event (FIFO) Reading

The TCA8418 has a 10-byte event FIFO, which stores any key presses or releases which have been configured to be added to the Key Event Table. All ROWs and COLs added to the keypad matrix via the *KP\_GPI01-3 Registers* will have any key pad events added to the FIFO. Any GPIs configured with a 1 in the *GPI\_EM1-3 Registers* will also be part of the event FIFO.

When the host wishes to read the FIFO, the following procedure is recommended.

- 1. Read the *INT\_STAT (0x02)* register to determine what asserted the INT line. If GPI\_INT or K\_INT is set, then a key event has occurred, and the event is stored in the FIFO.

- 2. Read the KEY\_LCK\_EC (0x03) register, bits [3:0] to see how many events are stored in FIFO.

- 3. Read the KEY\_EVENT\_A (0x04) register. Bit 7 value '0' signifies key release, value 1 signifies key press. Bits [6:0] state which key was pressed with respect to the Key Event Table. With each read of the key event register, the event counter in KEY\_LCK\_EC[3:0] will decrease by 1, and the FIFO will shift the events down 1 register.

- Repeat step 3 until either KEY\_LCK\_EC[3:0] = 0 or KEY\_EVENT\_A = 0. This signifies that the FIFO is empty.

- 5. Reset the INT\_STAT interrupt flag which was causing the interrupt by writing a 1 to the specific bit.

As an example, consider the following key presses.

| Event # | Key (Decimal Value) | Press/Release |

|---------|---------------------|---------------|

| 1       | 1                   | Press         |

| 2       | 32                  | Press         |

| 3       | 1                   | Release       |

| 4       | 32                  | Release       |

| 5       | 23                  | Press         |

| 6       | 23                  | Release       |

| 7       | 45                  | Press         |

| 8       | 41                  | Press         |

| 9       | 41                  | Release       |

| 10      | 45                  | Release       |

If this example key sequence occurs, then while performing the recommended read procedure listed above, the host would see the following information. Information at the top of the list is of an initial read to the KEY\_LCK\_EC[3:0] register.

| KEY_LCK_EC[3:0] Value | KEY_EVENT_A Value<br>(Binary/Hex) | Key (Decimal Value) | Press/Release |  |

|-----------------------|-----------------------------------|---------------------|---------------|--|

| 10                    | N/A                               | N/A                 | N/A           |  |

| 9                     | 1 000 0001 (0x81)                 | 1                   | Press         |  |

| 8                     | 1 010 0000 (0xA0)                 | 32                  | Press         |  |

| 7                     | 0 000 0001 (0x01)                 | 1                   | Release       |  |

| 6                     | 0 010 0000 (0x20)                 | 32                  | Release       |  |

| 5                     | 1 001 0111 (0x97)                 | 23                  | Press         |  |

| 4                     | 0 001 0111 (0x17)                 | 23                  | Release       |  |

| 3                     | 1 010 1101 (0xAD)                 | 45                  | Press         |  |

| 2                     | 1 010 1001 (0xA9)                 | 41                  | Press         |  |

| 1                     | 0 010 1001 (0x29)                 | 41                  | Release       |  |

| 0                     | 0 010 1101 (0x2D)                 | 45                  | Release       |  |

Table 5. Example Key Sequence

#### <sup>(1)</sup>8.3.1.4 Key Event Overflow

The TCA8418 has the ability to handle an overflow of the key event FIFO. An overflow event occurs when the FIFO is full of events (10 key events are stored) and a new key event occurs. In short, this means that the TCA8418 does not have the ability to hold any more key press information in the internal buffer. When this occurs, the OVR\_FLOW\_INT bit in the *INT\_STAT Register* is set, and if the OVR\_FLOW\_IEN bit is set in the *CFG Register*, then the INT output will be asserted low to let the processor know that an overflow has occurred.

The TCA8418 has the ability to handle an overflow in 1 of two ways, which is determined by the bit value of the OVR\_FLOW\_M bit in the *CFG Register*.

Please see the Overflow Errata section for more information about overflow behavior.

| OVR_FLOW_M Value | Overflow Mode      | Behavior                                                     |

|------------------|--------------------|--------------------------------------------------------------|

| 1                | Enabled            | Overflow data shifts with last event pushing first event out |

| 0                | Disabled (Default) | Overflow data is not stored and lost                         |

#### Table 6. OVR\_FLOW\_M Bit

(1) Note that the MSB of the KEY\_EVENT\_A value signifies a key press or release. MSB Bit = 1 signifies a key press; MSB Bit = 0 signifies a key release

**INSTRUMENTS**

Texas

Consider the example below, if the FIFO is full of the key presses and a new key press comes in. This new overflow key press will be a key press of key 2 (0x82 is the hex representation of a key 2 press event)

| FIFO Pagiatar | Original Value | After Key 1 Press Event (0x82) |                |  |  |  |  |

|---------------|----------------|--------------------------------|----------------|--|--|--|--|

| FIFO Register | Original Value | OVR_FLOW_M = 1                 | OVR_FLOW_M = 0 |  |  |  |  |

| A             | 0x81           | 0xA0                           | 0x81           |  |  |  |  |

| В             | 0xA0           | 0x01                           | 0xA0           |  |  |  |  |

| С             | 0x01           | 0x20                           | 0x01           |  |  |  |  |

| D             | 0x20           | 0x97                           | 0x20           |  |  |  |  |

| E             | 0x97           | 0x17                           | 0x97           |  |  |  |  |

| F             | 0x17           | 0xAD                           | 0x17           |  |  |  |  |

| Н             | 0xAD           | 0xA9                           | 0xAD           |  |  |  |  |

| I             | 0xA9           | 0x29                           | 0xA9           |  |  |  |  |

| J             | 0x29           | 0x2D                           | 0x29           |  |  |  |  |

| К             | 0x2D           | 0x82                           | 0x2D           |  |  |  |  |

#### Table 7. Key Event Overflow Handling

#### 8.3.2 Keypad Lock/Unlock

This user can lock the keypad through the lock/unlock feature in this device. Once the keypad is locked by setting BIT6 in *KEY\_LCK\_EC*, it can prevent the generation of key event interrupts and recorded key events. The unlock keys can be programmed with any value of the keys in the keypad matrix or any general purpose input (GPI) values that are part of the *Key Event Table*. When the keypad lock interrupt mask timer is non-zero, the user will need to press two specific keys before an keylock interrupt is generated or keypad events are recorded. A key event interrupt is generated the first time a user presses any key. This first interrupt can be used to turn on an LCD and display the unlock message. The processor will then read the lock status register to see if the keypad is unlocked. The next interrupt (keylock interrupt) will not be generated unless both unlock keys sequences are correct. If correct Unlock keys are not pressed before the mask timer expires, the state machine will start over again.

The recommended procedure to lock the keypad is to do the following

- 1. Determine which keys will be used for the unlock sequence. The key value from the *Key Event Tables* needs to be entered into the *UNLOCK1* and *UNLOCK2* registers.

- 2. The UNLOCK1 to UNLOCK2 timer duration must be set by entering the desired seconds (valid range is 0 to 7 seconds) into bits [2:0] of the *KP\_LCK\_TMR* register.

- 3. If an interrupt mask is desired (see *Keypad Lock Interrupt Mask Timer*), then the desired interrupt mask duration (valid range is 0 to 31 seconds) must be entered into bits [7:3] of the *KP\_LCK\_TMR* register.

- 4. When the host is ready to lock the keypad, a 1 is to be written to the K\_LCK\_EN bit (BIT6) in the KEY\_LCK\_EC register. This will lock the keypad.

- 5. If the host wishes to manually unlock the keypad, writing a '0' to the K\_LCK\_EN bit (BIT6) in the KEY\_LCK\_EC register will unlock the keypad.

Figure 20. Keypad Lock Flowchart

#### 8.3.3 Keypad Lock Interrupt Mask Timer

The TCA8418 features a *Keypad Lock/Unlock* feature which allows the user to stop the generation of key event interrupts by locking the key pad. There is an interrupt mask timer feature with the keypad lock, which allows the generation of a single interrupt when a key is pressed, primarily for the purpose of LCD backlighting. Note that this interrupt mask timer can also be used to limit the number of interrupts generated for a given amount of time.

The interrupt mask timer is enabled by setting bits [7:3] of the *KP\_LCK\_TIMER* register. The value in this register can be anywhere from 0 to 31 seconds (note that a value of 0 will disable this interrupt mask feature). When a keypad is locked and the interrupt mask timer is set to a non-zero value, this will enable the interrupt mask timer. This interrupt mask timer limits the amount of interrupts generated. Typically, this is used with the *Keypad Lock/Unlock* feature for LCD back lights. It is easiest to explain this feature with the following example; A mobile device has a LCD screen with a back light display which turns off after 10 seconds to save power. Normally, an interrupt to the processor would tell this LCD back light to turn on. When the keypad is locked, no interrupts are generated, so the back light will never turn on. This is where the interrupt mask feature is used. Please refer to Figure 20.The procedure for an example is below.

- 1. Since the back light turns off after 10 seconds of no interrupts, the interrupt mask timer ( <u>KP\_LCK\_TIMER</u>[7:3]) gets set to 10 seconds. Keypad is then locked.

- 2. When the first key press is detected, the TCA8418 sends an interrupt to the processor and starts a 10 second count down.

- 3. If the correct unlock sequence is not entered within the 10 seconds, no interrupts are sent and the back light will turn off.

- 4. After the 10 second timer has expired, if another key press occurs while keypad is locked (regardless of whether it is a correct unlock key or not), another interrupt is generated and the 10 second count down begins again.

SCPS215F-SEPTEMBER 2009-REVISED JULY 2017

www.ti.com

#### 8.3.4 Control-Alt-Delete Support

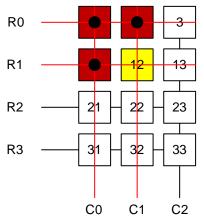

The TCA8418 can support normal key presses, but it also can support a <Ctrl><Alt><Del> (CAD) key press. This feature allows the host to recognize a specific key press and alert the host that the combination has occurred. The TCA8418 will recognize a <Ctrl><Alt><Del> key press if keys 1, 11, and 21 are all pressed at the same time. These keys are referenced to the key values listed in the *Key Event Table*. Note that this key combination that triggers a CAD interrupt is not adjustable, and must be keys 1, 11, and 21.

Please see CAD Interrupt Errata for more information.

#### 8.3.5 Interrupt Output

An interrupt is generated by any rising or falling edge of the port inputs in the input mode. After time  $t_{iv}$ , the signal INT is valid. Resetting the interrupt circuit is achieved when data on the port is changed to the original setting or data is read from the port that generated the interrupt. Resetting occurs in the read mode at the acknowledge (ACK) or not acknowledge (NACK) bit after the rising edge of the SCL signal. Interrupts that occur during the ACK or NACK clock pulse can be lost (or be very short) due to the resetting of the interrupt during this pulse. Each change of the I/Os after resetting is detected and is transmitted as INT.

Reading from or writing to another device does not affect the interrupt circuit, and a pin configured as an output cannot cause an interrupt. Changing an I/O from an output to an input may cause a false interrupt to occur, if the state of the pin does not match the contents of the input port register.

The INT output has an open-drain structure and requires a pull-up resistor to  $V_{CC}$  depending on the application. If the INT signal is connected back to the processor that provides the SCL signal to the TCA8418, then the INT pin has to be connected to  $V_{CC}$ . If not, the INT pin can be connected to  $V_{CC}$ .

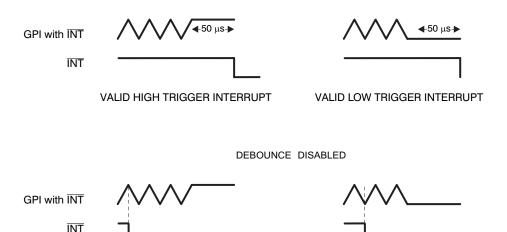

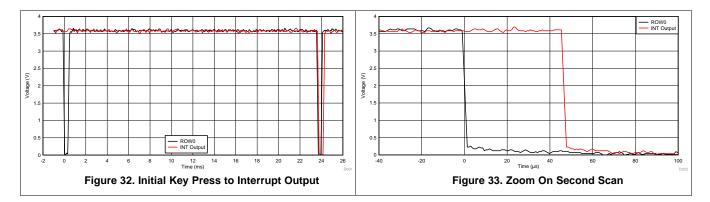

#### 8.3.5.1 50 Micro-second Interrupt Configuration

The TCA8418 provides the capability of deasserting the interrupt for 50 µs while there is a pending event. When the INT\_CFG bit in Register 0x01 is set, any attempt to clear the interrupt bit while the interrupt pin is already asserted results in a 50 µs deassertion. When the INT\_CFG bit is cleared, INT remains asserted if the host tries to clear the interrupt. This feature is particularly useful for software development and edge triggering applications.

#### 8.4 Device Functional Modes

#### 8.4.1 Power-On Reset (POR)

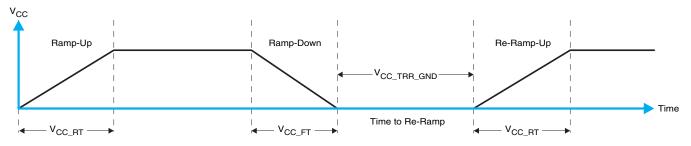

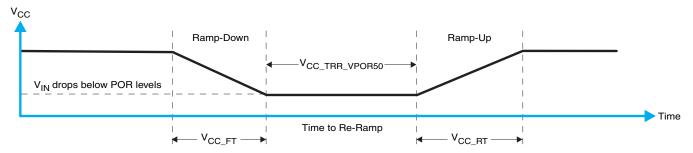

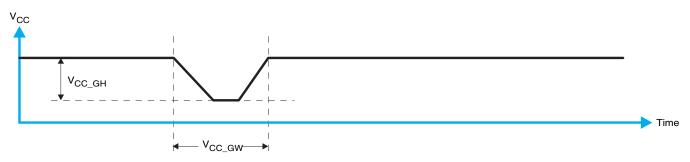

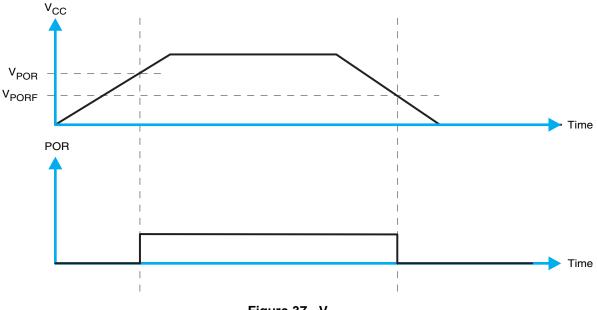

When power (from 0 V) is applied to  $V_{CC}$ , an internal power-on reset circuit holds the TCA8418 in a reset condition until  $V_{CC}$  has reached  $V_{PORR}$ . At that time, the reset condition is released, and the TCA8418 registers and I<sup>2</sup>C/SMBus state machine initialize to their default states. After that,  $V_{CC}$  must be lowered to below  $V_{PORF}$  and back up to the operating voltage for a power-reset cycle. See *Power Supply Recommendations* for more information on power up reset requirements.

#### 8.4.2 Powered (Key Scan Mode)

The TCA8418 can be used to read GPI from single buttons, or configured in key scan mode to read an array of keys. In key scan mode, there are two modes of operation.

#### 8.4.2.1 Idle Key Scan Mode

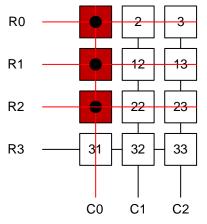

Once the TCA8418 has had the keypad array configured, it will enter idle mode when no keys are being pressed. All columns configured as part of the keypad array will be driven low and all rows configured as part of the keypad array will be set to inputs, with pull-up resistors enabled. During idle mode, the internal oscillator is turned off so that power consumption is low as the device awaits a key press.

#### 8.4.2.2 Active Key Scan Mode

When the TCA8418 is in idle key scan mode, the device awaits a key press. Once a key is pressed in the array, a low signal on one of the ROW pin inputs triggers an interrupt, which will turn on the internal oscillator and enter the active key scan mode. At this point, the TCA8418 will start the key scan algorithm to determine which key is being pressed, and/or it will use the internal oscillator for debouncing. Once all keys have been released, the device will enter idle key scan mode.

#### 8.5 Programming

#### 8.5.1 I<sup>2</sup>C Interface

The TCA8418 has a standard bidirectional  $I^2C$  interface that is controlled by a master device in order to be configured or read the status of this device. Each slave on the  $I^2C$  bus has a specific device address to differentiate between other slave devices that are on the same  $I^2C$  bus. Many slave devices will require configuration upon startup to set the behavior of the device. This is typically done when the master accesses internal register maps of the slave, which have unique register addresses. A device can have one or multiple registers where data is stored, written, or read.

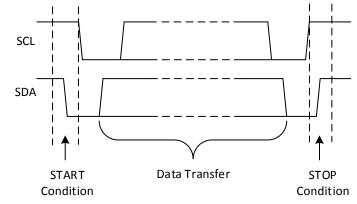

The physical I<sup>2</sup>C interface consists of the serial clock (SCL) and serial data (SDA) lines. Both SDA and SCL lines must be connected to  $V_{CC}$  through a pull-up resistor. The size of the pull-up resistor is determined by the amount of capacitance on the I<sup>2</sup>C lines. (For further details, refer to *I*<sup>2</sup>C *pull-up Resistor Calculation* (SLVA689).) Data transfer may be initiated only when the bus is idle. A bus is considered idle if both SDA and SCL lines are high after a STOP condition.

The following is the general procedure for a master to access a slave device:

- 1. If a master wants to send data to a slave:

- Master-transmitter sends a START condition and addresses the slave-receiver.

- Master-transmitter sends data to slave-receiver.

- Master-transmitter terminates the transfer with a STOP condition.

- 2. If a master wants to receive or read data from a slave:

- Master-receiver sends a START condition and addresses the slave-transmitter.

- Master-receiver sends the requested register to read to slave-transmitter.

- Master-receiver receives data from the slave-transmitter.

- Master-receiver terminates the transfer with a STOP condition.

Figure 21. Definition of Start and Stop Conditions

TEXAS INSTRUMENTS

www.ti.com

## Programming (continued)

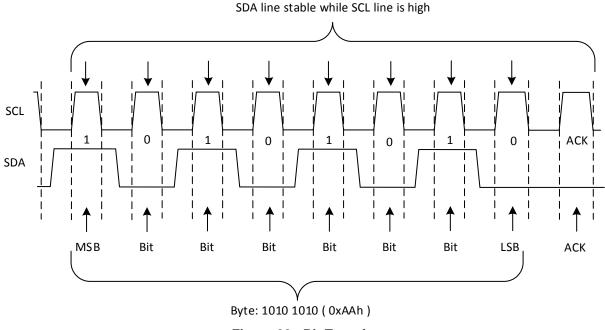

#### Figure 22. Bit Transfer

#### 8.5.2 Bus Transactions

Data must be sent to and received from the slave devices, and this is accomplished by reading from or writing to registers in the slave device.

Registers are locations in the memory of the slave which contain information, whether it be the configuration information or some sampled data to send back to the master. The master must write information to these registers in order to instruct the slave device to perform a task.

While it is common to have registers in I<sup>2</sup>C slaves, note that not all slave devices will have registers. Some devices are simple and contain only 1 register, which may be written to directly by sending the register data immediately after the slave address, instead of addressing a register. An example of a single-register device would be an 8-bit I<sup>2</sup>C switch, which is controlled via I<sup>2</sup>C commands. Since it has 1 bit to enable or disable a channel, there is only 1 register needed, and the master merely writes the register data after the slave address, skipping the register number.

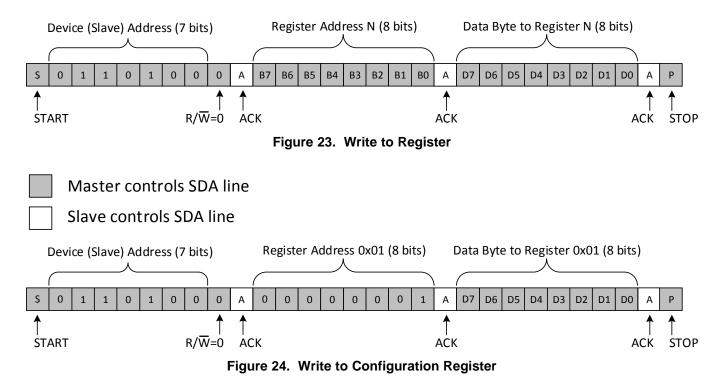

#### 8.5.2.1 Writes

To write on the  $l^2C$  bus, the master will send a START condition on the bus with the address of the slave, as well as the last bit (the R/W bit) set to 0, which signifies a write. After the slave sends the acknowledge bit, the master will then send the register address of the register to which it wishes to write. The slave will acknowledge again, letting the master know it is ready. After this, the master will start sending the register data to the slave until the master has sent all the data necessary (which is sometimes only a single byte), and the master will terminate the transmission with a STOP condition.

Figure 23 shows an example of writing a single byte to a register.

## **Programming (continued)**

Slave controls SDA line

## Write to one register in a device

#### **Programming (continued)**

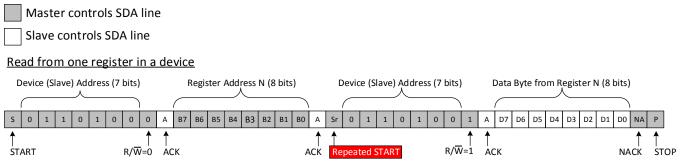

#### 8.5.2.2 Reads

Reading from a slave is very similar to writing, but requires some additional steps. In order to read from a slave, the master must first instruct the slave which register it wishes to read from. This is done by the master starting off the transmission in a similar fashion as the write, by sending the address with the R/W bit equal to 0 (signifying a write), followed by the register address it wishes to read from. Once the slave acknowledges this register address, the master will send a START condition again, followed by the slave address with the R/W bit set to 1 (signifying a read). This time, the slave will acknowledge the read request, and the master will release the SDA bus but will continue supplying the clock to the slave. During this part of the transaction, the master will become the master-receiver, and the slave will become the slave-transmitter.

The master will continue to send out the clock pulses, but will release the SDA line so that the slave can transmit data. At the end of every byte of data, the master will send an ACK to the slave, letting the slave know that it is ready for more data. Once the master has received the number of bytes it is expecting, it will send a NACK, signaling to the slave to halt communications and release the bus. The master will follow this up with a STOP condition.

Figure 25 shows an example of reading a single byte from a slave register.

Figure 25. Read from Register

#### 8.6 Register Maps

#### 8.6.1 Device Address

The address of the TCA8418 is shown in Table 8.

| Table 8. T | CA8418 | Device | Addresses |

|------------|--------|--------|-----------|

|------------|--------|--------|-----------|

| BYTE                           | BIT     |   |   |   |   |   |   |         |

|--------------------------------|---------|---|---|---|---|---|---|---------|

|                                | 7 (MSB) | 6 | 5 | 4 | 3 | 2 | 1 | 0 (LSB) |

| I <sup>2</sup> C slave address | 0       | 1 | 1 | 0 | 1 | 0 | 0 | R/W     |

The last bit of the slave address defines the operation (read or write) to be performed. A high (1) selects a read operation, while a low (0) selects a write operation.

#### 8.6.2 Control Register and Command Byte

Following the successful acknowledgment of the address byte, the bus master sends a command byte, which is stored in the control register in the TCA8418. The command byte indicates the register that will be updated with information. All registers can be read and written to by the system master.

Table 9 shows all the registers within this device and their descriptions. The default value in all registers is 0.

| ADDRESS | REGISTER NAME | REGISTER<br>DESCRIPTION                                              | 7         | 6             | 5              | 4           | 3                    | 2             | 1           | 0         |

|---------|---------------|----------------------------------------------------------------------|-----------|---------------|----------------|-------------|----------------------|---------------|-------------|-----------|

| 0x00    | Reserved      | Reserved                                                             |           |               |                |             |                      |               |             |           |

| 0x01    | CFG           | Configuration register<br>(interrupt processor<br>interrupt enables) | AI        | GPI_E_<br>CGF | OVR_FL<br>OW_M | INT_<br>CFG | OVR_F<br>LOW_I<br>EN | K_LC<br>K_IEN | GPI_IE<br>N | KE_IEN    |

| 0x02    | INT_STAT      | Interrupt status register                                            | N/A<br>0  | N/A<br>0      | N/A<br>0       | CAD_I<br>NT | OVR_F<br>LOW_I<br>NT | K_LC<br>K_INT | GPI_<br>INT | K_ INT    |

| 0x03    | KEY_LCK_EC    | Key lock and event<br>counter register                               | N/A<br>0  | K_LCK<br>_EN  | LCK2           | LCK1        | KLEC3                | KLEC<br>2     | KLEC1       | KLEC0     |

| 0x04    | KEY_EVENT_A   | Key event register A                                                 | KEA7<br>0 | KEA6<br>0     | KEA5<br>0      | KEA4<br>0   | KEA3<br>0            | KEA2<br>0     | KEA1<br>0   | KEA0<br>0 |

| 0x05    | KEY_EVENT_B   | Key event register B                                                 | KEB7<br>0 | KEB6<br>0     | KEB5<br>0      | KEB4<br>0   | KEB3<br>0            | KEB2<br>0     | KEB1<br>0   | KEB0<br>0 |

| 0x06    | KEY_EVENT_C   | Key event register C                                                 | KEC7<br>0 | KEC6<br>0     | KEC5<br>0      | KEC4<br>0   | KEC3<br>0            | KEC2<br>0     | KEC1<br>0   | KEC0<br>0 |

| 0x07    | KEY_EVENT_D   | Key event register D                                                 | KED7<br>0 | KED6<br>0     | KED5<br>0      | KED4<br>0   | KED3<br>0            | KED2<br>0     | KED1<br>0   | KED0<br>0 |

| 0x08    | KEY_EVENT_E   | Key event register E                                                 | KEE7<br>0 | KEE6<br>0     | KEE5<br>0      | KEE4<br>0   | KEE3<br>0            | KEE2<br>0     | KEE1<br>0   | KEE0<br>0 |

| 0x09    | KEY_EVENT_F   | Key event register F                                                 | KEF7<br>0 | KEF6<br>0     | KEF5<br>0      | KEF4<br>0   | KEF3<br>0            | KEF2<br>0     | KEF1<br>0   | KEF0<br>0 |

| 0x0A    | KEY_EVENT_G   | Key event register G                                                 | KEG7<br>0 | KEG6<br>0     | KEG5<br>0      | KEG4<br>0   | KEG3<br>0            | KEG2<br>0     | KEG1<br>0   | KEG0<br>0 |

| 0x0B    | KEY_EVENT_H   | Key event register H                                                 | KEH7<br>0 | KEH6<br>0     | KEH5<br>0      | KEH4<br>0   | KEH3<br>0            | KEH2<br>0     | KEH1<br>0   | KEH0<br>0 |

| 0x0C    | KEY_EVENT_I   | Key event register I                                                 | KEI7<br>0 | KEI6<br>0     | KEI5<br>0      | KEI4<br>0   | KEI3<br>0            | KEI2<br>0     | KEI1<br>0   | KEI0<br>0 |

| 0x0D    | KEY_EVENT_J   | Key event register J                                                 | KEJ7<br>0 | KEJ6<br>0     | KEJ5<br>0      | KEJ64<br>0  | KEJ3<br>0            | KEJ2<br>0     | KEJ1<br>0   | KEJ0<br>0 |

| 0x0E    | KP_LCK_TIMER  | Keypad lock 1 to lock 2<br>timer                                     | KL7       | KL6           | KL5            | KL4         | KL3                  | KL2           | KL1         | KL0       |

| 0x0F    | UNLOCK1       | Unlock key 1                                                         | UK1_7     | UK1_6         | UK1_5          | UK1_4       | UK1_3                | UK1_<br>2     | UK1_1       | UK1_0     |

| 0x10    | UNLOCK1       | Unlock key2                                                          | UK2_7     | UK2_6         | UK2_5          | UK2_4       | UK2_3                | UK2_<br>2     | UK2_1       | UK2_0     |

#### **Table 9. Register Descriptions**

Copyright © 2009–2017, Texas Instruments Incorporated

**TCA8418**

SCPS215F-SEPTEMBER 2009-REVISED JULY 2017

SCPS215F-SEPTEMBER 2009-REVISED JULY 2017

TCA8418

| Table 9. Regist | er Desc | riptions | s (contin | ued) |  |

|-----------------|---------|----------|-----------|------|--|

|                 |         |          |           |      |  |

|         |                                         |                                                        |           |           | •         | · ·       |           |           |           |           |

|---------|-----------------------------------------|--------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| ADDRESS | REGISTER NAME                           | REGISTER<br>DESCRIPTION                                | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

| 0x11    | GPIO_INT_STAT1                          | GPIO interrupt status                                  | R7IS<br>0 | R6IS<br>0 | R5IS<br>0 | R4IS<br>0 | R3IS<br>0 | R2IS<br>0 | R1IS<br>0 | R0IS<br>0 |

| 0x12    | GPIO_INT_STAT2                          | GPIO interrupt status                                  | C7IS<br>0 | C6IS<br>0 | C5IS<br>0 | C4IS<br>0 | C3IS<br>0 | C2IS<br>0 | C1IS<br>0 | COIS<br>0 |

| 0x13    | GPIO_INT_STAT3                          | GPIO interrupt status                                  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | C9IS<br>0 | C8IS<br>0 |

| 0x14    | GPIO_DAT_STAT1 (read twice to clear)    | GPIO data status                                       | R7DS      | R6DS      | R5DS      | R4DS      | R3DS      | R2DS      | R1DS      | R0DS      |

| 0x15    | GPIO_DAT_STAT2<br>(read twice to clear) | GPIO data status                                       | C7DS      | C6DS      | C5DS      | C4DS      | C3DS      | C2DS      | C1DS      | CODS      |

| 0x16    | GPIO_DAT_STAT3 (read twice to clear)    | GPIO data status                                       | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | C9DS      | C8DS      |

| 0x17    | GPIO_DAT_OUT1                           | GPIO data out                                          | R7DO<br>0 | R6DO<br>0 | R5DO<br>0 | R4DO<br>0 | R3DO<br>0 | R2DO<br>0 | R1DO<br>0 | R0DO<br>0 |

| 0x18    | GPIO_DAT_OUT2                           | GPIO data out                                          | C7DO<br>0 | C6DO<br>0 | C5DO<br>0 | C4DO<br>0 | C3DO<br>0 | C2DO<br>0 | C1DO<br>0 | C0DO<br>0 |

| 0x19    | GPIO_DAT_OUT3                           | GPIO data out                                          | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | C9DO<br>0 | C8DO<br>0 |

| 0x1A    | GPIO_INT_EN1                            | GPIO interrupt enable                                  | R7IE<br>0 | R6IE<br>0 | R5IE<br>0 | R4IE<br>0 | R3IE<br>0 | R2IE<br>0 | R1IE<br>0 | R0IE<br>0 |

| 0x1B    | GPIO_INT_EN2                            | GPIO interrupt enable                                  | C7IE<br>0 | C6IE<br>0 | C5IE<br>0 | C4IE<br>0 | C3IE<br>0 | C2IE<br>0 | C1IE<br>0 | COIE<br>0 |

| 0x1C    | GPIO_INT_EN3                            | GPIO interrupt enable                                  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | C9IE<br>0 | C8IE<br>0 |

| 0x1D    | KP_GPIO1                                | Keypad or GPIO<br>selection<br>0: GPIO<br>1: KP matrix | ROW7<br>0 | ROW6<br>0 | ROW5<br>0 | ROW4<br>0 | ROW3<br>0 | ROW2<br>0 | ROW1<br>0 | ROW0<br>0 |

| 0x1E    | KP_GPIO2                                | Keypad or GPIO<br>selection<br>0: GPIO<br>1: KP matrix | COL7<br>0 | COL6<br>0 | COL5<br>0 | COL4<br>0 | COL3<br>0 | COL2<br>0 | COL1<br>0 |           |

| 0x1F    | KP_GPIO3                                | Keypad or GPIO<br>selection<br>0: GPIO<br>1: KP matrix | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | COL9<br>0 | COL8<br>0 |

| 0x20    | GPI_EM1                                 | GPI event mode 1                                       | ROW7<br>0 | ROW6<br>0 | ROW5<br>0 | ROW4<br>0 | ROW3<br>0 | ROW2<br>0 | ROW1<br>0 | ROW0<br>0 |

| 0x21    | GPI_EM2                                 | GPI event mode 2                                       | COL7<br>0 | COL6<br>0 | COL5<br>0 | COL4<br>0 | COL3<br>0 | COL2<br>0 | COL1<br>0 | COL0<br>0 |

| 0x22    | GPI_EM3                                 | GPI event mode 3                                       | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | COL9<br>0 | COL8<br>0 |

| 0x23    | GPIO_DIR1                               | GPIO data direction<br>0: input<br>1: output           | R7DD<br>0 | R6DD<br>0 | R5DD<br>0 | R4DD<br>0 | R3DD<br>0 | R2DD<br>0 | R1DD<br>0 | R0DD<br>0 |

| 0x24    | GPIO_DIR2                               | GPIO data direction<br>0: input<br>1: output           | C7DD<br>0 | C6DD<br>0 | C5DD<br>0 | C4DD<br>0 | C3DD<br>0 | C2DD<br>0 | C1DD<br>0 | C0DD<br>0 |

| 0x25    | GPIO_DIR3                               | GPIO data direction<br>0: input<br>1: output           | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | C9DD<br>0 | C8DD<br>0 |

#### TCA8418 SCPS215F – SEPTEMBER 2009–REVISED JULY 2017

| ADDRESS | REGISTER NAME | REGISTER<br>DESCRIPTION                                           | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |  |  |

|---------|---------------|-------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|

| 0x26    | GPIO_INT_LVL1 | GPIO edge/level detect<br>0: falling/low<br>1: rising/high        | R7IL<br>0 | R6IL<br>0 | R5IL<br>0 | R4IL<br>0 | R3IL<br>0 | R2IL<br>0 | R1IL<br>0 | ROIL<br>0 |  |  |

| 0x27    | GPIO_INT_LVL2 | GPIO edge/level detect<br>0: falling/low<br>1: rising/high        | C7IL<br>0 | C6IL<br>0 | C5IL<br>0 | C4IL<br>0 | C3IL<br>0 | C2IL<br>0 | C1IL<br>0 | COIL<br>0 |  |  |

| 0x28    | GPIO_INT_LVL3 | GPIO edge/level detect<br>0: falling/low<br>1: rising/high        | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | C9IL<br>0 | C8IL<br>0 |  |  |

| 0x29    | DEBOUNCE_DIS1 | Debounce disable<br>0: debounce enabled<br>1: debounce disabled   | R7DD<br>0 | R6DD<br>0 | R5DD<br>0 | R4DD<br>0 | R3DD<br>0 | R2DD<br>0 | R1DD<br>0 | R0DD<br>0 |  |  |

| 0x2A    | DEBOUNCE_DIS2 | Debounce disable<br>0: debounce enabled<br>1: debounce disabled   | C7DD<br>0 | C6DD<br>0 | C5DD<br>0 | C4DD<br>0 | C3DD<br>0 | C2DD<br>0 | C1DD<br>0 | C0DD<br>0 |  |  |

| 0x2B    | DEBOUNCE_DIS3 | Debounce disable<br>0: debounce enabled<br>1: debounce disabled   | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | C9DD<br>0 | C8DD<br>0 |  |  |

| 0x2C    | GPIO_PULL1    | GPIO pull-up disable<br>0: pull-up enabled<br>1: pull-up disabled | R7PD<br>0 | R6PD<br>0 | R5PD<br>0 | R4PD<br>0 | R3PD<br>0 | R2PD<br>0 | R1PD<br>0 | R0PD<br>0 |  |  |

| 0x2D    | GPIO_PULL2    | GPIO pull-up disable<br>0: pull-up enabled<br>1: pull-up disabled | C7PD<br>0 | C6PD<br>0 | C5PD<br>0 | C4PD<br>0 | C3PD<br>0 | C2PD<br>0 | C1PD<br>0 | C0PD<br>0 |  |  |

| 0x2E    | GPIO_PULL3    | GPIO pull-up disable<br>0: pull-up enabled<br>1: pull-up disabled | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | N/A<br>0  | C9PD<br>0 | C8PD<br>0 |  |  |

| 0x2F    | Reserved      |                                                                   |           |           |           |           |           |           |           |           |  |  |

| 1       |               | 1                                                                 | 1         | 1         |           |           |           | 1         |           |           |  |  |

## Table 9. Register Descriptions (continued)