SLAS248D - DECEMBER 1999 - REVISED SEPTEMBER 2005

# 14-Bit, 1/3/8 MSPS, DSP-COMPATIBLE ANALOG-TO-DIGITAL CONVERTERS WITH INTERNAL REFERENCE AND PGA

## FEATURES

- 14-Bit Resolution

- 1, 3, and 8 MSPS Speed Grades Available

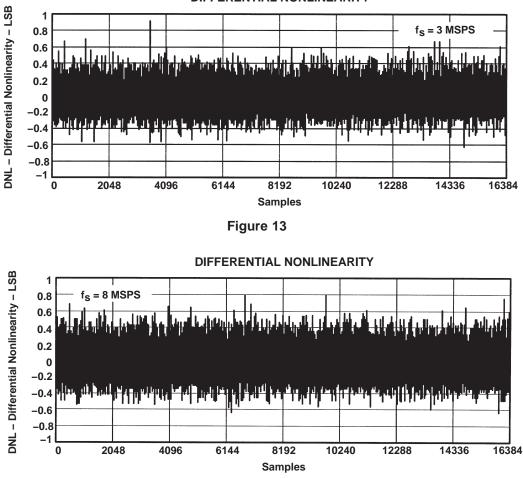

- Differential Nonlinearity (DNL) ±0.6 LSB Typ

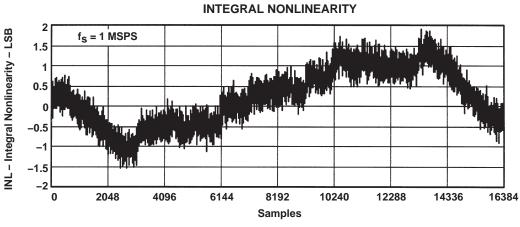

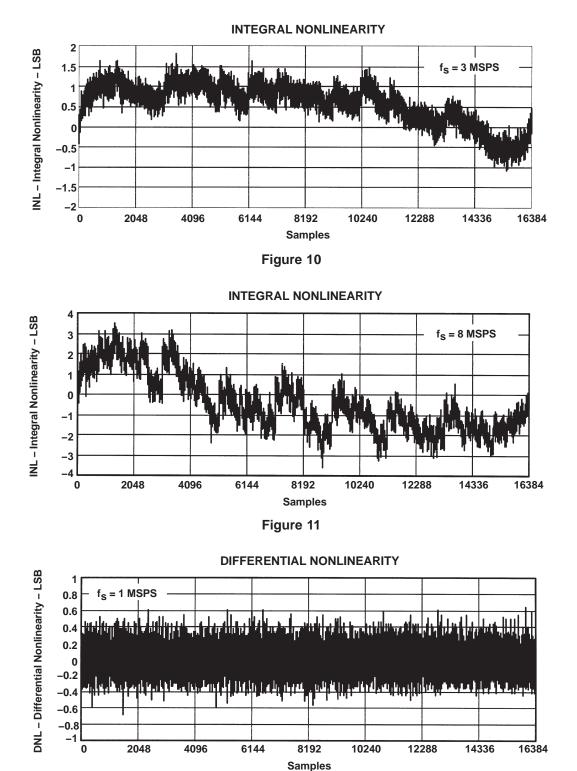

- Integral Nonlinearity (INL) ±1.5 LSB Typ

- Internal Reference

- Differential Inputs

- Programmable Gain Amplifier

- µP-Compatible Parallel Interface

- Timing Compatible With TMS320C6000 DSP

- 3.3-V Single Supply

- Power-Down Mode

- Monolithic CMOS Design

## **APPLICATIONS**

- xDSL Front Ends

- Communication

- Industrial Control

- Instrumentation

- Automotive

## DESCRIPTION

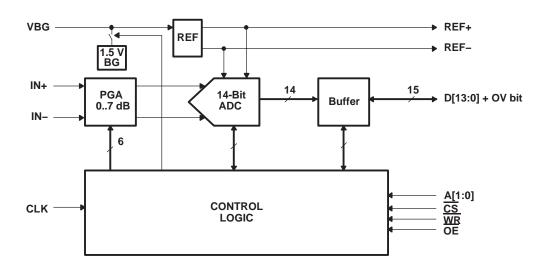

The THS1401, THS1403, and THS1408 are 14-bit, 1/3/8 MSPS, single supply analog-to-digital converters (ADCs) with an internal reference, differential inputs, programmable input gain, and an on-chip sample-and-hold amplifier.

Implemented with a CMOS process, the device has outstanding price/performance and power/speed ratios. The THS1401, THS1403, and THS1408 are designed for use with 3.3-V systems, and with a high-speed  $\mu$ P-compatible parallel interface, making them the first choice for solutions based on high-performance DSPs such as the TI TMS320C6000 series.

The THS1401, THS1403, and THS1408 are available in a TQFP-48 package in standard commercial and industrial temperature ranges. The THS1401, THS1403, and THS1408 are also available in a PQFP-48 package in automotive temperature range, and the THS1408 is available in a PQFP-48 package in military temperature range.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

Copyright @ 1999–2005, Texas Instruments Incorporated On products compliant to MIL-PRF-3853s, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters. SLAS248D - DECEMBER 1999 - REVISED SEPTEMBER 2005

#### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range unless otherwise noted.(1)

| Supply voltage, (AV <sub>DD</sub> to AGND)<br>Supply voltage, (DV <sub>DD</sub> to DGND)<br>Reference input voltage range, VBG<br>Analog input voltage range |                                  |                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------|

| Digital input voltage range                                                                                                                                  |                                  | – 0.3 V to DV <sub>DD</sub> + 0.3 V |

| Operating free-air temperature range, T <sub>A</sub> :                                                                                                       | C-suffix<br>I-suffix<br>Q-suffix |                                     |

| Storage temperature range, T <sub>stg</sub><br>Lead temperature 1,6 mm (1/16 inch) from                                                                      | n case for 10 seconds            | 65°C to 150°C<br>                   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

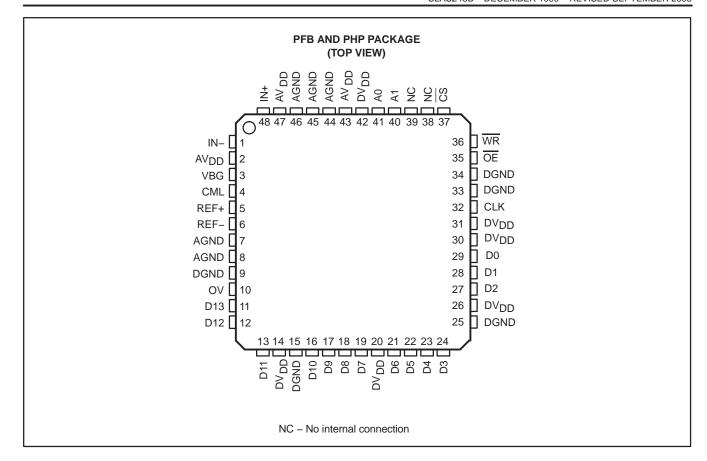

| TERM             | TERMINAL                                                     |     |                                                                                   |

|------------------|--------------------------------------------------------------|-----|-----------------------------------------------------------------------------------|

| NAME             | NO.                                                          | I/O | DESCRIPTION                                                                       |

| A[1:0]           | 40, 41                                                       | I   | Address input                                                                     |

| AGND             | 7,8, 44, 45, 46                                              |     | Analog ground                                                                     |

| AV <sub>DD</sub> | 2, 43, 47                                                    |     | Analog power supply                                                               |

| CLK              | 32                                                           | I   | Clock input                                                                       |

| CML              | 4                                                            |     | Reference midpoint. This pin requires a 0.1-µF capacitor to AGND.                 |

| CS               | 37                                                           | I   | Chip select input. Active low.                                                    |

| DGND             | 9, 15, 25, 33, 34                                            |     | Digital ground                                                                    |

| DVDD             | 14, 20, 26, 30, 31, 42                                       |     | Digital power supply                                                              |

| D[13:0]          | 11, 12, 13, 16, 17, 18,<br>19, 21, 22, 23, 24, 27,<br>28, 29 | I/O | Data inputs/outputs                                                               |

| NC               | 38, 39                                                       |     | No connection; do not use. Reserved.                                              |

| IN+              | 48                                                           | I   | Positive differential analog input                                                |

| IN-              | 1                                                            | I   | Negative differential analog input                                                |

| OE               | 35                                                           | I   | Output enable. Active low.                                                        |

| OV               | 10                                                           | 0   | Out-of-range output                                                               |

| REF+             | 5                                                            | 0   | Positive reference output. This pin requires a $0.1$ - $\mu$ F capacitor to AGND. |

| REF-             | 6                                                            | 0   | Negative reference output. This pin requires a $0.1-\mu F$ capacitor to AGND.     |

| VBG              | 3                                                            | I   | Reference input. This pin requires a 1-µF capacitor to AGND.                      |

| WR               | 36                                                           | I   | Write signal. Active low.                                                         |

## **Terminal Functions**

TEXAS INSTRUMENTS www.ti.com THS1401 THS1403 THS1408 SLAS248D – DECEMBER 1999 – REVISED SEPTEMBER 2005

|                | PACKAGED DEVICE                             |                                             |  |  |  |  |  |  |  |

|----------------|---------------------------------------------|---------------------------------------------|--|--|--|--|--|--|--|

| TA             | TQFP<br>(PFB)                               | PQFP (Power Pad)<br>(PHP)                   |  |  |  |  |  |  |  |

| 0°C to 70°C    | THS1401CPFB,<br>THS1403CPFB,<br>THS1408CPFB | _                                           |  |  |  |  |  |  |  |

| -40°C to 85°C  | THS1401IPFB,<br>THS1403IPFB,<br>THS1408IPFB | _                                           |  |  |  |  |  |  |  |

| -40°C to 125°C | _                                           | THS1401QPHP,<br>THS1403QPHP,<br>THS1408QPHP |  |  |  |  |  |  |  |

| –55°C to 125°C | _                                           | THS1408MPHP                                 |  |  |  |  |  |  |  |

THERMAL CHARACTERISTICS<sup>(1)</sup>

|                                              |             | TYP  | UNIT |

|----------------------------------------------|-------------|------|------|

| Thermal resistance, junction to embient Que  | PFB package | 85.9 | 0000 |

| Thermal resistance, junction-to-ambient, OJA | PHP package | 28.8 | °C/W |

|                                              | PFB package | 19.6 |      |

| Thermal resistance, junction-to-case, OJC    | PHP package | 0.79 | °C/W |

(1) Thermal resistance is modeled data, is not production tested, and is given for informational purposes only.

## **RECOMMENDED OPERATING CONDITIONS**

|                                                     |                 | MIN | NOM | MAX | UNIT |

|-----------------------------------------------------|-----------------|-----|-----|-----|------|

| Supply voltage, AV <sub>DD</sub> , DV <sub>DD</sub> |                 | 3   | 3.3 | 3.6 | V    |

| High level digital input, VIH                       |                 | 2   | 3.3 |     | V    |

| Low level digital input, VIL                        |                 |     | 0   | 0.8 | V    |

| Load capacitance, CL                                |                 |     | 5   | 15  | pF   |

|                                                     | THS1401         | 0.1 | 1   | 1   | MHz  |

| Clock frequency, fCLK                               | THS1403         | 0.1 | 3   | 3   | MHz  |

|                                                     | THS1408         | 0.1 | 8   | 8   | MHz  |

|                                                     | C- and I-suffix | 40  | 50  | 60  | 0/   |

| Clock duty cycle                                    | Q- and M-suffix | 45  | 50  | 55  | %    |

|                                                     | C-suffix        | 0   | 25  | 70  |      |

| Operating free-air temperature                      | I-suffix        | -40 | 25  | 85  | °C   |

|                                                     | Q-suffix        | -40 | 25  | 125 | -0   |

|                                                     | M-suffix        | -55 | 25  | 125 |      |

## **ELECTRICAL CHARACTERISTICS**

Over operating free-air temperature range, AVDD = DVDD = 3.3V, unless otherwise noted.

|         | PARAMETE                           | TEST CONDITIONS        | MIN                         | TYP  | MAX       | UNIT |      |  |

|---------|------------------------------------|------------------------|-----------------------------|------|-----------|------|------|--|

| Power S | Supply                             |                        | ·                           |      |           |      |      |  |

| IDDA    | Analog supply current              |                        | AV <sub>DD</sub> = 3.6 V    |      | 81        | 90   | mA   |  |

| IDDD    | Digital supply current             |                        | DV <sub>DD</sub> = 3.6 V    |      | 5         | 10   | mA   |  |

|         | Power                              |                        | $AV_{DD} = DV_{DD} = 3.6 V$ |      | 270       | 360  | mW   |  |

|         | Power down current                 |                        |                             |      | 20        |      | μΑ   |  |

| DC Cha  | racteristics                       |                        | •                           |      |           |      |      |  |

|         | Resolution                         |                        |                             |      | 14        |      | Bits |  |

| DNL     | Differential nonlinearity          |                        |                             |      | ±0.6      | ±1   | LSB  |  |

|         | THS1401                            |                        |                             | ±1.5 | ±2.5      |      |      |  |

|         |                                    | THS1403C/I             |                             |      | ±1.5      | ±2.5 |      |  |

| INL     | NL Integral nonlinearity           | THS1403Q               | Best fit                    |      | <u>+2</u> | ±3   | LSB  |  |

|         |                                    | THS1408C/I             |                             |      | ±3        | ±5   |      |  |

|         | THS1408Q/M                         |                        |                             | ±3.5 | ±7.5      |      |      |  |

|         | Offset error                       |                        | IN+=IN-, PGA=0 dB           |      |           | 0.3  | %FSR |  |

|         | <u>.</u>                           | C and I suffix         |                             |      |           | 1    | %FSR |  |

|         | Gain error                         | Q and M suffix         | PGA = 0 dB                  |      |           | 1.75 | %FSR |  |

| AC Cha  | racteristics                       |                        |                             |      |           |      |      |  |

| ENOB    | Effective number of bits           |                        |                             | 11.2 | 11.5      |      | Bits |  |

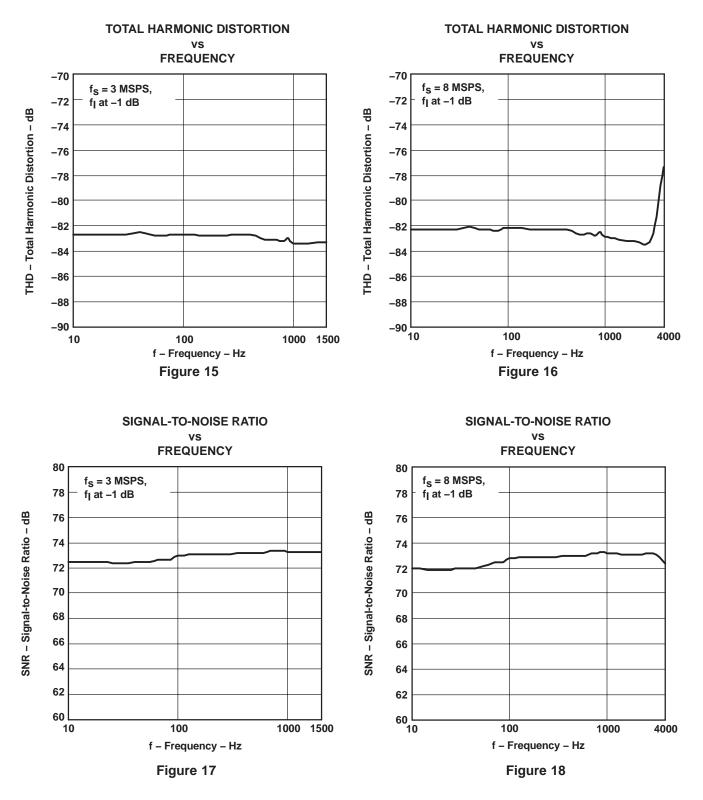

|         |                                    | THS1401/3/8            | f <sub>i</sub> = 100 kHz    |      | -81       |      |      |  |

| THD     | Total harmonic distortion          | THS1403/8              | f <sub>i</sub> = 1 MHz      |      | -78       |      | dB   |  |

|         |                                    | THS1408                | $f_i = 4 MHz$               |      | -77       |      |      |  |

|         |                                    | THS1401/3/8            | f <sub>i</sub> = 100 kHz    |      | 72        |      |      |  |

| SNR     | Signal-to-noise ratio              | THS1403/8              | f <sub>i</sub> = 1 MHz      | 70   | 72        |      | dB   |  |

|         |                                    | THS1408                | f <sub>i</sub> = 4 MHz      |      | 71        |      |      |  |

|         |                                    | THS1401/3/8            | f <sub>i</sub> = 100 kHz    |      | 70        |      |      |  |

| SINAD   | Signal-to-noise ratio + distortion | THS1403/8              | f <sub>i</sub> = 1 MHz      | 69   | 70        |      | dB   |  |

|         |                                    | THS1408                | $f_i = 4 MHz$               |      | 70        |      |      |  |

|         |                                    | THS1401/3/8            | f <sub>i</sub> = 100 kHz    |      | 80        |      |      |  |

|         | Coursians from dumonsis are set    | THS1403C/I, THS1408C/I | 6 4 MIL                     | 73   | 80        |      |      |  |

| SFDR    | Spurious-free dynamic range        | THS1403Q, THS1408Q/M   | f <sub>i</sub> = 1 MHz      | 71   | 80        |      | dB   |  |

|         |                                    | THS1408                | f <sub>i</sub> = 4 MHz      |      | 80        |      |      |  |

|         | Analog input bandwidth             |                        |                             |      | 140       |      | MHz  |  |

SLAS248D - DECEMBER 1999 - REVISED SEPTEMBER 2005

**ELECTRICAL CHARACTERISTICS (Cont.)** Over operating free-air temperature range, AVDD = DVDD = 3.3V, unless otherwise noted.

|         | PARAMETER                               | TEST CONDITIONS                                        | MIN               | TYP | MAX   | UNIT     |

|---------|-----------------------------------------|--------------------------------------------------------|-------------------|-----|-------|----------|

| Refere  | nce Voltage                             |                                                        |                   |     |       | <u>.</u> |

|         | Bandgap voltage, internal mode          |                                                        | 1.425             | 1.5 | 1.575 | V        |

|         | Input impedance                         |                                                        |                   | 40  |       | kΩ       |

|         | Positive reference voltage, REF+        |                                                        |                   | 2.5 |       | V        |

|         | Negative reference voltage, REF-        |                                                        |                   | 0.5 |       | V        |

|         | Reference difference, ∆REF, REF+ – REF– |                                                        |                   | 2   |       | V        |

|         | Accuracy, internal reference            |                                                        |                   | 5%  |       |          |

|         | Temperature coefficient                 |                                                        |                   | 40  |       | ppm/°C   |

|         | Voltage coefficient                     |                                                        |                   | 200 |       | ppm/V    |

| Analog  | J Inputs                                |                                                        |                   |     |       |          |

|         | Positive analog input, IN+              |                                                        | 0                 |     | AVDD  | V        |

|         | Negative analog input, IN–              |                                                        | 0                 |     | AVDD  | V        |

|         | Analog input voltage difference         | $\Delta A_{IN} = IN + - IN -, V_{REF} = REF + - REF -$ | -V <sub>REF</sub> |     | VREF  | V        |

|         | Input impedance                         |                                                        |                   | 25  |       | kΩ       |

|         | PGA range                               |                                                        | 0                 |     | 7     | dB       |

|         | PGA step size                           |                                                        |                   | 1   |       | dB       |

|         | PGA gain error                          |                                                        |                   |     | ±0.25 | dB       |

| Digital | Inputs                                  | ·                                                      |                   |     |       |          |

| VIH     | High-level digital input                |                                                        | 2                 |     |       | V        |

| VIL     | Low-level digital input                 |                                                        |                   |     | 0.8   | V        |

|         | Input capacitance                       |                                                        |                   | 5   |       | pF       |

|         | Input current                           |                                                        |                   |     | ±1    | μΑ       |

| Digital | Outputs                                 | ·                                                      |                   |     |       |          |

| Vон     | High-level digital output               | I <sub>OH</sub> = 50 μA                                | 2.6               |     |       | V        |

| VOL     | Low-level digital output                | I <sub>OL</sub> = 50 μA                                |                   |     | 0.4   | V        |

| loz     | Output current, high impedance          |                                                        |                   |     | ±10   | μΑ       |

| Clock   | Timing (CS low)                         |                                                        |                   |     |       |          |

|         |                                         | THS1401                                                | 0.1†              | 1   | 1     | MHz      |

| fCLK    | Clock frequency                         | THS1403                                                | 0.1†              | 3   | 3     | MHz      |

| -       |                                         | THS1408                                                | 0.1†              | 8   | 8     | MHz      |

| td      | Output delay time                       |                                                        |                   |     | 25    | ns       |

|         | Latency                                 |                                                        |                   | 9.5 |       | Cycles   |

<sup>†</sup> This parameter is not production tested for Q- and M-suffix devices.

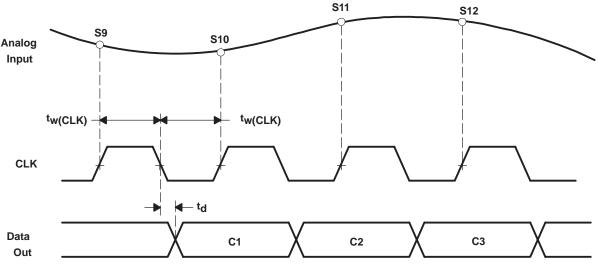

## PARAMETER MEASUREMENT INFORMATION

#### sample timing

The THS1401/3/8 core is based on a pipeline architecture with a latency of 9.5 samples. The conversion results appear on the digital output 9.5 clock cycles after the input signal was sampled.

Figure 1. Sample Timing

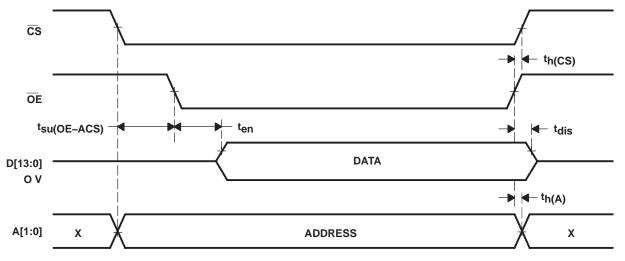

The parallel interface of the THS1401/3/8 ADC features 3-state buffers, making it possible to directly connect it to a data bus. The output buffers are enabled by driving the OE input low.

Besides the sample results, it is also possible to read back the values of the control register, the PGA register, and the offset register. Which register is read is determined by the address inputs A[1,0]. The ADC results are available at address 0.

The timing of the control signals is described in the following sections.

## PARAMETER MEASUREMENT INFORMATION

## read timing (15-pF load)

|                    | PARAMETER                          | MIN | TYP | MAX | UNIT |

|--------------------|------------------------------------|-----|-----|-----|------|

| tsu(OE-ACS)        | Address and chip select setup time | 4   |     |     | ns   |

| t <sub>en</sub>    | Output enable                      |     |     | 15  | ns   |

| <sup>t</sup> dis   | Output disable                     |     | 10  |     | ns   |

| t <sub>h(A)</sub>  | Address hold time                  | 1   |     |     | ns   |

| <sup>t</sup> h(CS) | Chip select hold time              | 0   |     |     | ns   |

NOTE: All timing parameters refer to a 50% level.

Figure 2. Read Timing

## PARAMETER MEASUREMENT INFORMATION

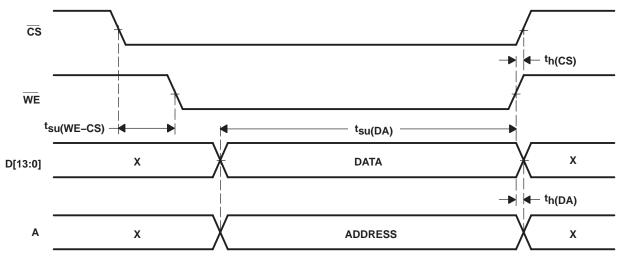

## write timing (15-pF load)

|                     | (DA) Data and address setup time |    |  |  | UNIT |

|---------------------|----------------------------------|----|--|--|------|

| tsu(WE-CS)          | Chip select setup time           | 4  |  |  | ns   |

| t <sub>su(DA)</sub> | Data and address setup time      | 29 |  |  | ns   |

| <sup>t</sup> h(DA)  | Data and address hold time       | 0  |  |  | ns   |

| t <sub>h(CS)</sub>  | Chip select hold time            | 0  |  |  | ns   |

| <sup>t</sup> wH(WE) | Write pulse duration high        | 15 |  |  | ns   |

NOTE: All timing parameters refer to a 50% level.

Figure 3. Write Timing

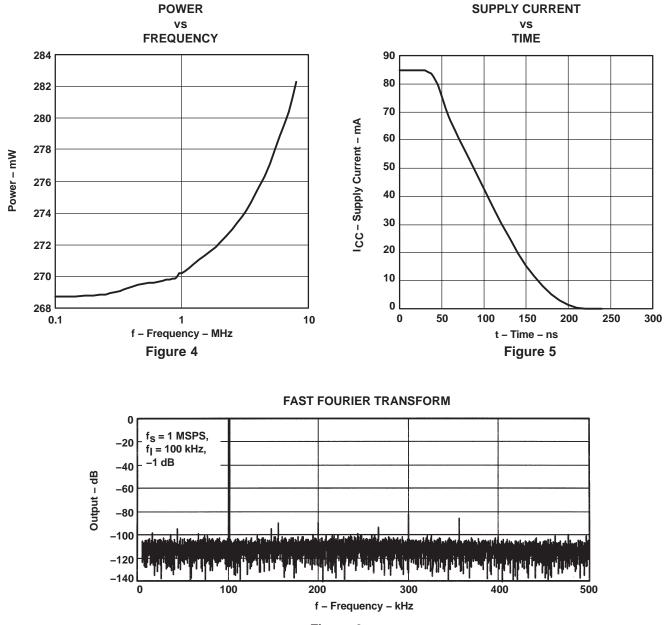

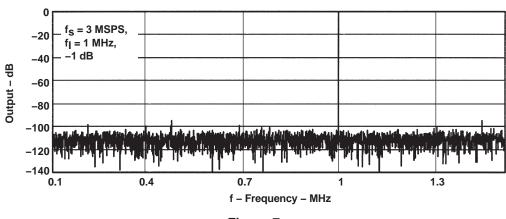

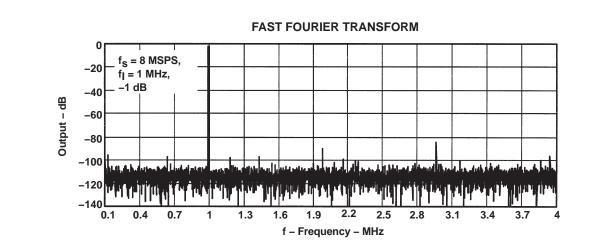

Figure 6

FAST FOURIER TRANSFORM

Figure 9

Figure 12

Figure 14

DIFFERENTIAL NONLINEARITY

## **PRINCIPLES OF OPERATION**

#### registers

The device contains several registers. The A register is selected by the values of bits A1 and A0:

| A1 | A0 | Register          |

|----|----|-------------------|

| 0  | 0  | Conversion result |

| 0  | 1  | PGA               |

| 1  | 0  | Offset            |

| 1  | 1  | Control           |

Tables 1 and 2 describe how to read the conversion results and how to configure the data converter. The default values (were applicable) show the state after a power-on reset.

Table 1. Conversion Result Register, Address 0, Read

| BIT      | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

|----------|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|-----|

| Function | MSB |     |     |     |    |    |    |    |    |    |    |    |    | LSB |

The output can be configured for 2s complement or straight binary format (see D11/control register).

The output code is given by:

| 2s com | plement:                          | Straigh | t binary:                             |

|--------|-----------------------------------|---------|---------------------------------------|

| -8192  | at $\Delta IN = -\Delta REF$      | 0       | at $\Delta IN = -\Delta REF$          |

| 0      | at $\Delta IN = 0$                | 8192    | at $\Delta IN = 0$                    |

| 8191   | $\Delta IN = +\Delta REF - 1 LSB$ | 16383   | at $\Delta IN = + \Delta REF - 1 LSB$ |

|        |                                   |         |                                       |

$1 \text{ LSB} = \frac{2\Delta \text{REF}}{16384}$

#### Table 2. PGA Gain Register, Address 1, Read/Write

| BIT      | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----------|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Function | Х   | Х   | Х   | Х   | Х  | Х  | Х  | Х  | Х  | Х  | Х  | G2 | G1 | G0 |

| Default  | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

The PGA gain is determined by writing to G2-0.

Gain (dB) =  $1dB \times G2-0$ . max = 7dB. The range of G2-0 is 0 to 7.

| Table 3. Of | ffset Register, | Address 2 | 2, Read/Write |

|-------------|-----------------|-----------|---------------|

|-------------|-----------------|-----------|---------------|

| BIT      | D13 | D12 | D11 | D10 | D9 | D8 | D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

|----------|-----|-----|-----|-----|----|----|-----|----|----|----|----|----|----|-----|

| Function | Х   | Х   | Х   | Х   | Х  | Х  | MSB |    |    |    |    |    |    | LSB |

| Default  | 0   | 0   | 0   | 0   | 0  | 0  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

The offset correction range is from -128 to 127 LSB. This value is added to the conversion results from the ADC.

**PRINCIPLES OF OPERATION**

#### Table 4. Control Register, Address 3, Read

| BIT      | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Function | PWD | REF | FOR | TM2 | TM1 | TM0 | OFF | RES |

#### Table 5. Control Register, Address 3, Write

| BIT                            | D13           | D12                                     | D11   | D10                                                                                      | D9                                                                                       | D8                                                                                     | D7                                                                | D6                                                | D5                                                      | D4                       | D3  | D2  | D1  | D0  |  |

|--------------------------------|---------------|-----------------------------------------|-------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------|--------------------------|-----|-----|-----|-----|--|

| Function                       | PWD           | REF                                     | FOR   | TM2                                                                                      | TM1                                                                                      | TM0                                                                                    | OFF                                                               | RES                                               | RES                                                     | RES                      | RES | RES | RES | RES |  |

| Default                        | 0             | 0                                       | 0     | 0                                                                                        | 0                                                                                        | 0                                                                                      | 0                                                                 | 0                                                 | 0                                                       | 0                        | 0   | 0   | 0   | 0   |  |

| PWD:<br>REF:<br>FOR:<br>TM2–0: | Refer         | er down<br>rence se<br>ut forma<br>mode | elect | 0 = int 0 = str $0 = str000 = 001 = 010 = 011 = 100 = 101 = 110 = 000 = 0000 = 00000000$ | ternal re<br>raight bi<br>both in<br>IN+ at<br>IN+ at I<br>normal<br>both in<br>IN+ at I | operati<br>puts = F<br>V <sub>CM</sub> (V<br>REF+, I<br>operati<br>puts = F<br>REF–, I | e 1<br>on<br>REF–<br>oltage a<br>N– at F<br>on<br>REF+<br>N– at V | = exter<br>= 2s co<br>at CML  <br>REF-<br>/CM (Vo | er down<br>rnal refe<br>omplem<br>pin), IN-<br>ltage at | erence<br>ent<br>- at RE |     |     |     |     |  |

| OF:<br>RES                     | Offse<br>Rese | t correc<br>rved                        | tion  |                                                                                          | 111 = IN+ at REF-, IN- at REF+0 = enable1 = disableMust be set to 0.                     |                                                                                        |                                                                   |                                                   |                                                         |                          |     |     |     |     |  |

### **APPLICATION INFORMATION**

#### driving the analog input

The THS1401/3/8 ADCs have a fully differential input. A differential input is advantageous with respect to SNR, SFDR, and THD performance because the signal peak-to-peak level is 50% of a comparable single-ended input.

There are three basic input configurations:

- Fully differential

- Transformer coupled single-ended to differential

- Single-ended

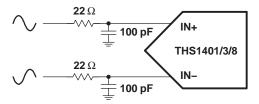

#### fully differential configuration

In this configuration, the ADC converts the difference ( $\Delta IN$ ) of the two input signals on IN+ and IN-.

Figure 19. Differential Input

The resistors and capacitors on the inputs decouple the driving source output from the ADC input and also serve as first order low pass filters to attenuate out of band noise.

The input range on both inputs is 0 V to AV<sub>DD</sub>. The full-scale value is determined by the voltage reference. The positive full-scale output is reached, if  $\Delta$ IN equals  $\Delta$ REF, the negative full-scale output is reached, if  $\Delta$ IN equals  $-\Delta$ REF.

| ∆IN [V] | OUTPUT       |

|---------|--------------|

| –∆REF   | – full scale |

| 0       | 0            |

| ∆REF    | + full scale |

## **APPLICATION INFORMATION**

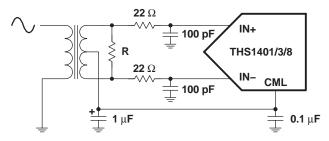

#### transformer coupled single-ended to differential configuration

If the application requires the best SNR, SFDR, and THD performance, the input should be transformer coupled.

The signal amplitude on both inputs of the ADC is one half as high as in a single-ended configuration thus increasing the ADC ac performance.

Figure 20. Transformer Coupled

The following table shows the input voltages for negative full-scale output, zero output, and positive full-scale output:

| IN [VPEAK]              | OUTPUT [PEAK]             |  |  |  |  |  |  |  |  |

|-------------------------|---------------------------|--|--|--|--|--|--|--|--|

| $-\Delta REF$           | – full scale†             |  |  |  |  |  |  |  |  |

| 0                       | 0                         |  |  |  |  |  |  |  |  |

| ∆REF                    | + full scale <sup>†</sup> |  |  |  |  |  |  |  |  |

| † n = 1 (winding ratio) |                           |  |  |  |  |  |  |  |  |

The resistor R of the transformer coupled input configuration must be set to match the signal source impedance  $R = n^2 Rs$ , where Rs is the source impedance and n is the transformer winding ratio.

## **APPLICATION INFORMATION**

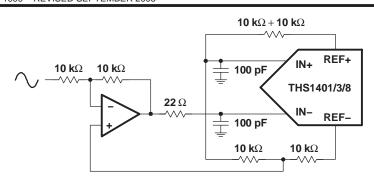

#### single-ended configuration

In this configuration, the input signal is level shifted by  $\Delta REF/2$ .

Figure 21. Single-Ended With Level Shift

The following table shows the input voltages for negative full-scale output, zero output, and positive full-scale output:

| ∆ <b>IN+ [V]</b> | OUTPUT       |

|------------------|--------------|

| $-\Delta REF$    | – full scale |

| 0                | 0            |

| ΔREF             | + full scale |

Note that the resistors of the op-amp and the op-amp all introduce gain and offset errors. Those errors can be trimmed by varying the values of the resistors.

Because of the added offset, the op-amp does not necessarily operate in the best region of its transfer curve (best linearity around zero) and therefore may introduce unacceptable distortion. For ac signals, an alternative is described in the following section.

## **APPLICATION INFORMATION**

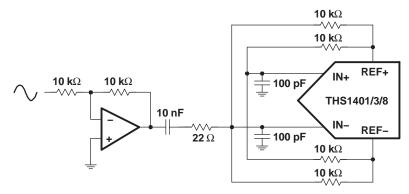

#### AC-coupled single-ended configuration

If the application does not require the signal bandwidth to include dc, the level shift shown in Figure 21 is not necessary.

Figure 22. Single-Ended With Level Shift

Because the signal swing on the op-amp is centered around ground, it is more likely that the signal stays within the linear region of the op-amp transfer function, thus increasing the overall ac performance.

| IN [V <sub>PEAK</sub> ] | OUTPUT [PEAK]                    |

|-------------------------|----------------------------------|

| $-\Delta REF$           | <ul> <li>– full scale</li> </ul> |

| 0                       | 0                                |

| ΔREF                    | + full scale                     |

Compared to the transformer-coupled configuration, the swing on IN– is twice as big, which can decrease the ac performance (SNR, SFD, and THD).

#### **APPLICATION INFORMATION**

#### internal/external reference operation

The THS1401/3/8 ADC can either be operated using the built-in band gap reference or using an external precision reference in case very high dc accuracy is needed.

The REF+ and REF+ outputs are given by:

REF + = VBG

$$\left(1 + \frac{2}{3}\right)$$

and REF-

If the built-in reference is used, VBG equals 1.5 V which results in REF+ = 2.5 V, REF- = 0.5 V and  $\triangle$ REF = 2 V.

The internal reference can be disabled by writing 1 to D12 (REF) in the control register (address 3). The band gap reference is then disconnected and can be substituted by a voltage on the VBG pin.

#### programmable gain amplifier

The on-chip programmable gain amplifier (PGA) has eight gain settings. The gain can be changed by writing to the PGA gain register (address 1). The range is 0 to 7dB in steps of one dB.

#### out of range indication

The OV output of the ADC indicates an out of range condition. Every time the difference on the analog inputs exceeds the differential reference, this signal is asserted. This signal is updated the same way as the digital data outputs and therefore subject to the same pipeline delay.

#### offset compensation

With the offset register it is possible to automatically compensate system offset errors, including errors caused by additional signal conditioning circuitry. If the offset compensation is enabled (D7 (OFF) in the control register), the value in the offset register (address 2) is automatically added to the output of the ADC.

In order to set the correct value of the offset compensation register, the ADC result when the input signal is 0 must be read by the host processor and written to the offset register (address 2).

#### test modes

The ADC core operation can be tested by selecting one of the available test modes (see control register description). The test modes apply various voltages to the differential input depending on the setting in the control register.

#### digital I/O

The digital inputs and outputs of the THS1401/3/8 ADC are 3-V CMOS compatible. In order to avoid current feed back errors, the capacitive load on the digital outputs should be as low as possible (50 pF max). Series resistors (100  $\Omega$ ) on the digital outputs can improve the performance by limiting the current during output transitions.

The parallel interface of the THS1401/3/8 ADC features 3-state buffers, making it possible to directly connect it to a data bus. The output buffers are enabled by driving the  $\overline{OE}$  input low.

Refer to the read and write timing diagrams in the parameter measurement information section for information on read and write access.

**Revision History**

| DATE | REV | PAGE | SECTION                 | DESCRIPTION                                                                                                                                                                                                                                                                              |

|------|-----|------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |     | 1    | —                       | Updated page 1 format and layout.                                                                                                                                                                                                                                                        |

|      |     | 1    | —                       | Moved funtional block diagram from page 2.                                                                                                                                                                                                                                               |

|      |     | 2    | —                       | Moved Terminal Function table from page 3.                                                                                                                                                                                                                                               |

|      |     | 2    | —                       | Moved Absolute Maximum table from page 4.                                                                                                                                                                                                                                                |

|      |     | 3    | —                       | Moved package pinout from page 1.                                                                                                                                                                                                                                                        |

| 9/05 | D   | 3    | —                       | Moved Ordering Options table from page 2.                                                                                                                                                                                                                                                |

|      |     | 15   | Principles of Operation | Table 1. In section 2s complement: $8191 \Delta IN = -\Delta REF - 1 LSB$ changed to $8191 \Delta IN = +\Delta REF - 1 LSB$ . In section Straight Binary: $16383 at \Delta IN = -\Delta REF - 1 LSB$ should be changed to $16383 \Delta IN = +\Delta REF - 1 LSB$                        |

|      |     | 16   | Principles of Operation | Table 5. In section TM2–0: Test Mode: $010 = IN+ at V_{REF}/2$ , $IN- at REF-$ , changed to, $010 = IN+ at V_{CM}$ (Voltage at CML pin), $IN- at REF-$ . Same section: $110 = IN+ at REF-$ , $IN- at V_{REF}/2$ , changed to, $110 = IN+ at REF-$ , $IN- at V_{CM}$ (Voltage at CML pin) |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

6-Feb-2017

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)            | Lead/Ball Finish<br>(6) | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|----------------------------|-------------------------|---------------------|--------------|-------------------------|---------|

| 5962-0051101NXD  | ACTIVE        | HTQFP        | PHP                | 48   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-3-260C-168 HR | -55 to 125   | 0051101<br>NXD          | Samples |

| THS1401IPFB      | ACTIVE        | TQFP         | PFB                | 48   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR | -40 to 85    | TJ1401                  | Samples |

| THS1403IPFB      | ACTIVE        | TQFP         | PFB                | 48   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR | -40 to 85    | TJ1403                  | Samples |

| THS1408IPFB      | ACTIVE        | TQFP         | PFB                | 48   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR | -40 to 85    | TJ1408                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

www.ti.com

6-Feb-2017

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF THS1408, THS1408M :

- Catalog: THS1408

- Enhanced Product: THS1408-EP, THS1408-EP

- Military: THS1408M

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Enhanced Product Supports Defense, Aerospace and Medical Applications

- Military QML certified for Military and Defense Applications

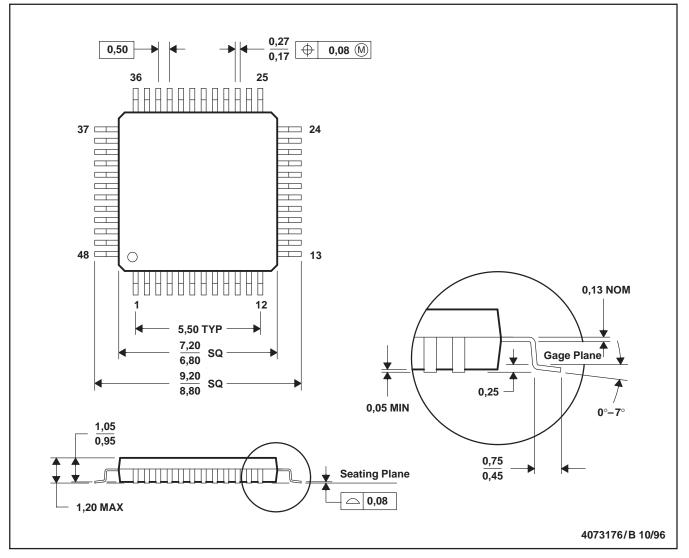

# **MECHANICAL DATA**

MTQF019A - JANUARY 1995 - REVISED JANUARY 1998

#### PFB (S-PQFP-G48)

PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-026

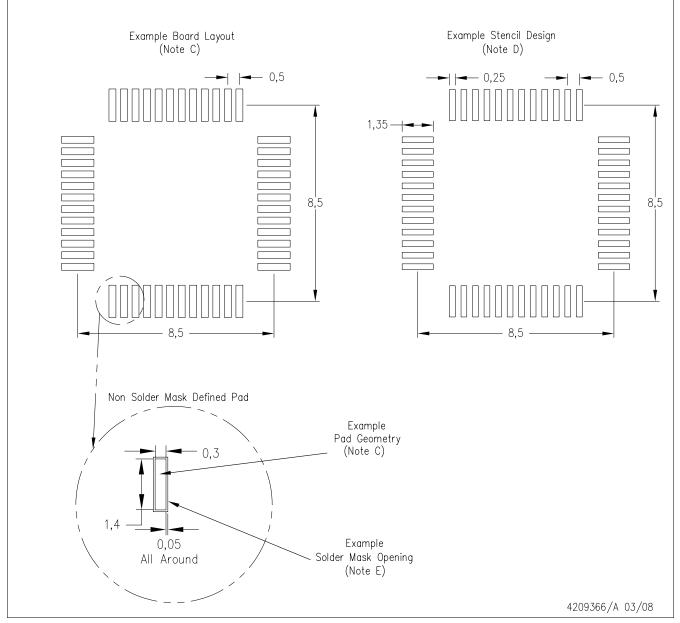

PFB (S-PQFP-G48)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

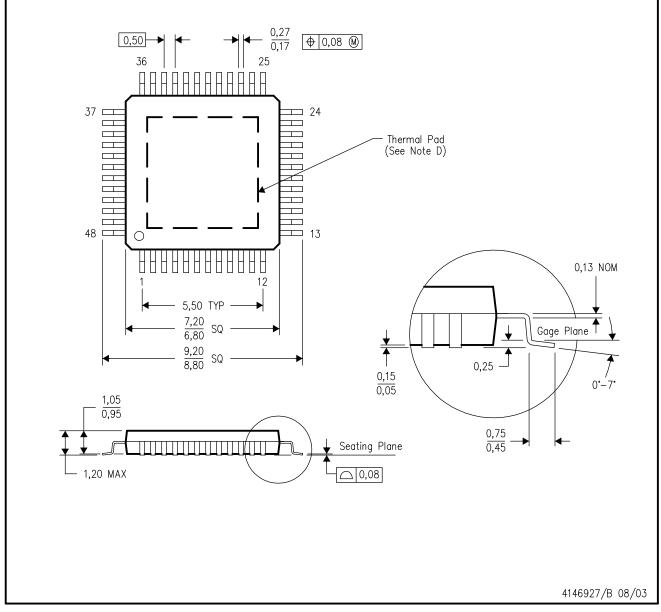

PHP (S-PQFP-G48)

$\textbf{PowerPAD}^{\,\mathbb{M}} \quad \textbf{PLASTIC} \ \textbf{QUAD} \ \textbf{FLATPACK}$

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Falls within JEDEC MS-026

PowerPAD is a trademark of Texas Instruments.

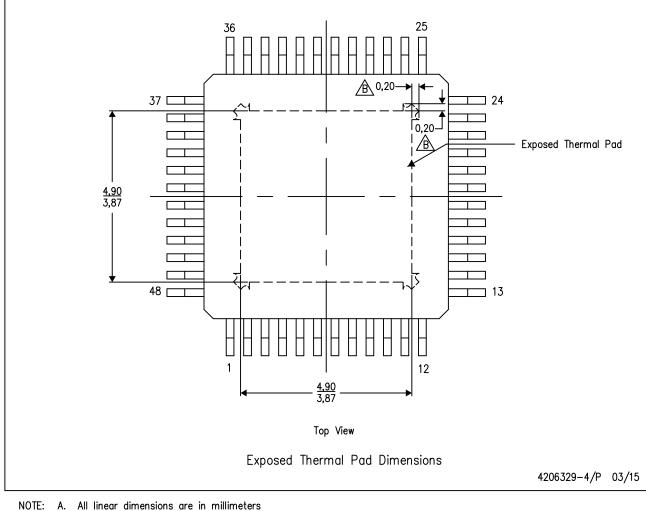

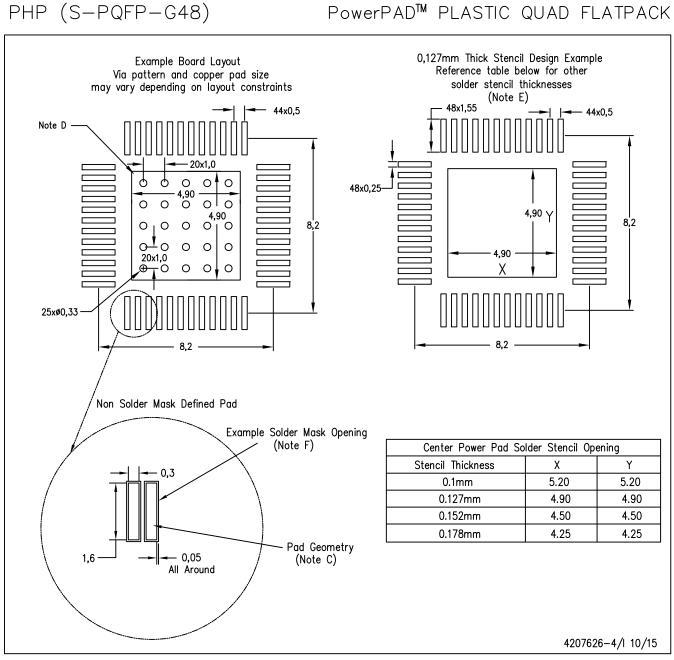

# PHP (S-PQFP-G48)

# PowerPAD™ PLASTIC QUAD FLATPACK

THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

A Tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <http://www.ti.com>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

F. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting options for vias placed in the thermal pad.

PowerPAD is a trademark of Texas Instruments

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

TI's published terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products that TI has qualified and released to market. Additional terms may apply to the use or sale of other types of TI products and services.

Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such reproduced documentation. Information of third parties may be subject to additional restrictions. Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyers and others who are developing systems that incorporate TI products (collectively, "Designers") understand and agree that Designers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers' applications and compliance of their applications (and of all TI products used in or for Designers' applications) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to their applications, Designer has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any applications that include TI products, Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.

TI's provision of technical, application or other design advice, quality characterization, reliability data or other services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using TI Resources in any way, Designer (individually or, if Designer is acting on behalf of a company, Designer's company) agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

Designer is authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949 and ISO 26262), TI is not responsible for any failure to meet such industry standard requirements.

Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards, such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and requirements. Using products in an application does not by itself establish any safety features in the application. Designers must ensure compliance with safety-related requirements and standards applicable to their applications. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equipment includes, without limitation, all medical devices identified by the U.S. Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.

TI may expressly designate certain products as completing a particular qualification (e.g., Q100, Military Grade, or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers' own risk. Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's noncompliance with the terms and provisions of this Notice.

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated