# Data Manual

Literature Number: SLLU099B AUGUST 2007–Revised February 2008

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SLLU099B-AUGUST 2007-REVISED FEBRUARY 2008

# Contents

| 1 | Introd       |           |                                                |           |  |  |  |

|---|--------------|-----------|------------------------------------------------|-----------|--|--|--|

|   | 1.1 Features |           |                                                |           |  |  |  |

|   | 1.2          | Descript  | ion                                            | <u>10</u> |  |  |  |

|   | 1.3          | Termina   | I Assignments                                  | 14        |  |  |  |

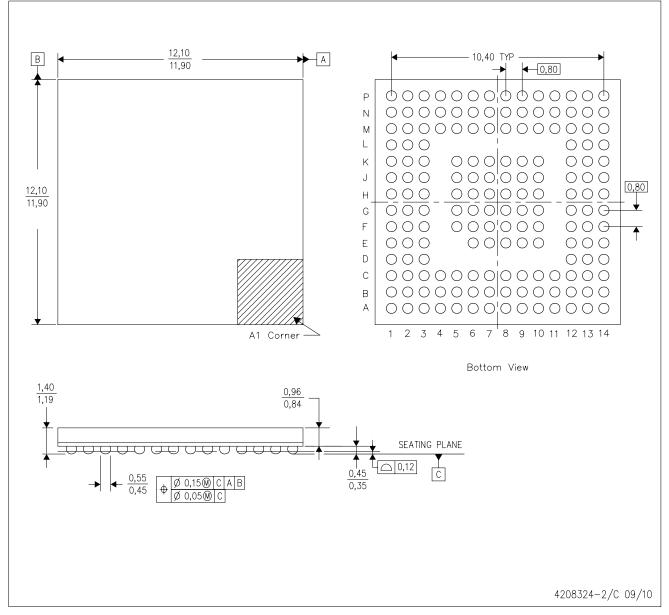

|   |              | 1.3.1     | Top View                                       | <u>14</u> |  |  |  |

|   |              | 1.3.2     | Bottom View                                    | <u>15</u> |  |  |  |

|   | 1.3.3        | Signals   | Sorted by Terminal Number                      | <u>16</u> |  |  |  |

|   | 1.3.4        | Signals   | Sorted by Name                                 | <u>17</u> |  |  |  |

|   | 1.3.5        | Termina   | I Functions                                    | <u>18</u> |  |  |  |

| 2 | Electr       | ical Cha  | aracteristics                                  | <u>26</u> |  |  |  |

|   | 2.1          | Absolute  | e Maximum Ratings                              | <u>26</u> |  |  |  |

|   | 2.2          | Recomn    | nended Operating Conditions                    | <u>26</u> |  |  |  |

|   | 2.3          | Electrica | al Characteristics, PHY Driver                 | <u>28</u> |  |  |  |

|   | 2.4          |           | al Characteristics, PHY Receiver               |           |  |  |  |

|   | 2.5          |           | al Characteristics, General                    |           |  |  |  |

|   | 2.6          | Thermal   | Characteristics                                | <u>29</u> |  |  |  |

|   | 2.7          | Switchin  | g Characteristics for PHY Portion              | <u>30</u> |  |  |  |

|   | 2.8          | Switchin  | g Characteristics for PCI Interface            | <u>30</u> |  |  |  |

| 3 | PHY S        | Section   | Register Configuration                         | <u>31</u> |  |  |  |

| 4 | PHY S        | Section   | Application Information                        | <u>37</u> |  |  |  |

|   | 4.1          | Power-C   | Class Programming                              | 37        |  |  |  |

|   | 4.2          | Power-L   | Jp Reset                                       | <u>39</u> |  |  |  |

|   | 4.3          | Crystal ( | Oscillator Selection                           | <u>39</u> |  |  |  |

|   | 4.4          | Bus Res   | set                                            | <u>40</u> |  |  |  |

| 5 | Princi       | iples of  | Operation (IEEE Std 1394b-2002 Interface)      | 42        |  |  |  |

|   | 5.1          | LLC Sec   | ction Service Request                          | <u>43</u> |  |  |  |

|   | 5.2          | Status T  | ransfer                                        | <u>46</u> |  |  |  |

|   | 5.3          | Receive   |                                                | <u>48</u> |  |  |  |

|   | 5.4          | Transmi   | t                                              | <u>51</u> |  |  |  |

| 6 | TSB8         | 3AA23 I   | Link Layer Controller Programming Model        | 53        |  |  |  |

|   | 6.1          | PCI Cor   | figuration Registers                           | <u>53</u> |  |  |  |

|   |              | 6.1.1     | Vendor ID Register                             | <u>54</u> |  |  |  |

|   |              | 6.1.2     | Device ID Register                             | <u>54</u> |  |  |  |

|   |              | 6.1.3     | Command Register                               | <u>54</u> |  |  |  |

|   |              | 6.1.4     | Status Register                                | <u>55</u> |  |  |  |

|   |              | 6.1.5     | Revision ID Register                           | <u>56</u> |  |  |  |

|   |              | 6.1.6     | Class Code Register                            | <u>57</u> |  |  |  |

|   |              | 6.1.7     | Cache Line Size Register                       | <u>58</u> |  |  |  |

|   |              | 6.1.8     | Latency Timer Register                         | <u>58</u> |  |  |  |

|   |              | 6.1.9     | Header Type Register                           | <u>58</u> |  |  |  |

|   |              | 6.1.10    | Built-In Self-Test (BIST) Register             | <u>59</u> |  |  |  |

|   |              | 6.1.11    | OHCI Base Address Register                     | <u>59</u> |  |  |  |

|   |              | 6.1.12    | TI Extension Base Address Register             | <u>60</u> |  |  |  |

|   |              | 6.1.13    | CardBus CIS Base Address Register              | <u>60</u> |  |  |  |

|   |              | 6.1.14    | CardBus CIS Pointer Register                   | <u>61</u> |  |  |  |

|   |              | 6.1.15    | Subsystem Vendor ID Register                   | <u>62</u> |  |  |  |

|   |              | 6.1.16    | Subsystem ID Register                          | <u>62</u> |  |  |  |

|   |              | 6.1.17    | Power Management Capabilities Pointer Register | <u>62</u> |  |  |  |

|   |              | 6.1.18    | Interrupt Line Register                        |           |  |  |  |

|   |              | 6.1.19    | Interrupt Pin Register                         | <u>63</u> |  |  |  |

|     | 6.1.20 | Minimum Grant Register                         | <u>63</u> |

|-----|--------|------------------------------------------------|-----------|

|     | 6.1.21 | Maximum Latency Register                       | <u>64</u> |

|     | 6.1.22 | OHCI Control Register                          | <u>64</u> |

|     | 6.1.23 | Capability ID Register                         | <u>65</u> |

|     | 6.1.24 | Next-Item Pointer Register                     | <u>65</u> |

|     | 6.1.25 | Power Management Capabilities Register         | <u>65</u> |

|     | 6.1.26 | Power Management Control and Status Register   | <u>66</u> |

|     | 6.1.27 | Power Management Extension Register            | <u>67</u> |

|     | 6.1.28 | Power Management Data Register                 | <u>67</u> |

|     | 6.1.29 | Multifunction Select Register                  | <u>68</u> |

|     | 6.1.30 | Miscellaneous Configuration Register           | <u>68</u> |

|     | 6.1.31 | LLC Section Enhancement Control Register       |           |

|     | 6.1.32 | Subsystem Access Register                      |           |

|     | 6.1.33 | GPIO Control Register                          | <u>72</u> |

| 6.2 | OHCI R | egisters                                       | <u>73</u> |

|     | 6.2.1  | OHCI Version Register                          | <u>75</u> |

|     | 6.2.2  | GUID ROM Register                              | <u>75</u> |

|     | 6.2.3  | Asynchronous Transmit Retries Register         | <u>76</u> |

|     | 6.2.4  | CSR Data Register                              | 77        |

|     | 6.2.5  | CSR Compare Data Register                      | <u>77</u> |

|     | 6.2.6  | CSR Control Register                           | <u>77</u> |

|     | 6.2.7  | Configuration ROM Header Register              | <u>78</u> |

|     | 6.2.8  | Bus Identification Register                    | <u>78</u> |

|     | 6.2.9  | Bus Options Register                           | <u>78</u> |

|     | 6.2.10 | GUID High Register                             | <u>79</u> |

|     | 6.2.11 | GUID Low Register                              | <u>80</u> |

|     | 6.2.12 | Configuration ROM Mapping Register             | <u>80</u> |

|     | 6.2.13 | Posted Write Address Low Register              | <u>80</u> |

|     | 6.2.14 | Posted Write Address High Register             | <u>81</u> |

|     | 6.2.15 | OHCI Vendor ID Register                        | <u>81</u> |

|     | 6.2.16 | Host Controller Control Register               | <u>82</u> |

|     | 6.2.17 | Self-ID Buffer Pointer Register                | <u>83</u> |

|     | 6.2.18 | Self-ID Count Register                         | <u>84</u> |

|     | 6.2.19 | Isochronous Receive Channel Mask High Register | <u>85</u> |

|     | 6.2.20 | Isochronous Receive Channel Mask Low Register  | <u>85</u> |

|     | 6.2.21 | Interrupt Event Register                       | <u>86</u> |

|     | 6.2.22 | Interrupt Mask Register                        | <u>88</u> |

|     | 6.2.23 | Isochronous Transmit Interrupt Event Register  | <u>90</u> |

|     | 6.2.24 | Isochronous Transmit Interrupt Mask Register   | <u>91</u> |

|     | 6.2.25 | Isochronous Receive Interrupt Event Register   | <u>91</u> |

|     | 6.2.26 | Isochronous Receive Interrupt Mask Register    | <u>92</u> |

|     | 6.2.27 | Initial Bandwidth Available Register           | <u>92</u> |

|     | 6.2.28 | Initial Channels Available High Register       | <u>92</u> |

|     | 6.2.29 | Initial Channels Available Low Register        | <u>93</u> |

|     | 6.2.30 | Fairness Control Register                      | <u>93</u> |

|     | 6.2.31 | LLC Section Control Register                   | <u>94</u> |

|     | 6.2.32 | Node Identification Register                   | <u>94</u> |

|     | 6.2.33 | PHY Layer Control Register                     | <u>95</u> |

|     | 6.2.34 | Isochronous Cycle Timer Register               | <u>96</u> |

|     | 6.2.35 | Asynchronous Request Filter High Register      | <u>96</u> |

|     | 6.2.36 | Asynchronous Request Filter Low Register       | <u>97</u> |

|     | 6.2.37 | Physical Request Filter High Register          | <u>97</u> |

|     | 6.2.38 | Physical Request Filter Low Register           |           |

|     |        |                                                |           |

SLLU099B-AUGUST 2007-REVISED FEBRUARY 2008

|      | 6.2.39   | Physical Upper Bound Register (Optional Register)       | . <u>99</u> |

|------|----------|---------------------------------------------------------|-------------|

|      | 6.2.40   | Asynchronous Context Control Register                   | <u>. 99</u> |

|      | 6.2.41   | Asynchronous Context Command Pointer Register           | <u>100</u>  |

|      | 6.2.42   | Isochronous Transmit Context Control Register           | <u>100</u>  |

|      | 6.2.43   | Isochronous Transmit Context Command Pointer Register   | <u>101</u>  |

|      | 6.2.44   | Isochronous Receive Context Control Register            | <u>102</u>  |

|      | 6.2.45   | Isochronous Receive Context Command Pointer Register    | <u>104</u>  |

|      | 6.2.46   | Isochronous Receive Context Match Register              | <u>104</u>  |

| 6.3  | TI Exter | nsion Registers                                         | <u>105</u>  |

|      | 6.3.1    | DV Timestamp Enhancements                               | <u>105</u>  |

|      | 6.3.2    | MPEG2 Timestamp Procedure                               | <u>106</u>  |

|      | 6.3.3    | Isochronous Receive Digital Video Enhancements          | <u>106</u>  |

|      | 6.3.4    | Isochronous Receive Digital Video Enhancements Register | <u>106</u>  |

|      | 6.3.5    | Link Enhancement Register                               | <u>107</u>  |

|      | 6.3.6    | Timestamp Offset Register                               | <u>110</u>  |

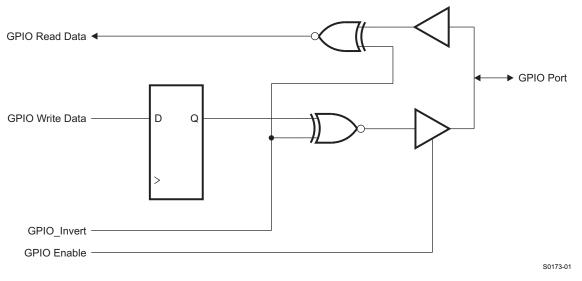

| Gene | ral-Purp | oose Input/Output (GPIO) Interface                      | 111         |

|      | •        | DM Interface                                            |             |

7 8

SLLU099B-AUGUST 2007-REVISED FEBRUARY 2008

# List of Figures

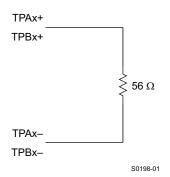

| 2-1 | Test Load Diagram                                           | <u>30</u>  |

|-----|-------------------------------------------------------------|------------|

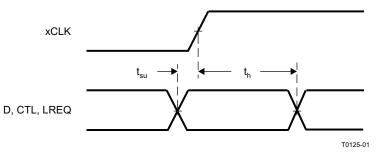

| 2-2 | Setup and Hold Time Waveforms for Dx, CTLx, and LREQ Inputs | <u>30</u>  |

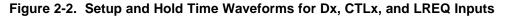

| 2-3 | Dx and CTLx Output Delay Relative to xCLK Waveforms         | <u>31</u>  |

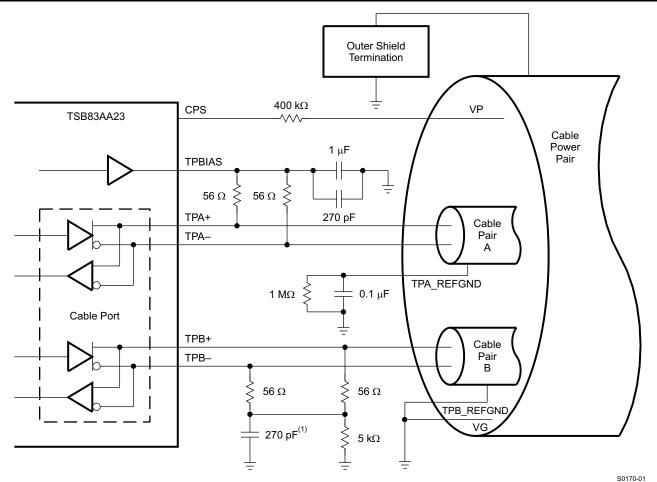

| 4-1 | Typical Twisted Pair IEEE Std 1394a-2000 Cable Connections  | <u>38</u>  |

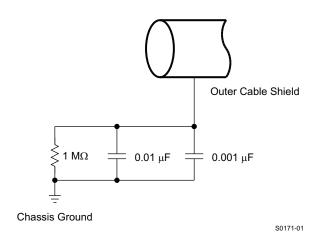

| 4-2 | Typical DC-Isolated Outer Shield Termination                | <u>38</u>  |

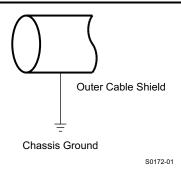

| 4-3 | Non-DC-Isolated Outer Shield Termination                    | <u>39</u>  |

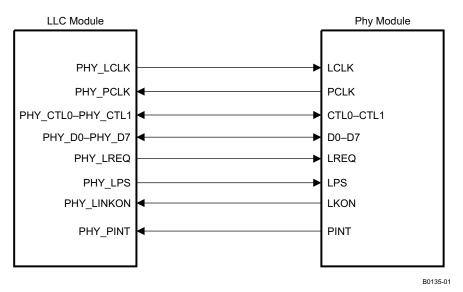

| 5-1 | PHY Section-LLC Section Interface                           | <u>42</u>  |

| 5-2 | LREQ/PHY_LREQ Request Stream                                | <u>43</u>  |

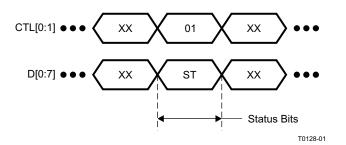

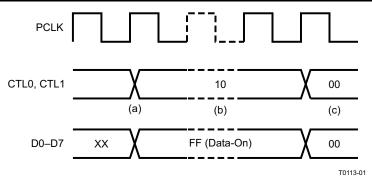

| 5-3 | Bus Status Transfer                                         | <u>47</u>  |

| 5-4 | PINT (PHY Section Interrupt) Stream                         | <u>47</u>  |

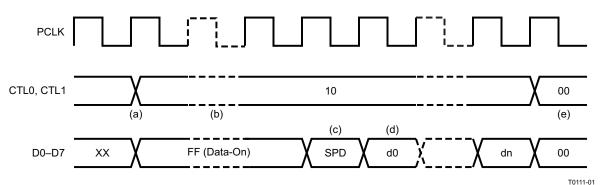

| 5-5 | Normal Packet Reception                                     | <u>49</u>  |

| 5-6 | Normal Packet Reception With Optional Bus Status Transfer   | <u>49</u>  |

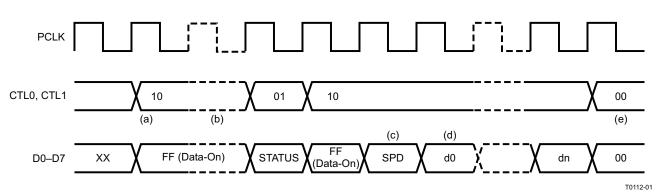

| 5-7 | Null Packet Reception                                       | <u>50</u>  |

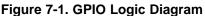

| 7-1 | GPIO Logic Diagram                                          | <u>111</u> |

SLLU099B-AUGUST 2007-REVISED FEBRUARY 2008

# List of Tables

| 3-1  | Base Register Configuration                                            | <u>31</u> |

|------|------------------------------------------------------------------------|-----------|

| 3-2  | Base Register Field Descriptions                                       | <u>31</u> |

| 3-3  | Page-0 (Port-Status) Register Configuration                            | <u>33</u> |

| 3-4  | Page-0 (Port-Status) Register Field Descriptions                       | <u>34</u> |

| 3-5  | Page 1 (Vendor ID) Register Configuration                              | <u>35</u> |

| 3-6  | Page 1 (Vendor ID) Register Field Descriptions                         | <u>36</u> |

| 3-7  | Page 7 (Vendor-Dependent) Register Configuration                       | <u>36</u> |

| 3-8  | Page 7 (Vendor-Dependent) Register Field Descriptions                  | <u>36</u> |

| 4-1  | Power Class Descriptions                                               | <u>37</u> |

| 5-1  | CTL Encoding When PHY Section Has Control of the Bus                   | <u>43</u> |

| 5-2  | CTL Encoding When LLC Section Has Control of the Bus                   | <u>43</u> |

| 5-3  | Request Stream Bit Length                                              | <u>44</u> |

| 5-4  | Request-Type Encoding                                                  | <u>44</u> |

| 5-5  | Bus Request                                                            | <u>45</u> |

| 5-6  | Bus-Request Format Encoding                                            | <u>45</u> |

| 5-7  | Bus-Request Speed Encoding                                             | <u>45</u> |

| 5-8  | Read Register Request                                                  | <u>45</u> |

| 5-9  | Write Register Request                                                 | <u>46</u> |

| 5-10 | Link Notification Request                                              | <u>46</u> |

| 5-11 | Status Bits                                                            | <u>47</u> |

| 5-12 | PHY Status Transfer Encoding                                           | <u>48</u> |

| 5-13 | Register Read (Solicited and Unsolicited) PHY Status Transfer Encoding | <u>48</u> |

| 5-14 | Receive Speed Codes and Format                                         | <u>50</u> |

| 5-15 | Link-Request-Type Encoding During Packet Transmission                  | <u>51</u> |

| 5-16 | Link-Request Speed-Code Encoding During Packet Transmission            | <u>51</u> |

| 5-17 | Link-Request Format Encoding During Packet Transmission                | <u>52</u> |

| 5-18 | Subaction End-Notification Encoding During Packet Transmission         | <u>52</u> |

| 5-19 | Format Type During Grant Cycle                                         | <u>52</u> |

| 5-20 | Grant Type Values During Grant Cycle                                   | <u>52</u> |

| 5-21 | Speed Type Values During Grant Cycle                                   | <u>52</u> |

| 6-1  | Bit Field Access Tag Descriptions                                      | <u>53</u> |

| 6-2  | PCI Configuration Register Map                                         | <u>53</u> |

| 6-3  | Command Register Description                                           | <u>55</u> |

| 6-4  | Status Register Description                                            | <u>56</u> |

| 6-5  | Revision ID Register Description                                       | <u>56</u> |

| 6-6  | Class Code Register Description                                        | <u>57</u> |

| 6-7  | Cache Line Size Register Description                                   | <u>58</u> |

| 6-8  | Latency Timer Register Description                                     | <u>58</u> |

| 6-9  | Header Type Register Description                                       | <u>58</u> |

| 6-10 | Built-In Self-Test (BIST) Register Description             | <u>59</u> |

|------|------------------------------------------------------------|-----------|

| 6-11 | OHCI Base Address Register Description                     | <u>59</u> |

| 6-12 | TI Base Address Register Description                       | <u>60</u> |

| 6-13 | CardBus CIS Base Address Register Description              | <u>61</u> |

| 6-14 | CardBus CIS Pointer Register Description                   | <u>61</u> |

| 6-15 | Subsystem Vendor ID Register Description                   | <u>62</u> |

| 6-16 | Subsystem ID Register Description                          | <u>62</u> |

| 6-17 | Interrupt Line Register Description                        | <u>63</u> |

| 6-18 | Interrupt Line and Pin Register Description                | <u>63</u> |

| 6-19 | Minimum Grant Register Description                         | <u>63</u> |

| 6-20 | Maximum Latency Register Description                       | <u>64</u> |

| 6-21 | OHCI Control Register Description                          | <u>64</u> |

| 6-22 | Capability ID Register Description                         | <u>65</u> |

| 6-23 | Next-Item Pointer Register Description                     | <u>65</u> |

| 6-24 | Power Management Capabilities Register Description         | <u>66</u> |

| 6-25 | Power Management Control and Status Register Description   | <u>66</u> |

| 6-26 | Power Management Extension Register Description            | <u>67</u> |

| 6-27 | Power Management Data Register Description                 | <u>67</u> |

| 6-28 | Multifunction Select Register                              | <u>68</u> |

| 6-29 | Miscellaneous Configuration Register                       | <u>69</u> |

| 6-30 | LLC Section Enhancement Control Register Description       | <u>71</u> |

| 6-31 | Subsystem Access Register Description                      | <u>72</u> |

| 6-32 | GPIO Control Register Description                          | <u>72</u> |

| 6-33 | OHCI Register Map                                          | <u>73</u> |

| 6-34 | OHCI Version Register Description                          | <u>75</u> |

| 6-35 | GUID ROM Register Description                              | <u>76</u> |

| 6-36 | Asynchronous Transmit Retries Register Description         | <u>76</u> |

| 6-37 | CSR Control Register Description                           | <u>77</u> |

| 6-38 | Configuration ROM Header Register Description              | <u>78</u> |

| 6-39 | Bus Options Register Description                           | <u>79</u> |

| 6-40 | Configuration ROM Mapping Register Description             | <u>80</u> |

| 6-41 | Posted Write Address Low Register Description              | <u>80</u> |

| 6-42 | Posted Write Address High Register Description             | <u>81</u> |

| 6-43 | Vendor ID Register Description                             | <u>82</u> |

| 6-44 | Host Controller Control Register Description               | <u>82</u> |

| 6-45 | Self-ID Count Register Description                         | <u>84</u> |

| 6-46 | Isochronous Receive Channel Mask High Register Description | <u>85</u> |

| 6-47 | Isochronous Receive Channel Mask Low Register Description  | <u>85</u> |

| 6-48 | Interrupt Event Register Description                       | <u>87</u> |

| 6-49 | Interrupt Mask Register Description                        | <u>89</u> |

| 6-50 | Isochronous Transmit Interrupt Event Register Description  | <u>91</u> |

# TSB83AA23 IEEE Std 1394b-2002

## **PHY and OHCI Link Device**

| 6-51 | Isochronous Receive Interrupt Event Register Description            | <u>92</u> |

|------|---------------------------------------------------------------------|-----------|

| 6-52 | Initial Bandwidth Available Register Description                    | <u>92</u> |

| 6-53 | Initial Channels Available High Register Description                | <u>93</u> |

| 6-54 | Initial Channels Available High Register Description                | <u>93</u> |

| 6-55 | Fairness Control Register Description                               | <u>94</u> |

| 6-56 | LLC Section Control Register Description                            | <u>94</u> |

| 6-57 | Node Identification Register Description                            | <u>95</u> |

| 6-58 | PHY Layer Control Register Description                              | <u>95</u> |

| 6-59 | Isochronous Cycle Timer Register Description                        | <u>96</u> |

| 6-60 | Asynchronous Request Filter High Register Description               | <u>97</u> |

| 6-61 | Asynchronous Request Filter Low Register Description                | <u>97</u> |

| 6-62 | Physical Request Filter High Register Description                   | <u>98</u> |

| 6-63 | Physical Request Filter Low Register Description                    | <u>98</u> |

| 6-64 | Asynchronous Context Control Register Description                   | <u>99</u> |

| 6-65 | Asynchronous Context Command Pointer Register Description           | 00        |

| 6-66 | Isochronous Transmit Context Control Register Description           | 01        |

| 6-67 | Isochronous Receive Context Control Register Description            | <u>03</u> |

| 6-68 | Isochronous Receive Context Match Register Description              | 05        |

| 6-69 | TI Extension Register Map                                           | 05        |

| 6-70 | Isochronous Receive Digital Video Enhancements Register Description | 07        |

| 6-71 | Link Enhancement Register Description                               | 09        |

| 6-72 | Timestamp Offset Register Description                               | 10        |

| 8-1  | Serial EEPROM Map                                                   | 13        |

## 1 Introduction

#### 1.1 Features

- Fully Supports Provisions of IEEE Std 1394b-2002 Revision 1.33+ at 1-Gigabit Signaling Rates

- Fully Supports Provisions of IEEE Std 1394a-2000 and IEEE Std 1394-1995 for High-Performance Serial Bus

- Fully Interoperable With Firewire<sup>™</sup>, i.LINK<sup>™</sup>, and SB1394 Implementations of IEEE Std 1394

- Provides Three Fully Backward-Compatible, (IEEE Std 1394a-2000 Fully Compliant) Bilingual IEEE Std 1394b-2002 Cable Ports at up to 800 Megabits per Second (Mbps)

- Full IEEE Std 1394a-2000 Support Includes:

- Connection Debounce

- Arbitrated Short Reset

- Multispeed Concatenation

- Arbitration Acceleration

- Fly-By Concatenation

- Port Disable/Suspend/Resume

- Extended Resume Signaling for Compatibility With Legacy Digital Video (DV) Devices

- Power-Down Features to Conserve Energy in Battery-Powered Applications

- Low-Power Sleep Mode

- Fully Compliant With Open Host Controller Interface (OHCI) Requirements

- Cable Power Presence Monitoring

- Cable Ports Monitor Line Conditions for Active Connection to Remote Node

- Register Bits Give Software Control of Contender Bit, Power-Class Bits, Link Active Control Bit, and IEEE Std 1394a-2000 Features

- Interoperable With Other 1394 Physical Layers (PHYs) Using 1.8-V, 3.3-V, and 5-V Supplies

- Low-Jitter, External Crystal Oscillator Provides Transmit and Receive Data at 100/200/400/800 Mbps and Link-Layer Controller (LLC) Clock at 49.152 MHz and 98.304 MHz

- Separate Bias (TPBIAS) for Each Port

- Software Device Reset (SWR)

- Fail-Safe Circuitry Senses Sudden Loss of Power to the Device and Disables Ports to Ensure That TSB83AA23 Does Not Load TPBIAS of Any Connected Device and Blocks Any Leakage From the Port Back to Power Plane

- IEEE Std 1394a-2000-Compliant Common-Mode Noise Filter on Incoming Bias Detect Circuit to Filter Out Crosstalk Noise

- Port Programmable to Force IEEE Std 1394a-2000 Mode to Allow Use of IEEE Std 1394a-2000 Connectors (IEEE Std 1394b-2002 Signaling Must Not Be Put Across IEEE Std 1394a-2000 Connectors or Cables)

- 3.3-V and 5-V PCI Signaling Environments

- Serial-Bus Data Rates of 100 Mbps, 200 Mbps, 400 Mbps, and 800 Mbps

- Physical Write Posting of up to Three

Outstanding Transactions

- Serial ROM or Boot ROM Interface Supports 2-Wire Serial EEPROM Devices

- 33-MHz/32-Bit PCI Interface

- Multifunction Terminal (MFUNC Terminal 1):

- PCI\_CLKRUN Protocol Per PCI Mobile Design Guide

- General-Purpose I/O (GPIO)

- CYCLEIN/CYCLEOUT for External Cycle Timer Control for Customized Synchronization

- PCI Burst Transfers and Deep FIFOs to Tolerate Large Host Latency

- Transmit FIFO—5K Asynchronous

- Transmit FIFO—2K Isochronous

- Receive FIFO—2K Asynchronous

- Receive FIFO—2K Isochronous

- D0, D1, D2, and D3 Power States and PME Events Per PCI Bus Power Management Interface Specification

- Programmable Asynchronous Transmit Threshold

- Isochronous Receive Dual-Buffer Mode

- Out-of-Order Pipelining for Asynchronous Transmit Requests

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

OHCI-Lynx is a trademark of Texas Instruments.

Firewire is a trademark of Apple Computer, Inc.

i.LINK is a trademark of Sony Kabushiki Kaisha TA Sony Corporation. All other trademarks are the property of their respective owners.

#### Initial-Bandwidth-Available and Initial-Channels-Available Registers

#### Digital Video and Audio Performance Enhancements

#### 1.2 Description

The TSB83AA23 is an integrated IEEE Std 1394b-2002 link-layer controller (LLC) design and physical layer (PHY) design combined in a single package to meet the demanding requirements of today's 1394 bus applications. The TSB83AA23 device is capable of exceptional 800-Mbps performance; thus, providing the throughput and bandwidth to move data efficiently and quickly between the PCI and 1394 buses. The TSB83AA23 device also provides outstanding ultralow power operation and intelligent power-management capabilities. The device provides the IEEE 1394 LLC function and PHY function and is compatible with 100-Mbps, 200-Mbps, 400-Mbps, and 800-Mbps serial-bus data rates.

The TSB83AA23 operates as the interface between 33-MHz/32-bit PCI local bus and an IEEE Std 1394a-2000 or IEEE Std 1394b-2002 serial-bus interface. It is capable of supporting serial data rates at 98.304, 196.608, 393.216, 491.52, or 786.432 Mbps (referred to as S100, S200, S400, S400B, or S800 speeds, respectively). When acting as a PCI bus master, the TSB83AA23 device is capable of multiple cache-line bursts of data, which can transfer at 132M bytes/s for 32-bit transfers after connecting to the memory controller.

Due to the high throughput potential of the TSB83AA23 device, it possible to encounter large PCI and legacy 1394 bus latencies, which can cause the 1394 data to be overrun. To overcome this potential problem, the TSB83AA23 implements deep transmit and receive FIFOs (see Section 1.1, *Features*, for FIFO size information) to buffer the 1394 data, thus, preventing possible problems due to bus latency. This also ensures that the device can transmit and receive sustained maximum-size isochronous or asynchronous data payloads at S800.

The TSB83AA23 LLC section implements other performance enhancements to improve overall performance of the device, such as a highly-tuned physical data path for enhanced SBP-2 performance, physical post writing buffers, multiple isochronous contexts, and advanced internal arbitration.

The TSB83AA23 LLC section also implements hardware enhancements to better support digital video (DV) and MPEG data stream reception and transmission. These enhancements are enabled through the isochronous receive digital video enhancements register at TI extension offset A80h (see Section 6.3.4, *Isochronous Receive Digital Video Enhancements Register*). These enhancements include automatic time-stamp insertion for transmitted DV and MPEG-formatted streams, and common isochronous packet (CIP) header stripping for received DV streams.

The CIP format is defined by the IEC 61883-1:1998 specification. The enhancements to the isochronous data contexts are implemented as hardware support for the synchronization time stamp for both DV and audio/video CIP formats. The TSB83AA23 device supports modification of the synchronization time-stamp field to ensure that the value inserted via software is not stale — that is, less than the current cycle timer when the packet is transmitted.

The TSB83AA23 performance and enhanced throughput make it an excellent choice for today's 1394 PC market; however, portable, mobile, and even desktop PC power-management schemes continue to require devices to use less and less power, and TI's 1394 product line has continued to raise the bar by providing the lowest-power 1394 devices in the industry. The TSB83AA23 device represents the next evolution of TI commitment to meet the challenge of power-sensitive applications. The TSB83AA23 device has ultralow operational power requirements and intelligent power-management capabilities that allow it to conserve power autonomously based on the device usage. The TSB83AA23 LLC section fully supports D0, D1, D2, and D3<sub>hot/cold</sub> power states, as specified in the *PC 2001 Design Guide* requirements and the *PCI Power Management Specification*. PME wake-event support is subject to operating-system support and implementation.

As required by the 1394 Open Host Controller Interface Specification (OHCI) and IEEE Std 1394a-2000, internal control registers are memory mapped and nonprefetchable. The PCI configuration header is accessed through configuration cycles as specified by the PCI Local Bus Specification, and provides plug-and-play (PnP) compatibility. Furthermore, the TSB83AA23 LLC section is fully compliant with the latest PCI Local Bus Specification, PCI Bus Power Management Interface Specification, IEEE Std 1394b-2002, IEEE Std 1394a-2000, and 1394 Open Host Controller Interface Specification.

The TSB83AA23 PHY section provides the digital and analog transceiver functions needed to implement a three-port node in a cable-based IEEE 1394 network. Each cable port incorporates two differential line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and for packet reception and transmission.

The TSB83AA23 is powered by multiple voltage supplies, 3.3-V supplies for I/O and the LLC section, and a core voltage supply for the PHY section. The core voltage supply is supplied to the PLLVDD\_CORE and DVDD\_CORE terminals in accordance with the requirements in the recommended operating conditions. The PLLVDD\_CORE terminals must be separated from the DVDD\_CORE terminals, the PLLVDD\_CORE terminals are decoupled with 1- $\mu$ F and smaller decoupling capacitors, and the DVDD\_CORE terminals separately decoupled with 1- $\mu$ F and smaller decoupling capacitors. The separation between DVDD\_CORE and PLLVDD\_CORE can be implemented by separate power-supply rails, or by a single power-supply rail, where the DVDD\_CORE and PLLVDD\_CORE are separated by a filter network to keep noise from the PLLVDD\_CORE supply. In addition, REG\_EN must be asserted low to enable the internal voltage regulator for the LLC section. If REG\_EN is not pulled low, the a 1.8-V power rail must be applied to the REG18 pins.

The TSB83AA23 requires an external 98.304-MHz crystal oscillator to generate a reference clock. The external clock drives an internal phase-locked loop (PLL), which generates the required reference signal. This reference signal provides the clock signals that control transmission of the outbound encoded information. The power-down (PD) function, when enabled by asserting the PD terminal high, stops operation of the PLL.

Data bits to be transmitted through the cable ports are latched internally, combined serially, encoded, and transmitted at 98.304, 196.608, 393.216, 491.52, or 983.04 Mbps (referred to as S100, S200, S400, S400B, or S800 speed, respectively) as the outbound information stream.

To ensure that the TSB83AA23 conforms to the IEEE Std 1394b-2002 standard, the BMODE terminal must be asserted.

#### NOTE

The BMODE terminal does not select the cable-interface mode of operation. The BMODE terminal selects the internal PHY section-LLC section interface mode of operation and affects the arbitration modes on the cable. BMODE must be pulled high during normal operation.

The cable interface can follow either the IEEE Std 1394a-2000 protocol or the IEEE Std 1394b-2002 protocol on all ports. The mode of operation is determined by the interface capabilities of the ports being connected. When any of the ports are connected to an IEEE Std 1394a-2000-compliant device, the cable interface on that port operates in the IEEE Std 1394a-2000 data-strobe mode at a compatible S100, S200, or S400 speed. When a bilingual port is connected to an IEEE Std 1394b-2002-compliant node, the cable interface on that port operates per the IEEE Std 1394b-2002 standard at S400B or S800 speed. The TSB83AA23 automatically determines the correct cable interface connection method for the bilingual ports.

To operate a port as an IEEE Std 1394b-2002 bilingual port, the data-strobe-only terminal for the port (DS0 or DS1) must be pulled to ground through a 1-k $\Omega$  resistor. The port must be operated in the IEEE Std 1394b-2002 bilingual mode when an IEEE Std 1394b-2002 bilingual or an IEEE Std 1394b-2002 Beta-only connector is connected to the port. To operate the port as an IEEE Std 1394a-2000-only port, the data-strobe-only terminal (DS0 or DS1) must be pulled to 3.3-V V<sub>CC</sub> through a 1-k $\Omega$  resistor. The only time the port must be forced to the data-strobe-only mode is if the port is connected to an IEEE Std 1394a-2000 connector (either 6 pin, which is recommended, or 4 pin). This mode is provided to ensure that IEEE Std 1394b-2002 signaling is never sent across an IEEE Std 1394a-2000 cable.

During packet reception, the serial data bits are split into 2-, 4-, or 8-bit parallel streams by the PHY section and sent to the link-layer controller (LLC) section. The received data is also transmitted (repeated) on the other connected and active cable ports.

Both the twisted pair A (TPA) and the twisted pair B (TPB) cable interfaces incorporate differential comparators to monitor the line states during initialization and arbitration when connected to an IEEE Std 1394a-2000-compliant device. The outputs of these comparators are used by the internal logic to determine the arbitration status. The TPA channel monitors the incoming cable common-mode voltage. The value of this common-mode voltage is used during IEEE Std 1394a-2000-mode arbitration and sets the speed of the next packet transmission. In addition, the TPB channel monitors the incoming cable common-mode voltage on the TPB pair for the presence of the remotely supplied twisted pair bias (TPBIAS) voltage.

When connected to an IEEE Std 1394a-2000-compliant node, the TSB83AA23 PHY section provides a 1.86-V nominal bias voltage at the TPBIAS terminal for port termination. The PHY section contains three independent TPBIAS circuits (one for each port). This bias voltage, when seen through a cable by a remote receiver, indicates the presence of an active connection. This bias voltage source must be stabilized by an external filter capacitor of 1  $\mu$ F.

The line drivers in the TSB83AA23 PHY section are designed to work with external 112- $\Omega$  termination resistor networks to match the 110- $\Omega$  cable impedance. One termination network is required at each end of a twisted-pair cable. Each network is composed of a pair of series-connected 56- $\Omega$  resistors. The midpoint of the pair of resistors that is connected to the TPA terminals is connected to its corresponding TPBIAS voltage terminal. The midpoint of the pair of resistors that is directly connected to the TPB terminals is coupled to ground through a parallel RC network, with recommended values of 5 k $\Omega$  and 270 pF. The values of the external line-termination resistors are selected to meet the standard specifications when connected in parallel with the internal receiver circuits. A precision external resistor connected between the R0 and R1 terminals sets the driver output current, along with other internal operating currents.

When the power supply of the TSB83AA23 is off while the twisted-pair cables are connected, the TSB83AA23 transmitter and receiver circuitry present to the cable a high-impedance signal that does not load the device at the other end of the cable.

When the TSB83AA23 PHY section is used without one or more of the ports brought out to a connector, the twisted-pair terminals of the unused ports must be terminated for reliable operation. For each unused port, the port must be forced to the IEEE Std 1394a-2000-only mode (data-strobe-only mode), after which the TPB+ and TPB- terminals can be tied together and then pulled to ground; or the TPB+ and TPB- terminals can be connected to the suggested normal termination network. The TPA+ and TPA- terminals of an unused port can be left unconnected. The TPBIAS terminal can be connected through a  $1-\mu$ F capacitor to ground or left unconnected.

The TESTM, TESTW, SE, and SM terminals are used to set up various manufacturing test conditions. For normal operation, the TESTM and TESTW terminals must be connected to  $V_{DD}$  through a 1-k $\Omega$  resistor. The SE and SM terminals must be tied to ground through a 1-k $\Omega$  resistor.

Three package terminals are used as inputs to set the default value for three configuration status bits in the self-ID packet. They can be pulled high through a  $1-k\Omega$  resistor or hardwired low as a function of the equipment design. The PC0, PC1, and PC2 terminals indicate the default power class status for the node (the need for power from the cable or the ability to supply power to the cable). The contender bit in the PHY register set indicates that the node is a contender either for the isochronous resource manager (IRM) or for the bus manager (BM). On the TSB83AA23, this bit can be set only by a write to the PHY register set. If a node is to be a contender for IRM or BM, the node software must set this bit in the PHY register set.

The LPS (link power status) terminal of the PHY section works with the LKON terminal to manage the power usage in the node. The PHY\_LPS signal from the LLC section is used with the LCtrl bit (see Section 1.3.5) to indicate the active/power status of the LLC section. The LPS signal also resets, disables, and initializes the PHY section-LLC section interface (the state of the PHY section-LLC section interface is controlled solely by the LPS input, regardless of the state of the LCtrl bit). The LPS terminal of the PHY section must be connected to the PHY\_LPS terminal of the LLC section during normal operation.

The LPS input is considered inactive if it remains low for more than the LPS\_RESET time (see the LPS terminal definition) and is considered active otherwise. When the PHY section detects that the LPS input is inactive, the PHY section-LLC section interface is placed into a low-power reset state in which the CTL and D outputs are held in the logic 0 state and the LREQ input is ignored; however, the PCLK output remains active. If the LPS input remains low for more than the LPS\_DISABLE time (see the LPS terminal definition), the PHY section-LLC section interface is put into a low-power disabled state in which the PCLK output is also held inactive. The TSB83AA23 continues the necessary PHY repeater functions required for normal network operation, regardless of the state of the PHY section-LLC section interface. When the interface is in the reset or disabled state and the LPS input is again observed active, the PHY section initializes the interface and returns to normal operation. The PHY section-LLC section interface is also held in the disabled state during hardware reset. When the LPS terminal is returned to an active state after being sensed as having entered the LPS\_DISABLE time, the TSB83AA23 issues a bus reset. This broadcasts the node self-ID packet, which contains the updated L bit state (the PHY section and LLC section now being accessible).

The PHY section uses the LKON terminal to notify the LLC section to power up and become active. When activated, the output LKON signal is a square wave. The PHY section activates the LKON output when the LLC section is inactive and a wake-up event occurs. The LLC section is considered inactive when either the LPS input is inactive, as previously described, or the LCtrl bit is cleared to 0. A wake-up event occurs when a link-on PHY packet addressed to this node is received, or conditionally when a PHY interrupt occurs. The PHY section deasserts the LKON output when the LLC section becomes active (both LPS sensed as active and the LCtrl bit set to 1). The PHY section also deasserts the LKON output when a bus reset occurs, unless a PHY interrupt condition exists, which would otherwise cause LKON to be active. If the TSB83AA23 is power cycled and the power class is 0 through 4, the PHY section asserts LKON for approximately 167  $\mu$ s or until both the LPS is active and the LCtrl bit is 1.

SLLU099B-AUGUST 2007-REVISED FEBRUARY 2008

## **1.3 Terminal Assignments**

# 1.3.1 Top View

|    | Α              | В         | С          | D         | Е             | F               | G          | н        | J        | к                  | L         | М                 | Ν       | Р        |

|----|----------------|-----------|------------|-----------|---------------|-----------------|------------|----------|----------|--------------------|-----------|-------------------|---------|----------|

| 14 | PCI_AD17       | PCI_AD18  | PCI_AD21   | PCI_AD22  | PCI_AD23      | PCI_AD24        | PCI_AD27   | PCI_AD28 | PCI_AD30 | PCI_PME            | PCI_CLK   | PC2               | PCI_RST | PCI_INTA |

| 13 | PCI_AD16       | PCI_AD19  | PCI_AD20   | PCI_IDSEL | PCI_C/BE3     | PCI_AD25        | PCI_AD26   | PCI_AD29 | PCI_AD31 | PCI_REQ            | PCI_GNT   | PC1               | SDA     | TPA2+    |

| 12 | PCI_<br>FRAME  | PCI_C/BE2 | PINT       | PHY_PINT  | CNA           | PD              | TESTM      | RESET    | BMODE    | TESTW<br>(VREG_PD) | PC0       | G_RST             | SCL     | TPA2-    |

| 11 | PCI_<br>DEVSEL | PCI_IRDY  | LPS        |           |               |                 |            |          |          |                    |           | MFUNC             | REG_EN  | TPB2+    |

| 10 | PCI_STOP       | PCI_TRDY  | PHY_LPS    |           | DVDD_3.3      | DVDD_<br>CORE   | VCCP       | REG18    | GND      | AVDD_3.3           |           | TPBIAS2           | GND     | TPB2-    |

| 09 | PCI_PERR       | LKON/DS2  | PHY_LINKON |           | VCC           | GND             | GND        | GND      | GND      | AVDD_3.3           |           | TPBIAS1           | GND     | TPA1+    |

| 08 | PCI_SERR       | LREQ      | PHY_LREQ   |           | VCC           | GND             | GND        | GND      | GND      | VCC                |           | TPBIAS0           | GND     | TPA1-    |

| 07 | PCI_C/BE1      | PCLK      | PHY_PCLK   |           | VCC           | GND             | GND        | GND      | GND      | VCC                |           | PHY_CTL0<br>-CTL0 | GND     | TPB1+    |

| 06 | PCI_PAR        | LCLK      | PHY_LCLK   |           | DVDD_3.3      | GND             | GND        | GND      | VCC      | AVDD_3.3           |           | PHY_CTL1<br>-CTL1 | GND     | TPB1-    |

| 05 | PCI_AD15       | PCI_AD14  | PCI_C/BE0  |           |               | DVDD_<br>CORE   | REG18      | VCCP     | VCC      | AVDD_3.3           |           | PHY_D0-D0         | GND     | TPA0+    |

| 04 | PCI_AD12       | PCI_AD13  | PCI_ACK64  |           |               |                 |            |          |          |                    |           | PHY_D1-D1         | GND     | TPA0-    |

| 03 | PCI_AD11       | PCI_AD6   | PCI_AD5    | PCI_AD4   | PCI_<br>REQ64 | PLLVDD_<br>CORE | PLLVDD_3.3 | CPS      | GND      | GND                | PHY_D7-D7 | PHY_D2-D2         | GND     | TPB0+    |

| 02 | PCI_AD10       | PCI_AD7   | PCI_AD2    | PCI_AD3   | AVDD_3.3      | PLLGND          | DS1        | DS0      | SE       | GND                | PHY_D6-D6 | PHY_D3-D3         | GND     | TPB0-    |

| 01 | PCI_AD9        | PCI_AD8   | PCI_AD1    | PCI_AD0   | R1            | R0              | RSVD (XO)  | XI       | SM       | GND                | PHY_D5-D5 | PHY_D4-D4         | GND     | GND      |

SLLU099B-AUGUST 2007-REVISED FEBRUARY 2008

#### 1.3.2 Bottom View

| Ρ | GND       | TPB0-     | TPB0+           | TPA0-     | TPA0+         | TPB1-             | TPB1+             | TPA1-    | TPA1+      | TPB2-         | TPB2+          | TPA2-              | TPA2+     | PCI_INTA |

|---|-----------|-----------|-----------------|-----------|---------------|-------------------|-------------------|----------|------------|---------------|----------------|--------------------|-----------|----------|

| N | GND       | GND       | GND             | GND       | GND           | GND               | GND               | GND      | GND        | GND           | REG_EN         | SCL                | SDA       | PCI_RST  |

| М | PHY_D4-D4 | PHY_D3-D3 | PHY_D2-D2       | PHY_D1-D1 | PHY_D0-D0     | PHY_CTL1<br>-CTL1 | PHY_CTL0<br>-CTL0 | TPBIAS0  | TPBIAS1    | TPBIAS2       | MFUNC          | G_RST              | PC1       | PC2      |

| L | PHY_D5-D5 | PHY_D6-D6 | PHY_D7-D7       |           |               |                   |                   |          |            |               |                | PC0                | PCI_GNT   | PCI_CLK  |

| к | GND       | GND       | GND             |           | AVDD_3.3      | AVDD_3.3          | VCC               | VCC      | AVDD_3.3   | AVDD_3.3      |                | TESTW<br>(VREG_PD) | PCI_REQ   | PCI_PME  |

| J | SM        | SE        | GND             |           | VCC           | VCC               | GND               | GND      | GND        | GND           |                | BMODE              | PCI_AD31  | PCI_AD30 |

| н | хі        | DS0       | CPS             |           | VCCP          | GND               | GND               | GND      | GND        | REG18         |                | RESET              | PCI_AD29  | PCI_AD28 |

| G | RSVD (XO) | DS1       | PLLVDD_3.3      |           | REG18         | GND               | GND               | GND      | GND        | VCCP          |                | TESTM              | PCI_AD26  | PCI_AD27 |

| F | R0        | PLLGND    | PLLVDD_<br>CORE |           | DVDD_<br>CORE | GND               | GND               | GND      | GND        | DVDD_<br>CORE |                | PD                 | PCI_AD25  | PCI_AD24 |

| Е | R1        | AVDD_3.3  | PCI_<br>REQ64   |           |               | DVDD_3.3          | VCC               | VCC      | VCC        | DVDD_3.3      |                | CNA                | PCI_C/BE3 | PCI_AD23 |

| D | PCI_AD0   | PCI_AD3   | PCI_AD4         |           |               |                   |                   |          |            |               |                | PHY_PINT           | PCI_IDSEL | PCI_AD22 |

| с | PCI_AD1   | PCI_AD2   | PCI_AD5         | PCI_ACK64 | PCI_C/BE0     | PHY_LCLK          | PHY_PCLK          | PHY_LREQ | PHY_LINKON | PHY_LPS       | LPS            | PINT               | PCI_AD20  | PCI_AD21 |

| в | PCI_AD8   | PCI_AD7   | PCI_AD6         | PCI_AD13  | PCI_AD14      | LCLK              | PCLK              | LREQ     | LKON/DS2   | PCI_TRDY      | PCI_IRDY       | PCI_C/BE2          | PCI_AD19  | PCI_AD18 |

| A | PCI_AD9   | PCI_AD10  | PCI_AD11        | PCI_AD12  | PCI_AD15      | PCI_PAR           | PCI_C/BE1         | PCI_SERR | PCI_PERR   | PCI_STOP      | PCI_<br>DEVSEL | PCI_<br>FRAME      | PCI_AD16  | PCI_AD17 |

|   | 01        | 02        | 03              | 04        | 05            | 06                | 07                | 08       | 09         | 10            | 11             | 12                 | 13        | 14       |

SLLU099B-AUGUST 2007-REVISED FEBRUARY 2008

## 1.3.3 Signals Sorted by Terminal Number

| Terminal<br>Number | Signal Name | Terminal<br>Number | Signal Name | Terminal<br>Number | Signal Name        | Terminal<br>Number | Signal Name   |  |

|--------------------|-------------|--------------------|-------------|--------------------|--------------------|--------------------|---------------|--|

| A01                | PCI_AD9     | D01                | PCI_AD0     | H02                | DS0                | M02                | PHY_D3-D3     |  |

| A02                | PCI_AD10    | D02                | PCI_AD3     | H03                | H03 CPS M03        |                    | PHY_D2-D2     |  |

| A03                | PCI_AD11    | D03                | PCI_AD4     | H05                | VCCP               | M04                | PHY_D1-D1     |  |

| A04                | PCI_AD12    | D12                | PHY_PINT    | H06                | GND                | M05                | PHY_D0-D0     |  |

| A05                | PCI_AD15    | D13                | PCI_IDSEL   | H07                | GND                | M06                | PHY_CTL1-CTL1 |  |

| A06                | PCI_PAR     | D14                | PCI_AD22    | H08                | GND                | M07                | PHY_CTL0-CTL0 |  |

| A07                | PCI_C/BE1   | E01                | R1          | H09                | GND                | M08                | TPBIAS0       |  |

| A08                | PCI_SERR    | E02                | AVDD_3.3    | H10                | REG18              | M09                | TPBIAS1       |  |

| A09                | PCI_PERR    | E03                | PCI_REQ64   | H12                | RESET              | M10                | TPBIAS2       |  |

| A10                | PCI_STOP    | E06                | DVDD_3.3    | H13                | PCI_AD29           | M11                | MFUNC         |  |

| A11                | PCI_DEVSEL  | E07                | VCC         | H14                | PCI_AD28           | M12                | G_RST         |  |

| A12                | PCI_FRAME   | E08                | VCC         | J01                | SM                 | M13                | PC1           |  |

| A13                | PCI_AD16    | E09                | VCC         | J02                | SE                 | M14                | PC2           |  |

| A14                | PCI_AD17    | E10                | DVDD_3.3    | J03                | GND                | N01                | GND           |  |

| B01                | PCI_AD8     | E12                | CNA         | J05                | VCC                | N02                | GND           |  |

| B02                | PCI_AD7     | E13                | PCI_C/BE3   | J06                | VCC                | N03                | GND           |  |

| B03                | PCI_AD6     | E14                | PCI_AD23    | J07                | GND                | N04                | GND           |  |

| B04                | PCI_AD13    | F01                | R0          | J08                | GND                | N05                | GND           |  |

| B05                | PCI_AD14    | F02                | PLLGND      | J09                | GND                | N06                | GND           |  |

| B06                | LCLK        | F03                | PLLVDD_CORE | J10                | GND                | N07                | GND           |  |

| B07                | PCLK        | F05                | DVDD_CORE   | J12                | BMODE              | N08                | GND           |  |

| B08                | LREQ        | F06                | GND         | J13                | PCI_AD31           | N09                | GND           |  |

| B09                | LKON/DS2    | F07                | GND         | J14                | PCI_AD30           | N10                | GND           |  |

| B10                | PCI_TRDY    | F08                | GND         | K01                | GND                | N11                | REG_EN        |  |

| B11                | PCI_IRDY    | F09                | GND         | K02                | GND                | N12                | SCL           |  |

| B12                | PCI_C/BE2   | F10                | DVDD_CORE   | K03                | GND                | N13                | SDA           |  |

| B13                | PCI_AD19    | F12                | PD          | K05                | AVDD_3.3           | N14                | PCI_RST       |  |

| B14                | PCI_AD18    | F13                | PCI_AD25    | K06                | AVDD_3.3           | P01                | GND           |  |

| C01                | PCI_AD1     | F14                | PCI_AD24    | K07                | VCC                | P02                | TPB0-         |  |

| C02                | PCI_AD2     | G01                | RSVD (X0)   | K08                | VCC                | P03                | TPB0+         |  |

| C03                | PCI_AD5     | G02                | DS1         | K09                | AVDD_3.3           | P04                | TPA0-         |  |

| C04                | PCI_ACK64   | G03                | PLLVDD_3.3  | K10                | AVDD_3.3           | P05                | TPA0+         |  |

| C05                | PCI_C/BE0   | G05                | REG18       | K12                | TESTW<br>(VREG_PD) | P06                | TPB1-         |  |

| C06                | PHY_LCLK    | G06                | GND         | K13                | PCI_REQ            | P07                | TPB1+         |  |

| C07                | PHY_PCLK    | G07                | GND         | K14                | PCI_PME            | P08                | TPA1–         |  |

| C08                | PHY_LREQ    | G08                | GND         | L01                | PHY_D5-D5          | P09                | TPA1+         |  |

| C09                | PHY_LINKON  | G09                | GND         | L02                | PHY_D6-D6          | P10                | TPB2–         |  |

| C10                | PHY_LPS     | G10                | VCCP        | L03                | PHY_D7-D7          | P11                | TPB2+         |  |

| C11                | LPS         | G12                | TESTM       | L12                | PC0                | P12                | TPA2–         |  |

| C12                | PINT        | G13                | PCI_AD26    | L13                | PCI_GNT            | P13                |               |  |

| C13                | PCI_AD20    | G14                | PCI_AD27    | L14                | PCI_CLK            | P14                |               |  |

| C14                | PCI_AD21    | H01                | XI          | M01                | PHY_D4-D4          |                    |               |  |

SLLU099B-AUGUST 2007-REVISED FEBRUARY 2008

## 1.3.4 Signals Sorted by Name

| Signal Name | Terminal<br>Number | Signal Name | Terminal<br>Number | Signal Name   | Terminal<br>Number | Signal Name        | Terminal<br>Number |

|-------------|--------------------|-------------|--------------------|---------------|--------------------|--------------------|--------------------|

| AVDD_3.3    | E02, K05,          | N.C.        | H11, J04,          | PCI_AD29      | H13                | PHY_PINT           | D12                |

|             | K06, K09,          |             | J11, K04,          | PCI_AD30      | J14                | PINT               | C12                |

|             | K10                |             | K11, L04,          | PCI_AD31      | J13                | PLLGND             | F02                |

| BMODE       | J12                |             | L05, L06,          | PCI_C/BE0     | C05                | PLLVDD_3.3         | G03                |

| CNA         | E12                |             | L07, L08           | PCI_C/BE1     | A07                | PLLVDD_CORE        | F03                |

| CPS         | H03                |             | L09, L10,          | PCI_C/BE2     | B12                | R0                 | F01                |

| DS0         | H02                |             | L11                | PCI_C/BE3     | E13                | R1                 | E01                |

| DS1         | G02                | PC0         | L12                | PCI_CLK       | L14                | REG18              | G05, H10           |

| DVDD_3.3    | E06, E10           | PC1         | M13                | PCI_DEVSEL    | A11                | REG_EN             | N11                |

| DVDD_CORE   | F05, F10           | PC2         | M14                | PCI_FRAME     | A12                | RESET              | H12                |

| G_RST       | M12                | PCI_ACK64   | C04                | PCI_GNT       | L13                | SCL                | N12                |

| GND         | F06, F07,          | PCI_AD0     | D01                | PCI_IDSEL     | D13                | SDA                | N13                |

|             | F08, F09,          | PCI_AD1     | C01                | PCI_INTA      | P14                | SE                 | J02                |

|             | G06, G07,          | PCI_AD2     | C02                | PCI_IRDY      | B11                | SM                 | J01                |

|             | G08, G09,          | PCI_AD3     | D02                | PCI_PAR       | A06                | TESTM              | G12                |

|             | H06, H07,          | PCI_AD4     | D03                | PCI_PERR      | A09                | TESTW<br>(VREG_PD) | K12                |

|             | H08, H09,          | PCI_AD5     | C03                | PCI_PME       | K14                | TPA0-              | P04                |

|             | J03, J07,          | PCI_AD6     | B03                | PCI_REQ       | K13                | TPA0+              | P05                |

|             | J08, J09,          | PCI_AD7     | B02                | PCI_REQ64     | E03                | TPA1–              | P08                |

|             | J10, K01,          | PCI_AD8     | B01                | PCI_RST       | N14                | TPA1+              | P09                |

|             | K02, K03,          | PCI_AD9     | A01                | PCI_SERR      | A08                | TPA2–              | P12                |

|             | N01, N02,          | PCI_AD10    | A02                | PCI_STOP      | A10                | TPA2+              | P13                |

|             | N03, N04,          | PCI_AD11    | A03                | PCI_TRDY      | B10                | TPB0-              | P02                |

|             | N05, N06,          | PCI_AD12    | A04                | PCLK          | B07                | TPB0+              | P03                |

|             | N07, N08,          | PCI_AD13    | B04                | PD            | F12                | TPB1-              | P06                |

|             | N09, N10,          | PCI_AD14    | B05                | PHY_CTL0-CTL0 | M07                | TPB1+              | P07                |

|             | P01                | PCI_AD15    | A05                | PHY_CTL1-CTL1 | M06                | TPB2-              | P10                |

| LCKL        | B06                | PCI_AD16    | A13                | PHY_D0-D0     | M05                | TPB2+              | P11                |

| LKON/DS2    | B09                | PCI_AD17    | A14                | PHY_D1-D1     | M04                | TPBIAS0            | M08                |

| LPS         | C11                | PCI_AD18    | B14                | PHY_D2-D2     | M03                | TPBIAS1            | M09                |

| LREQ        | B08                | PC1_AD19    | B13                | PHY_D3-D3     | M02                | TPBIAS2            | M10                |

| MFUNC       | M11                | PCI_AD20    | C13                | <br>PHY_D4-D4 | M01                | VCC                | E07, E08,          |

| N.C.        | D04, D05,          | PCI_AD21    | C14                | <br>PHY_D5-D5 | L01                | †1                 | E09, J05,          |

|             | D06, D07,          | PCI_AD22    | D14                | PHY_D6-D6     | L02                | †1                 | J06, K07,          |

|             | D08, D09,          | PCI_AD23    | E14                | PHY_D7-D7     | L03                | †1                 | K08                |

|             | D10, D11,          | PCI_AD24    | F14                | PHY_LCLK      | C06                | VCCP               | G10, H05           |

|             | E04, E05,          | PCI_AD25    | F13                | PHY_LINKON    | C09                | XI                 | H01                |

|             | E11, F04,          | PCI_AD26    | G13                | PHY_LPS       | C10                | RSVD (XO)          | G01                |

|             | F11, G04,          | PCI_AD27    | G14                | PHY LREQ      | C08                |                    |                    |

|             | G11, H04,          | PCI_AD28    | H14                | PHY_PCLK      | C07                |                    |                    |

SLLU099B-AUGUST 2007-REVISED FEBRUARY 2008

### **1.3.5 Terminal Functions**

| TERMINAL    |                                                                                                                                                                                         | 1/0 | DECODIDENCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.                                                                                                                                                                                     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                                                                                                                                                                                         |     | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AVDD_3.3    | E02, K05, K06,<br>K09, K10                                                                                                                                                              |     | Analog circuit power. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled $0.1-\mu$ F and $0.001-\mu$ F. Lower-frequency $10-\mu$ F filtering capacitors also are recommended. These supply terminals are separated from the other power terminals internal to the device to provide noise isolation. The PLLVDD_3.3, AVDD_3.3, and DVDD_3.3 terminals must be tied together with a low-dc-impedance connection on the circuit board.                                                                                                    |

| DVDD_CORE   | F05, F10                                                                                                                                                                                |     | Digital 1.95-V circuit power. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled $0.1-\mu F$ and $0.001-\mu F$ . An additional $1-\mu F$ capacitor is required for voltage regulation. These supply terminals are separated from the other power terminals internal to the device to provide noise isolation.                                                                                                                                                                                                                           |

| DVDD_3.3    | E06, E10                                                                                                                                                                                |     | Digital 3.3-V circuit power. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled $0.1 \mu$ F and $0.001 \mu$ F. Lower-frequency $10 \mu$ F filtering capacitors also are recommended. The DVDD_3.3 terminals must be tied together at a low-impedance point on the circuit board. These supply terminals are separated from the other power terminals internal to the device to provide noise isolation. The PLLVDD_3.3, AVDD_3.3, and DVDD_3.3 terminals must be tied together with a low-dc-impedance connection on the circuit board. |

| GND         | F06, F07, F08,<br>F09, G06, G07,<br>G08, G09, H06,<br>H07, H08, H09,<br>J03, J07, J08,<br>J09, J10, K01,<br>K02, K03, N01,<br>N02, N03, N04,<br>N05, N06, N07,<br>N08, N09, N10,<br>P01 |     | Ground. These terminals must be tied together to the low-impedance circuit-board ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PLLGND      | F02                                                                                                                                                                                     |     | PLL circuit ground. These terminals must be tied together to the low-impedance circuit-board ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PLLVDD_CORE | F03                                                                                                                                                                                     |     | PLL 1.95-V circuit power. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled 0.1- $\mu$ F and 0.001- $\mu$ F. An additional 1- $\mu$ F capacitor is required for voltage regulation, and the PLLVDD_CORE terminals must be separate from the DVDD_CORE terminals. These supply terminals are separated from the other power terminals internal to the device to provide noise isolation.                                                                                                                                                |

| PLLVDD_3.3  | G03                                                                                                                                                                                     |     | PLL 3.3-V circuit power. A combination of high-frequency decoupling capacitors near the terminal is suggested, such as paralleled 0.1- $\mu$ F and 0.001- $\mu$ F. Lower-frequency 10- $\mu$ F filtering capacitors also are recommended. This supply terminal is separated from the other power terminals internal to the device to provide noise isolation. The DVDD_3.3 terminals must be tied together at a low-impedance point on the circuit board. The PLLVDD_3.3, AVDD_3.3, and DVDD_3.3 terminals must be tied together with a low-dc-impedance connection.                           |

| REG18       | G05, H10                                                                                                                                                                                |     | The REG18 terminals are connected to the internal 1.8-V LLC-section core voltage. They provide local bypass for the internal core voltage or to provide 1.8 V to the core externally if the internal regulator is disabled.                                                                                                                                                                                                                                                                                                                                                                    |

| REG_EN      | N11                                                                                                                                                                                     | Ι   | Regulator enable. When this terminal is low, the internal 1.8-V regulator is enabled and generates the 1.8-V internal core voltage from the 3.3-V supply voltage. If it is disabled by pulling the terminal high through a 10-k $\Omega$ or smaller resistor, 1.8 V must be provided to the REG18 terminals for normal operation.                                                                                                                                                                                                                                                              |

| VCC         | E07, E08, E09,<br>J05, J06, K07,<br>K08                                                                                                                                                 |     | 3.3-V power supply. A parallel combination of high-frequency decoupling capacitors near each terminal is suggested, such as 0.1- $\mu$ F and 0.001- $\mu$ F. Lower-frequency 10- $\mu$ F filtering capacitors also are recommended. They must be tied to a low-impedance point on the circuit board.                                                                                                                                                                                                                                                                                           |

| VCCP        | G10, H05                                                                                                                                                                                | Ι   | PCI signaling clamp voltage power. PCI signals are clamped to this power rail per the <i>PCI Local Bus Specification</i> . In addition, if a 5-V ROM is used, the VCCP terminal must be connected to 5 V.                                                                                                                                                                                                                                                                                                                                                                                      |

### TEXAS INSTRUMENTS www.ti.com

# TSB83AA23 IEEE Std 1394b-2002 PHY and OHCI Link Device

| TERMIN                                                                                               | AL                                                   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                                                                 | NO. I/O DESCRIPTION                                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |