Sample &

Buy

SLUSAT7F-NOVEMBER 2011-REVISED DECEMBER 2014

Support &

Community

20

## UCC2721x 120-V Boot, 4-A Peak, High-Frequency High-Side and Low-Side Driver

Technical

Documents

#### 1 Features

- Drives Two N-Channel MOSFETs in High-Side and Low-Side Configuration With Independent Inputs

- Maximum Boot Voltage 120-V DC

- 4-A Sink, 4-A Source Output Currents

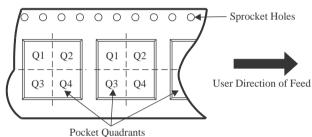

- 0.9-Ω Pullup and Pulldown Resistance

- Input Pins Can Tolerate -10 V to 20 V and Are Independent of Supply Voltage Range

- TTL or Pseudo-CMOS Compatible Input Versions

- 8-V to 17-V VDD Operating Range, (20-V Absolute Maximum)

- 7.2-ns Rise and 5.5-ns Fall Time With 1000-pF Load

- Fast Propagation Delay Times (18 ns Typical)

- 2-ns Delay Matching

- Symmetrical Undervoltage Lockout for High-Side and Low-Side Driver

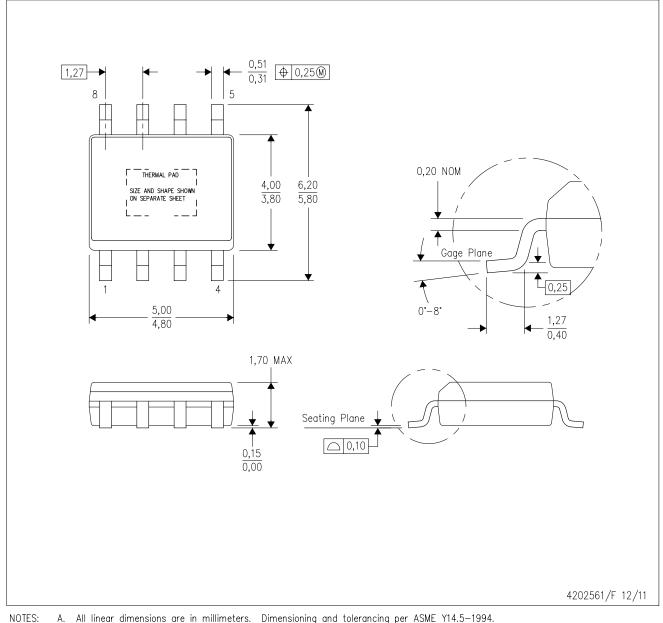

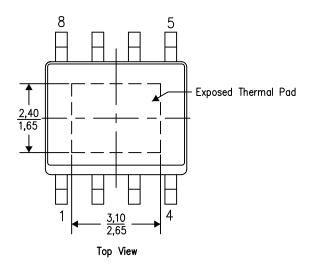

- All Industry Standard Packages Available (SOIC-8, PowerPAD<sup>™</sup> SOIC-8, 4-mm × 4-mm SON-8 and 4-mm × 4-mm SON-10)

- Specified from -40 to 140 °C

#### Applications 2

- Power Supplies for Telecom, Datacom, and Merchant

- Half-Bridge and Full-Bridge Converters

- **Push-Pull Converters**

- High-Voltage Synchronous-Buck Converters

- **Two-Switch Forward Converters**

- Active-Clamp Forward Converters

- **Class-D Audio Amplifiers**

## 3 Description

Tools &

Software

The UCC27210 and UCC27211 drivers are based on the popular UCC27200 and UCC27201 MOSFET drivers, but offer several significant performance improvements. Peak output pull-up and pull-down current has been increased to 4-A source and 4-A sink, and pull-up and pull-down resistance have been reduced to 0.9  $\Omega$ , thereby allowing for driving large power MOSFETs with minimized switching losses during the transition through the Miller Plateau of the MOSFET. The input structure is now able to directly handle -10 VDC, which increases robustness and also allows direct interface to gate-drive transformers without using rectification diodes. The inputs are also independent of supply voltage and have a maximum rating of 20-V.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE      | BODY SIZE (NOM)   |

|-------------|--------------|-------------------|

|             | SOIC (8)     | 4.90 mm × 3.91 mm |

| UCC27210,   | PowerPAD (8) | 4.89 mm × 3.90 mm |

| UCC27211    | WSON (10)    | 4.00 mm + 4.00 mm |

|             | VSON (8)     | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

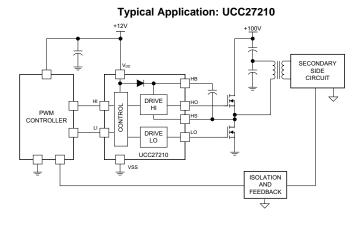

### Typical Application: UCC27211

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## **Table of Contents**

| Feat       | ures 1                                          |    | 8.1  | Overview   |

|------------|-------------------------------------------------|----|------|------------|

| Арр        | lications 1                                     |    | 8.2  | Functiona  |

|            | cription 1                                      |    | 8.3  | Feature D  |

|            | ision History 2                                 |    | 8.4  | Device Fu  |

|            | cription (Continued)                            | 9  | Арр  | lication a |

|            | Configuration and Functions                     |    | 9.1  | Applicatio |

|            | cifications                                     |    | 9.2  | Typical A  |

| 7.1        |                                                 | 10 | Pow  | er Supp    |

|            | Absolute Maximum Ratings                        | 11 | Lay  | out        |

| 7.2<br>7.3 | ESD Ratings                                     |    | 11.1 | Layout C   |

| -          |                                                 |    | 11.2 | Layout E   |

| 7.4        | Thermal Information                             |    | 11.3 | Thermal    |

| 7.5        | Electrical Characteristics                      | 12 | -    | ice and I  |

| 7.6        | Switching Characteristics: Propagation Delays 8 | 12 | 12.1 |            |

| 7.7        | Switching Characteristics: Delay Matching 8     |    |      | Docume     |

| 7.8        | Switching Characteristics: Output Rise and Fall |    | 12.2 | Related    |

|            | Time                                            |    | 12.3 | Tradema    |

| 7.9        | Switching Characteristics: Miscellaneous        |    | 12.4 | Electros   |

| 7.10       | Typical Characteristics 10                      |    | 12.5 | Glossar    |

|            | ailed Description 13                            | 13 | Mec  | hanical,   |

|            |                                                 |    |      |            |

|    | 8.2   | Functional Block Diagram          | 14 |

|----|-------|-----------------------------------|----|

|    | 8.3   | Feature Description               | 14 |

|    | 8.4   | Device Functional Modes           | 15 |

| 9  | Appl  | lication and Implementation       | 16 |

|    | 9.1   | Application Information           | 16 |

|    | 9.2   | Typical Application               | 16 |

| 10 | Pow   | er Supply Recommendations         | 21 |

| 11 | Layo  | out                               | 21 |

|    | -     | Layout Guidelines                 |    |

|    | 11.2  | Layout Example                    | 22 |

|    | 11.3  | Thermal Considerations            | 22 |

| 12 | Devi  | ice and Documentation Support     | 23 |

|    | 12.1  | Documentation Support             | 23 |

|    | 12.2  | Related Links                     | 23 |

|    | 12.3  | Trademarks                        | 23 |

|    | 12.4  | Electrostatic Discharge Caution   | 23 |

|    | 12.5  | Glossary                          | 23 |

| 13 | Mec   | hanical, Packaging, and Orderable |    |

|    | Infor | mation                            | 23 |

|    |       |                                   |    |

## 4 Revision History

1 2

3

4

5

6

7

8

2

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Revision E (August 2013) to Revision F

| • | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional |

|---|------------------------------------------------------------------------------------------------------------------|

|   | Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device      |

|   | and Documentation Support section, and Mechanical, Packaging, and Orderable Information section                  |

| C | hanges from Revision D (November, 2012) to Revision E                                         | Page |

|---|-----------------------------------------------------------------------------------------------|------|

| • | Added Note 2 to the Terminal Functions Table                                                  | 5    |

| • | Changed Repetitive pulse data from -18 V to -(24V-VDD).                                       | 5    |

| • | Added additional details to Note 2                                                            | 5    |

| • | Changed Voltage on HS, V <sub>HS</sub> (repetitive pulse <100 ns) data from -15 to -(24V-VDD) | 6    |

| • | Deleted 2.4-mA operating current min range in both places                                     | 7    |

| • | Changed operating current max range extended to 5.2 in both places.                           | 7    |

| • | Deleted 1.5 min Boot voltage operating current range                                          | 7    |

| • | Changed Boot voltage operating current max range from 4.2 to 5.0.                             | 7    |

| • | Changed HB to V <sub>SS</sub> operating current max range from 1.1 to 1.2.                    | 7    |

| • | Changed LO Gate Driver's Low-level output voltage max range from 0.17 to 0.19                 | 7    |

| • | Changed HO GATE Driver's Low-level output voltage max range from 0.17 to 0.19.                | 7    |

## Changes from Revision C (March, 2012) to Revision D

| • | Changed capacitor range from 1.0 µF to 4.7 µF.             | . 5 |

|---|------------------------------------------------------------|-----|

| • | Added Terminal Functions Note to HI and LI pin description | . 5 |

| • | Changed bullet 2 in the Layout Recommendations.            | 21  |

| • | Added Note: For systems using                              | 21  |

EXAS

Copyright © 2011–2014, Texas Instruments Incorporated

## Page

Page

1

## UCC27210, UCC27211

Page

SLUSAT7F-NOVEMBER 2011-REVISED DECEMBER 2014

### Changes from Revision B (February) to Revision C

| • | Changed V <sub>DD</sub> operating current max range of 4.3 to 4.4 in both places | . 7 |

|---|----------------------------------------------------------------------------------|-----|

| • | Changed Boot voltage operating current max range from 4.0 to 4.2.                | . 7 |

| • | Changed HB to V <sub>SS</sub> quiescent current max range from 0.13 to 1.0.      | . 7 |

| • | Changed HB to V <sub>SS</sub> operating current max range from 0.9 to 1.1.       | . 7 |

| • | Added Input UCC27210/11 (DDA Only) values.                                       | . 7 |

| • | Added Under-Voltage Lockout (UVLO) DDA only values, two places.                  | . 7 |

| • | Changed LO Gate Driver's Low-level output voltage max range from 0.15 to 0.17    | . 7 |

| • | Changed LO Gate Driver's V <sub>LOH</sub> max range from 0.27 to 0.29.           | . 7 |

| • | Changed HO GATE Driver's Low-level output voltage max range from 0.15 to 0.17.   | . 7 |

| • | Changed $V_{LI}$ falling to $V_{LO}$ falling min value from 17 to 15             | . 8 |

| • | Changed $V_{HI}$ falling to $V_{HO}$ falling min value from 17 to 15.            | . 8 |

| • | Changed V <sub>LI</sub> rising to V <sub>LO</sub> rising min value from 18 to 15 | . 8 |

| • | Changed V <sub>HI</sub> rising to V <sub>HO</sub> rising min value from 18 to 15 | . 8 |

| • | Changed Figure 17, Output Current vs. Output Voltage.                            | 12  |

|   |                                                                                  |     |

## **5** Description (Continued)

The switching node (HS pin) of the UCC2721x can handle –18 V maximum which allows the high-side channel to be protected from inherent negative voltages caused parasitic inductance and stray capacitance. The UCC27210 (Pseudo-CMOS inputs) and UCC27211 (TTL inputs) have increased hysteresis allowing for interface to analog or digital PWM controllers with enhanced noise immunity.

The low-side and high-side gate drivers are independently controlled and matched to 2 ns between the turnon and turnoff of each other.

An on-chip 120-V rated bootstrap diode eliminates the external discrete diodes. Undervoltage lockout is provided for both the high-side and the low-side drivers providing symmetric turnon and turnoff behavior and forcing the outputs low if the drive voltage is below the specified threshold.

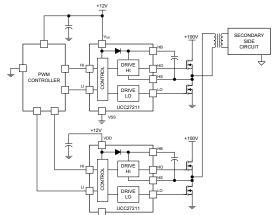

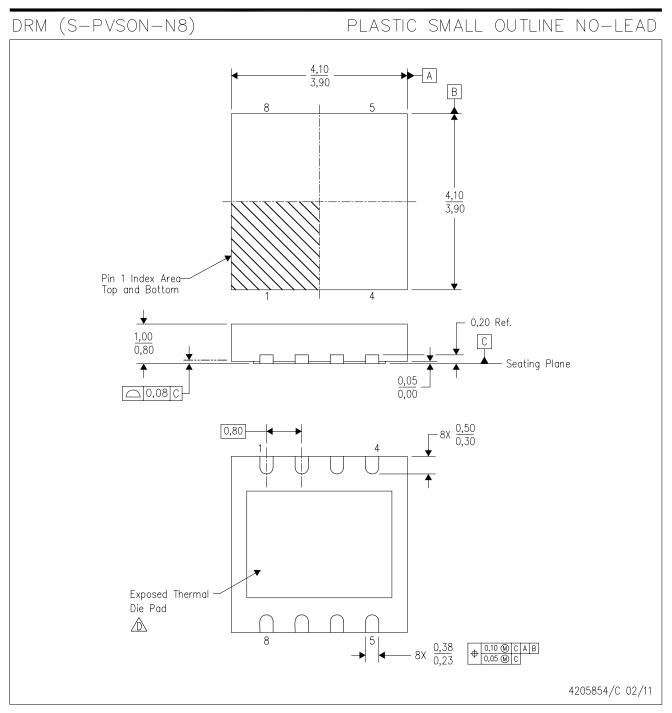

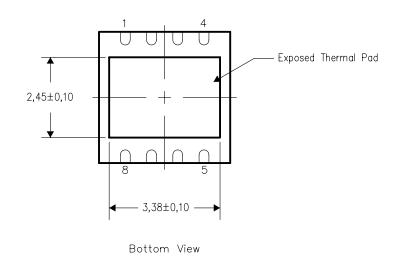

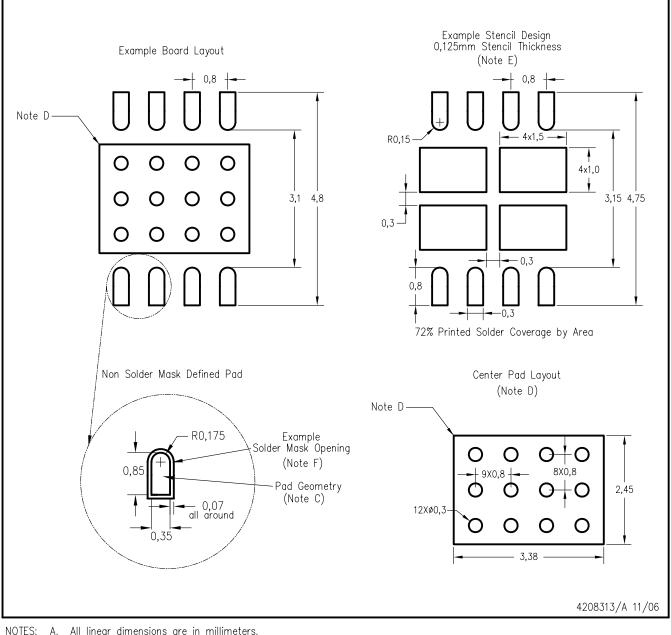

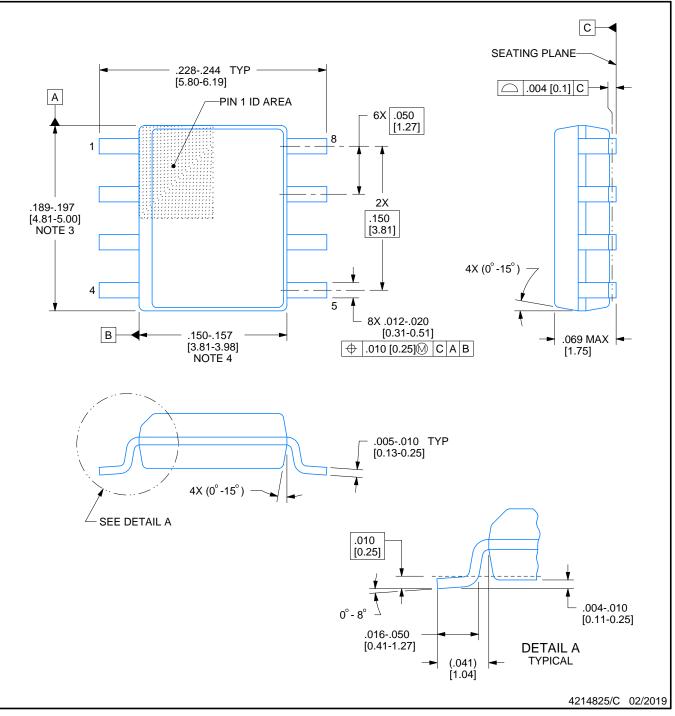

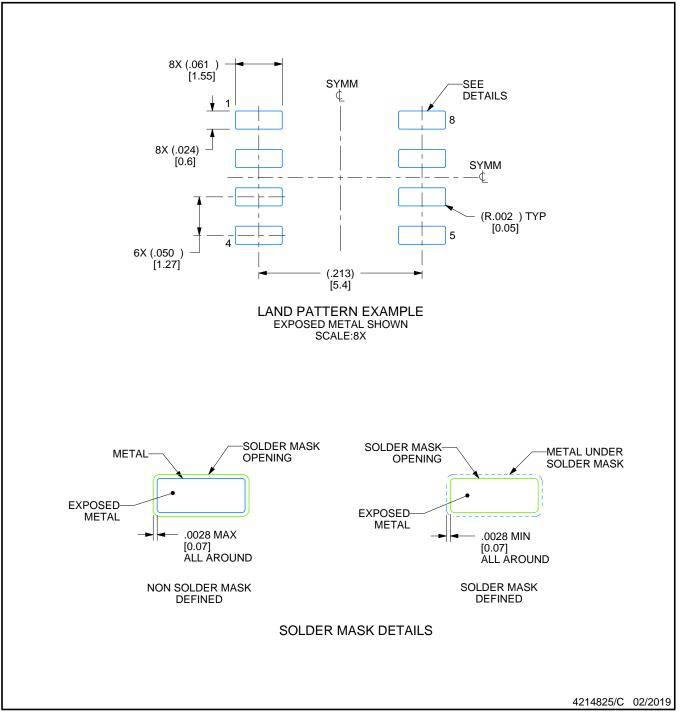

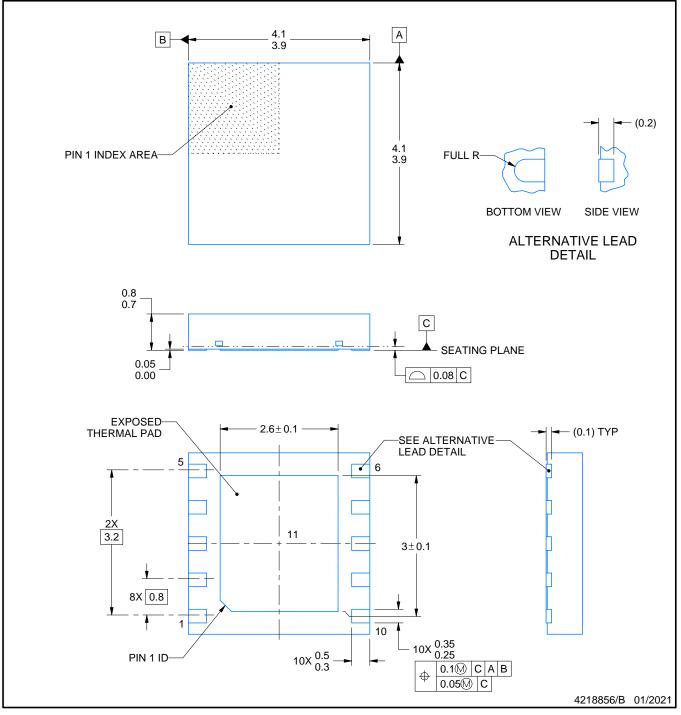

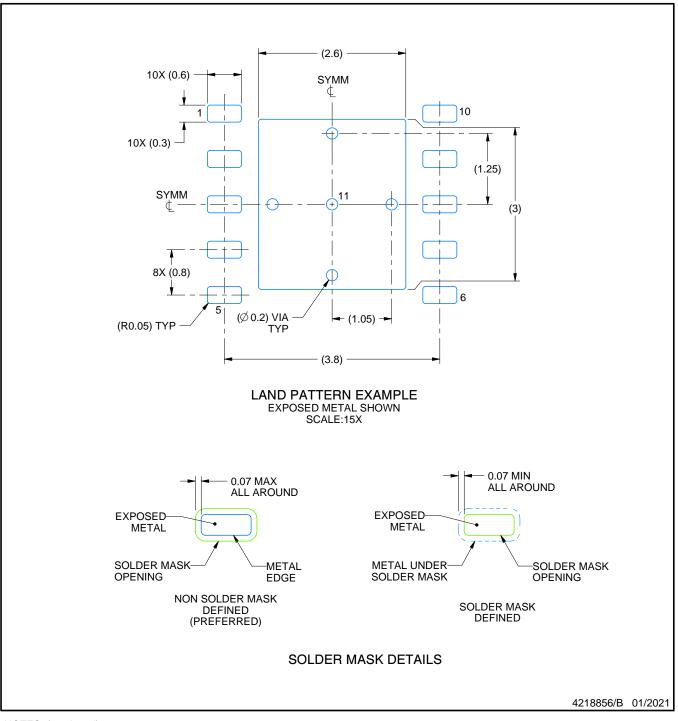

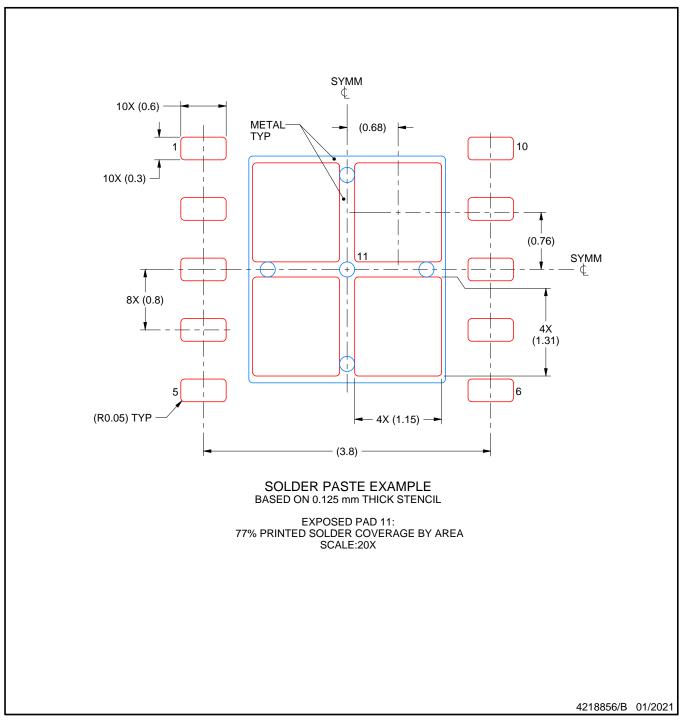

Both devices are offered in 8-pin SOIC (D), PowerPAD SOIC-8 (DDA), 4-mm × 4-mm SON-8 (DRM) and SON-10 (DPR) packages.

## 6 Pin Configuration and Functions

SLUSAT7F - NOVEMBER 2011 - REVISED DECEMBER 2014

#### www.ti.com

## **Pin Functions**

| PIN                |           | I/O | DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|--------------------|-----------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME               | D/DDA/DRM | DPR | 1/0         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| VDD                | 1         | 1   | Р           | Positive supply to the lower-gate driver. Decouple this pin to V <sub>SS</sub> (GND). Typical decoupling capacitor range is 0.22 $\mu$ F to 4.7 $\mu$ F (See <sup>(1)</sup> ).                                                                                                                                                                                                                             |  |  |

| НВ                 | 2         | 2   | Ρ           | High-side bootstrap supply. The bootstrap diode is on-chip but the external bootstrap capacitor is required. Connect positive side of the bootstrap capacitor to this pin. Typical range of HB bypass capacitor is $0.022 \ \mu\text{F}$ to $0.1 \ \mu\text{F}$ . The capacitor value is dependent on the gate charge of the high-side MOSFET and should also be select based on speed and ripple criteria |  |  |

| НО                 | 3         | 3   | 0           | High-side output. Connect to the gate of the high-side power MOSFET.                                                                                                                                                                                                                                                                                                                                       |  |  |

| HS                 | 4         | 4   | Ρ           | High-side source connection. Connect to source of high-side power MOSFET.<br>Connect the negative side of bootstrap capacitor to this pin.                                                                                                                                                                                                                                                                 |  |  |

| н                  | 5         | 7   | Ι           | High-side input. <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| LI                 | 6         | 8   | Ι           | Low-side input. <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| VSS                | 7         | 9   | G           | Negative supply terminal for the device which is generally grounded.                                                                                                                                                                                                                                                                                                                                       |  |  |

| LO                 | 8         | 10  | 0           | Low-side output. Connect to the gate of the low-side power MOSFET.                                                                                                                                                                                                                                                                                                                                         |  |  |

| N/C                | _         | 5/6 | _           | Not connected.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| PowerPAD<br>TM (3) |           |     | G           | Used on the DDA, DRM and DPR packages only. Electrically referenced to $V_{\rm SS}$ (GND). Connect to a large thermal mass trace or GND plane to dramatically improve thermal performance.                                                                                                                                                                                                                 |  |  |

(1) For cold temperature applications we recommend the upper capacitance range. Attention should also be made to PCB layout - see Layout.

(2) HI or LI input is assumed to connect to a low impedance source signal. The source output impedance is assumed less than 100 Ω. If the source impedance is greater than 100 Ω, add a bypassing capacitor, each, between HI and VSS and between LI and VSS. The added capacitor value depends on the noise levels presented on the pins, typically from 1 nF to 10 nF should be effective to eliminate the possible noise effect. When noise is present on two pins, HI or LI, the effect is to cause HO and LO malfunctions to have wrong logic outputs.

(3) The PowerPAD<sup>™</sup> is not directly connected to any leads of the package. However it is electrically and thermally connected to the substrate which is the ground of the device.

## 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                                                                                                                                                                                                                                      |                                         | MIN                   | MAX                   | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------|-----------------------|------|

| Supply voltage range, $V_{DD}^{(2)}$ , $V_{HB}$ - $V_{H}$                                                                                                                                                                                                            | S                                       | -0.3                  | 20                    |      |

| Input voltages on LI and HI, $V_{LI}$ , $V_{HI}$                                                                                                                                                                                                                     |                                         | -10                   | 20                    |      |

| pput voltages on LI and HI, $V_{LI}$ , $V_{HI}$<br>Dutput voltage on LO, $V_{LO}$<br>Dutput voltage on HO, $V_{HO}$<br>Foltage on HS, $V_{HS}$<br>Foltage on HB, $V_{HB}$<br>Departing virtual junction temperature, $T_{J}$<br>ead temperature (soldering, 10 sec.) | DC                                      | -0.3                  | V <sub>DD</sub> + 0.3 |      |

| Output voltage on LO, VLO                                                                                                                                                                                                                                            | Repetitive pulse <100 ns <sup>(3)</sup> | -2                    | V <sub>DD</sub> + 0.3 |      |

|                                                                                                                                                                                                                                                                      | DC                                      | V <sub>HS</sub> – 0.3 | V <sub>HB</sub> + 0.3 | V    |

| Output voltage on HO, V <sub>HO</sub>                                                                                                                                                                                                                                | Repetitive pulse <100 ns <sup>(3)</sup> | V <sub>HS</sub> – 2   | V <sub>HB</sub> + 0.3 |      |

|                                                                                                                                                                                                                                                                      | DC                                      | -1                    | 115                   |      |

| Voltage on HS, V <sub>HS</sub>                                                                                                                                                                                                                                       | Repetitive pulse <100 ns <sup>(3)</sup> | -(24 V-VDD)           | 115                   |      |

| Voltage on HB, V <sub>HB</sub>                                                                                                                                                                                                                                       |                                         | -0.3                  | 120                   |      |

| Operating virtual junction temperature,                                                                                                                                                                                                                              | TJ                                      | -40                   | 150                   | °C   |

| Lead temperature (soldering, 10 sec.)                                                                                                                                                                                                                                |                                         |                       | 300                   | C    |

| Storage temperature, T <sub>stg</sub>                                                                                                                                                                                                                                |                                         | -65                   | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to VSS unless otherwise noted. Currents are positive into, negative out of the specified terminal.

(3) Verified at bench characterization. VDD is the value used in an application design.

SLUSAT7F-NOVEMBER 2011-REVISED DECEMBER 2014

www.ti.com

STRUMENTS

XAS

## 7.2 ESD Ratings

|                    |                         | VALUE         UNIT           Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> ±2000           Charged-device model (CDM), per JEDEC specification JESD22-         ±1000           V         V |       |   |

|--------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                                                                                                                                              | ±2000 |   |

| V <sub>(ESD)</sub> | Electrostatic discharge |                                                                                                                                                                                                                | ±1000 | V |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

all voltages are with respect to  $V_{SS}$ ; currents are positive into and negative out of the specified terminal.  $-40^{\circ}C < T_J = T_A < 140^{\circ}C$  (unless otherwise noted)

|                                                           | MIN                                       | TYP | MAX                         | UNIT |

|-----------------------------------------------------------|-------------------------------------------|-----|-----------------------------|------|

| Supply voltage range, $V_{DD}$ , $V_{HB}$ - $V_{HS}$      | 8                                         | 12  | 17                          |      |

| Voltage on HS, V <sub>HS</sub>                            | -1                                        |     | 105                         |      |

| Voltage on HS, V <sub>HS</sub> (repetitive pulse <100 ns) | -(24V-VDD)                                |     | 110                         | V    |

| Voltage on HB, V <sub>HB</sub>                            | V <sub>HS</sub> +8,<br>V <sub>DD</sub> –1 |     | V <sub>HS</sub> +17,<br>115 |      |

| Voltage slew rate on HS                                   |                                           |     | 50                          | V/ns |

| Operating junction temperature range                      | -40                                       |     | 140                         | °C   |

## 7.4 Thermal Information

|                         |                                                             |        | UCC27210, | UCC27211 |         |       |

|-------------------------|-------------------------------------------------------------|--------|-----------|----------|---------|-------|

|                         | THERMAL METRIC                                              | D      | DDA       | DRM      | DPR     | UNIT  |

|                         |                                                             | 8 PINS | 8 PINS    | 8 PINS   | 10 PINS |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(1)</sup>       | 111.8  | 37.7      | 33.9     | 36.8    |       |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance <sup>(2)</sup>    | 56.9   | 47.2      | 33.2     | 36.0    |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance <sup>(3)</sup>         | 53.0   | 9.6       | 11.4     | 14.0    | °C/W  |

| ΨJT                     | Junction-to-top characterization parameter <sup>(4)</sup>   | 7.8    | 2.8       | 0.4      | 0.3     | °C/vv |

| ΨЈВ                     | Junction-to-board characterization parameter <sup>(5)</sup> | 52.3   | 9.4       | 11.7     | 14.2    |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance <sup>(6)</sup> | n/a    | 3.6       | 2.3      | 3.4     |       |

(1) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(2) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(3) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(4) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>0JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

(5) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>0JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

6

Copyright © 2011-2014, Texas Instruments Incorporated

## 7.5 Electrical Characteristics

$V_{DD} = V_{HB} = 12$  V,  $V_{HS} = V_{SS} = 0$  V, no load on LO or HO,  $T_A = T_J = -40^{\circ}$ C to 140°C, (unless otherwise noted)

|                    | PARAMETER                                                                    |          | TEST CONDITIONS                                       | MIN   | TYP    | MAX  | UNI        |

|--------------------|------------------------------------------------------------------------------|----------|-------------------------------------------------------|-------|--------|------|------------|

| SUPPL              | PPLY CURRENTS                                                                |          |                                                       |       |        |      |            |

| DD                 | V <sub>DD</sub> quiescent current                                            |          | V(LI) = V(HI) = 0 V                                   | 0.05  | 0.085  | 0.17 |            |

| DDO                |                                                                              | UCC27210 |                                                       |       | 2.6    | 5.2  |            |

|                    | V <sub>DD</sub> operating current                                            | UCC27211 | $f = 500 \text{ kHz}, C_{\text{LOAD}} = 0$            |       | 2.5    | 5.2  | mA         |

| НВ                 | Boot voltage quiescent current                                               |          | V(LI) = V(HI) = 0 V                                   | 0.015 | 0.065  | 0.1  |            |

| нво                | Boot voltage operating cur                                                   | rent     | $f = 500 \text{ kHz}, C_{LOAD} = 0$                   |       | 2.5    | 5.0  |            |

| I <sub>HBS</sub>   | HB to V <sub>SS</sub> quiescent curre                                        | nt       | V(HS) = V(HB) = 115 V                                 |       | 0.0005 | 1.0  | μA         |

| I <sub>HBSO</sub>  | HB to V <sub>SS</sub> operating current                                      | nt       | $f = 500 \text{ kHz}, C_{LOAD} = 0$                   |       | 0.07   | 1.2  | mA         |

| INPUT              |                                                                              |          |                                                       |       |        |      |            |

| V <sub>HIT</sub>   | Input voltage threshold                                                      |          | UCC27210                                              | 4.2   | 5.0    | 5.8  |            |

|                    | Input voltage threshold                                                      |          | UCC27210 (DDA only)                                   | 4.2   | 5.0    | 5.9  |            |

| V <sub>LIT</sub>   |                                                                              |          | UCC27210                                              | 2.4   | 3.2    | 4.0  | V          |

|                    |                                                                              |          | UCC27210 (DDA only)                                   | 2.4   | 3.2    | 4.0  |            |

| V <sub>IHYS</sub>  | Input voltage hysteresis                                                     |          | 110007040                                             |       | 1.8    |      |            |

| R <sub>IN</sub>    | Input pulldown resistance                                                    |          | UCC27210                                              |       | 102    |      | kΩ         |

| V <sub>HIT</sub>   | Input voltage threshold                                                      |          | UCC27211                                              | 1.9   | 2.3    | 2.7  |            |

|                    |                                                                              |          | UCC27211 (DDA only)                                   | 1.9   | 2.3    | 2.8  | .,         |

| V <sub>LIT</sub>   | Input voltage threshold                                                      |          | UCC27211                                              | 1.3   | 1.6    | 1.9  | V          |

|                    |                                                                              |          | UCC27211 (DDA only)                                   | 1.3   | 1.6    | 2.1  |            |

| V <sub>IHYS</sub>  | Input voltage hysteresis                                                     |          |                                                       |       | 700    |      | m\         |

| R <sub>IN</sub>    | Input pulldown resistance                                                    |          | UCC27211                                              |       | 68     |      | kΩ         |

| UNDER              | VOLTAGE LOCKOUT (UVL                                                         | _0)      |                                                       |       |        |      |            |

| V <sub>DDR</sub>   | V <sub>DD</sub> turnon threshold                                             |          |                                                       | 6.2   | 7.0    | 7.8  |            |

|                    |                                                                              |          | DDA only                                              | 5.8   | 7.0    | 8.1  |            |

| V <sub>DDHYS</sub> | Hysteresis                                                                   |          |                                                       |       | 0.5    |      | .,         |

| V <sub>HBR</sub>   | V <sub>HB</sub> turnon threshold                                             |          |                                                       | 5.6   | 6.7    | 7.9  | V          |

|                    |                                                                              |          | DDA only                                              | 5.3   | 6.7    | 8.0  |            |

| V <sub>HBHYS</sub> | Hysteresis                                                                   |          |                                                       |       | 1.1    |      |            |

|                    | TRAP DIODE                                                                   |          |                                                       |       |        | L    |            |

| V <sub>F</sub>     | Low-current forward voltage                                                  | је       | I <sub>VDD-HB</sub> = 100 μA                          |       | 0.65   | 0.8  | , <i>.</i> |

| V <sub>FI</sub>    | High-current forward volta                                                   | ge       | I <sub>VDD-HB</sub> = 100 mA                          |       | 0.85   | 0.95 | V          |

| R <sub>D</sub>     | Dynamic resistance, ΔVF/                                                     | ΔΙ       | $I_{VDD-HB}$ = 100 mA and 80 mA                       | 0.3   | 0.5    | 0.85 | Ω          |

| LO GAT             | TE DRIVER                                                                    |          |                                                       |       |        | L    |            |

| V <sub>LOL</sub>   | Low-level output voltage                                                     |          | I <sub>LO</sub> = 100 mA                              | 0.05  | 0.09   | 0.19 | , <i>.</i> |

| V <sub>LOH</sub>   | High level output voltage                                                    |          | $I_{LO} = -100 \text{ mA}, V_{LOH} = V_{DD} - V_{LO}$ | 0.1   | 0.16   | 0.29 | V          |

|                    | Peak pull-up current <sup>(1)</sup><br>Peak pull-down current <sup>(1)</sup> |          | $V_{LO} = 0 V$                                        |       | 3.7    |      |            |

|                    |                                                                              |          | $V_{LO} = 12 \text{ V}$                               |       | 4.5    |      | A          |

| HO GA              |                                                                              |          | 1                                                     | I     |        | I    |            |

| V <sub>HOL</sub>   | Low-level output voltage                                                     |          | I <sub>HO</sub> = 100 mA                              | 0.05  | 0.09   | 0.19 |            |

| V <sub>HOH</sub>   | High-level output voltage                                                    |          | $I_{HO}$ = -100 mA, $V_{HOH}$ = $V_{HB}$ - $V_{HO}$   | 0.1   | 0.16   | 0.29 | V          |

|                    | Peak pull-up current <sup>(1)</sup>                                          |          | $V_{HO} = 0 V$                                        |       | 3.7    |      |            |

|                    | Peak pull-down current <sup>(1)</sup>                                        |          | $V_{HO} = 12 V$                                       |       | 4.5    |      | A          |

(1) Ensured by design.

## UCC27210, UCC27211

SLUSAT7F-NOVEMBER 2011-REVISED DECEMBER 2014

www.ti.com

## 7.6 Switching Characteristics: Propagation Delays

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                          | TEST CONDITIONS                 | MIN | TYP | MAX | UNIT |

|-------------------|----------------------------------------------------|---------------------------------|-----|-----|-----|------|

| T <sub>DLFF</sub> | $V_{LI}$ falling to $V_{LO}$ falling               | UCC27210, C <sub>LOAD</sub> = 0 | 15  | 21  | 37  |      |

| T <sub>DHFF</sub> | $V_{\text{HI}}$ falling to $V_{\text{HO}}$ falling |                                 | 15  | 21  | 37  |      |

| T <sub>DLRR</sub> | $V_{LI}$ rising to $V_{LO}$ rising                 |                                 | 15  | 24  | 46  |      |

| T <sub>DHRR</sub> | $V_{HI}$ rising to $V_{HO}$ rising                 |                                 | 15  | 24  | 46  | 20   |

| T <sub>DLFF</sub> | $V_{LI}$ falling to $V_{LO}$ falling               | UCC27211, C <sub>LOAD</sub> = 0 | 10  | 17  | 30  | ns   |

| T <sub>DHFF</sub> | $V_{\text{HI}}$ falling to $V_{\text{HO}}$ falling |                                 | 10  | 17  | 30  |      |

| T <sub>DLRR</sub> | $V_{\text{LI}}$ rising to $V_{\text{LO}}$ rising   |                                 | 10  | 18  | 40  |      |

| T <sub>DHRR</sub> | $V_{HI}$ rising to $V_{HO}$ rising                 |                                 | 10  | 18  | 40  |      |

## 7.7 Switching Characteristics: Delay Matching

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER            | TEST CONDITIONS | MIN                                    | TYP | MAX | UNIT |    |

|-------------------|----------------------|-----------------|----------------------------------------|-----|-----|------|----|

| T <sub>MON</sub>  | From HO OFF to LO ON |                 | $T_J = 25^{\circ}C$                    |     | 3   | 11   | 20 |

|                   |                      | 110007040       | $T_J = -40^{\circ}C$ to $140^{\circ}C$ |     | 3   | 14   | ns |

| T <sub>MOFF</sub> | From LO OFF to HO ON | UCC27210        | $T_J = 25^{\circ}C$                    |     | 3   | 11   |    |

|                   |                      |                 | $T_J = -40^{\circ}C$ to $140^{\circ}C$ |     | 3   | 14   | ns |

| T <sub>MON</sub>  | From HO OFF to LO ON |                 | $T_J = 25^{\circ}C$                    |     | 2   | 9.5  | 20 |

|                   |                      | 110007044       | $T_J = -40^{\circ}C$ to $140^{\circ}C$ |     | 2   | 14   | ns |

| T <sub>MOFF</sub> | From LO OFF to HO ON | UCC27211        | $T_J = 25^{\circ}C$                    |     | 2   | 9.5  |    |

|                   |                      |                 | $T_J = -40^{\circ}C$ to $140^{\circ}C$ | 2   |     | 14   | ns |

## 7.8 Switching Characteristics: Output Rise and Fall Time

over operating free-air temperature range (unless otherwise noted)

| PARAMETER      |              | TEST CONDITIONS                         | MIN | TYP  | MAX | UNIT |

|----------------|--------------|-----------------------------------------|-----|------|-----|------|

| t <sub>R</sub> | LO rise time | $C_{LOAD}$ = 1000 pF, from 10% to 90%   |     | 7.2  |     |      |

| t <sub>R</sub> | HO rise time |                                         |     | 7.2  |     |      |

| t <sub>F</sub> | LO fall time | $C_{LOAD}$ = 1000 pF, from 90% to 10%   |     | 5.5  |     | ns   |

| t <sub>F</sub> | HO fall time |                                         |     | 5.5  |     |      |

| t <sub>R</sub> | LO, HO       | $C_{LOAD} = 0.1 \ \mu F$ , (3 V to 9 V) |     | 0.36 | 0.6 |      |

| t <sub>F</sub> | LO, HO       | $C_{LOAD} = 0.1 \ \mu F$ , (9 V to 3 V) |     | 0.15 | 0.4 | μs   |

## 7.9 Switching Characteristics: Miscellaneous

over operating free-air temperature range (unless otherwise noted)

|     | PARAMETER                                                                                           | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----|-----------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| Mir | nimum input pulse width that chang                                                                  |                 |     | 50  | ~~  |      |

| Boo | Bootstrap diode turnoff time <sup>(1)(2)</sup> $I_F = 20 \text{ mA}, I_{REV} = 0.5 \text{ A}^{(3)}$ |                 |     | 20  |     | ns   |

(1) Ensured by design.

(2)  $I_{F}$ : Forward current applied to bootstrap diode,  $I_{REV}$ : Reverse current applied to bootstrap diode. (3) Typical values for  $T_{A} = 25^{\circ}$ C.

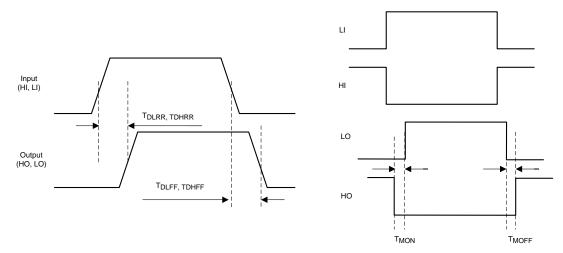

Figure 1. Timing Diagrams

### UCC27210, UCC27211 SLUSAT7F – NOVEMBER 2011 – REVISED DECEMBER 2014

www.ti.com

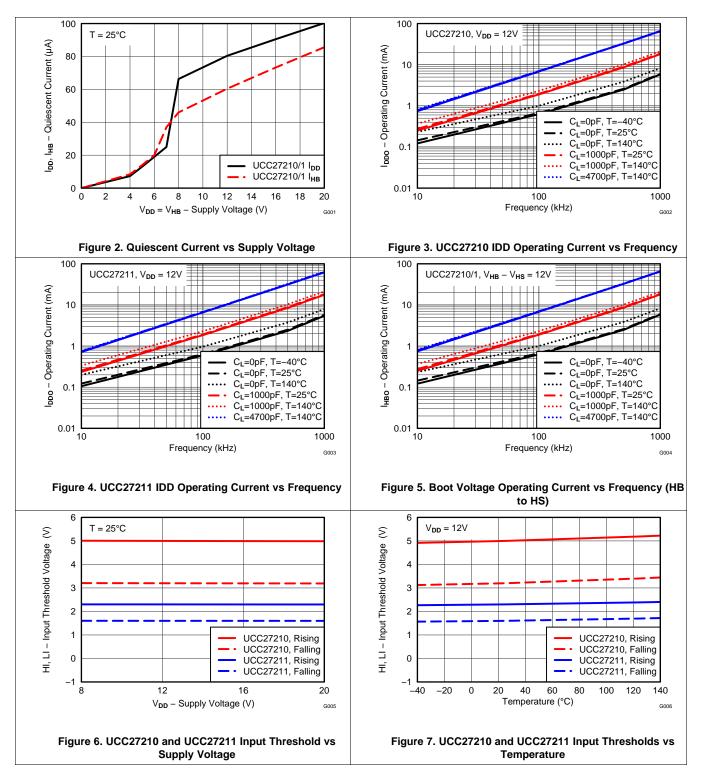

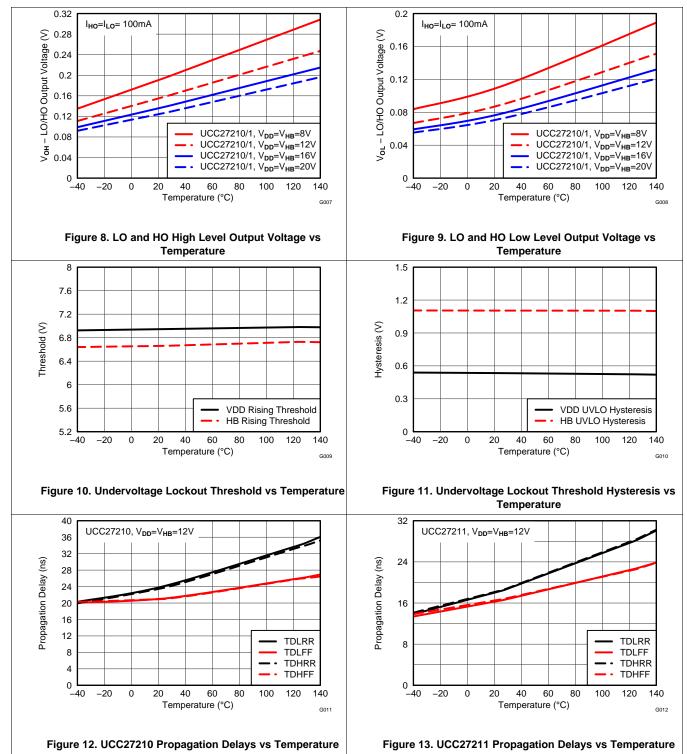

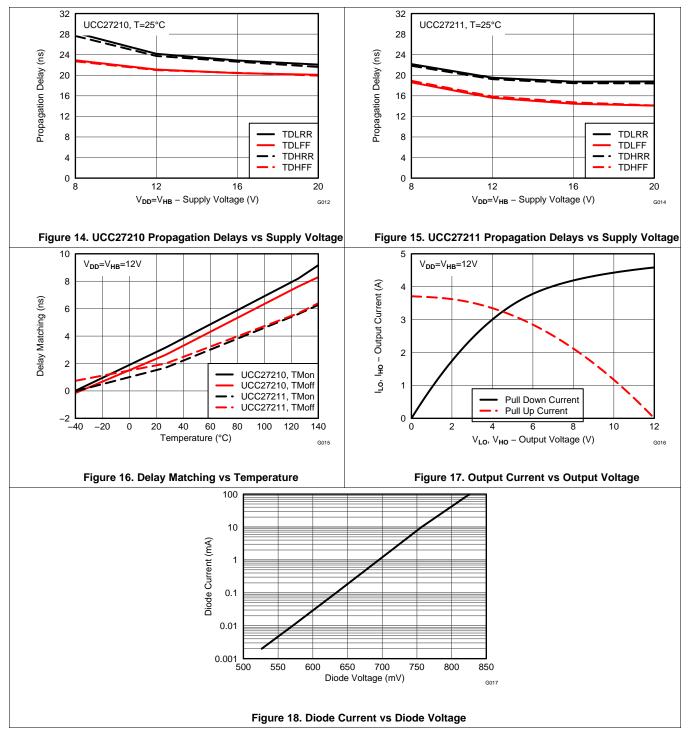

## 7.10 Typical Characteristics

## **Typical Characteristics (continued)**

## UCC27210, UCC27211

SLUSAT7F - NOVEMBER 2011 - REVISED DECEMBER 2014

www.ti.com

## **Typical Characteristics (continued)**

## 8 Detailed Description

#### Overview 8.1

drivers which are designed to drive both the high side and low side of N-channel MOSFETs in a half-/full-bridge or synchronous buck configuration. The floating high-side driver can operate with supply voltages of up to 120 V. This allows for N-channel MOSFET control in half-bridge, full-bridge, push pull, two-switch forward and active clamp forward converters.

The UCC27210 and UCC27211 devices feature 4-A source/sink capability, industry best-in-class switching characteristics and a host of other features listed in Table 1. These features combine to ensure efficient, robust and reliable operation in high-frequency switching power circuits.

| FEATURE                                                                           | BENEFIT                                                                                                                                                  |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-A source and sink current with 0.9- $\Omega$ output resistance                  | High peak current ideal for driving large power MOSFETs with minimal power loss (fast-drive capability at Miller plateau)                                |

| Input pins (HI and LI) can directly handle -10 VDC up to 20 VDC                   | Increased robustness and ability to handle under/overshoot. Can interface directly to gate-drive transformers without having to use rectification diodes |

| 120-V internal boot diode                                                         | Provides voltage margin to meet telecom 100-V surge requirements                                                                                         |

| Switch node (HS pin) able to handle –18 V maximum for 100 ns                      | Allows the high-side channel to have extra protection from inherent negative voltages caused parasitic inductance and stray capacitance.                 |

| Robust ESD circuitry to handle voltage spikes                                     | Excellent immunity to large dV/dT conditions                                                                                                             |

| 18-ns propagation delay with 7.2-ns / 5.5-ns rise/fall Times                      | Best-in-class switching characteristics and extremely low-pulse transmission distortion                                                                  |

| 2-ns (typ) delay matching between channels                                        | Avoids transformer volt-second offset in bridge                                                                                                          |

| Symmetrical UVLO circuit                                                          | Ensures high-side and low-side shut down at the same time                                                                                                |

| CMOS optimized threshold or TTL optimized thresholds with<br>increased hysteresis | Complementary to analog or digital PWM controllers. Increased<br>hysteresis offers added noise immunity                                                  |

### Table 1. UCC27210 and UCC27211 Highlights

In the UCC27210 and UCC27211 devices, the high side and low side each have independent inputs which allow maximum flexibility of input control signals in the application. The boot diode for the high-side driver bias supply is internal to the UCC27210 and UCC27211. The UCC27210 is the Pseudo-CMOS compatible input version and the UCC27211 is the TTL or logic compatible version. The high-side driver is referenced to the switch node (HS) which is typically the source pin of the high-side MOSFET and drain pin of the low-side MOSFET. The low-side driver is referenced to  $V_{SS}$  which is typically ground. The functions contained are the input stages, UVLO protection, level shift, boot diode, and output driver stages.

UCC27210, UCC27211

SLUSAT7F-NOVEMBER 2011-REVISED DECEMBER 2014

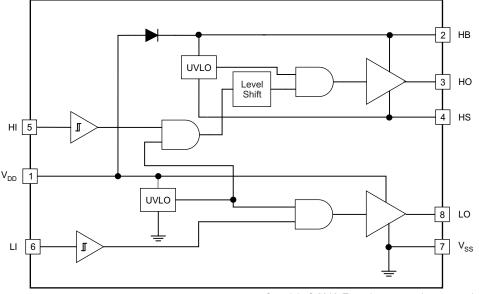

## 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

## 8.3 Feature Description

### 8.3.1 Input Stages

The input stages provide the interface to the PWM output signals. The input impedance of the UCC27210 is 100 k $\Omega$  nominal and input capacitance is approximately 2 pF. The 100 k $\Omega$  is a pull-down resistance to V<sub>SS</sub> (ground). The UCC27210 Pseudo-CMOS input structure has been designed to provide large hysteresis and at the same time to allows interfacing to a multitude of analog or digital PWM controllers. In some CMOS designs, the input thresholds are determined as a percentage of VDD. By doing so, the high-level input threshold can become unreasonably high and unusable. The UCC27210 recognizes the fact that VDD levels are trending downward and it therefore provides a rising threshold with 5.0 V (typical) and falling threshold with 3.2 V (typical). The input hysteresis of the UCC27210 is 1.8 V (typical).

The input stages of the UCC27211 have impedance of 70 k $\Omega$  nominal and input capacitance is approximately 2 pF. Pull-down resistance to V<sub>SS</sub> (ground) is 70 k $\Omega$ . The logic level compatible input provides a rising threshold of 2.3 V and a falling threshold of 1.6 V.

### 8.3.2 Undervoltage Lockout (UVLO)

The bias supplies for the high-side and low-side drivers have UVLO protection.  $V_{DD}$  as well as  $V_{HB}$  to  $V_{HS}$  differential voltages are monitored. The  $V_{DD}$  UVLO disables both drivers when  $V_{DD}$  is below the specified threshold. The rising  $V_{DD}$  threshold is 7.0 V with 0.5-V hysteresis. The VHB UVLO disables only the high-side driver when the  $V_{HB}$  to  $V_{HS}$  differential voltage is below the specified threshold. The  $V_{HB}$  UVLO rising threshold is 6.7 V with 1.1-V hysteresis.

## 8.3.3 Level Shift

The level shift circuit is the interface from the high-side input to the high-side driver stage which is referenced to the switch node (HS). The level shift allows control of the HO output referenced to the HS pin and provides excellent delay matching with the low-side driver.

### Feature Description (continued)

### 8.3.4 Boot Diode

The boot diode necessary to generate the high-side bias is included in the UCC27210 and UCC27211 family of drivers. The diode anode is connected to  $V_{DD}$  and cathode connected to  $V_{HB}$ . With the  $V_{HB}$  capacitor connected to HB and the HS pins, the  $V_{HB}$  capacitor charge is refreshed every switching cycle when HS transitions to ground. The boot diode provides fast recovery times, low diode resistance, and voltage rating margin to allow for efficient and reliable operation.

## 8.3.5 Output Stages

The output stages are the interface to the power MOSFETs in the power train. High slew rate, low resistance and high peak current capability of both output drivers allow for efficient switching of the power MOSFETs. The low-side output stage is referenced from  $V_{DD}$  to  $V_{SS}$  and the high side is referenced from  $V_{HB}$  to  $V_{HS}$ .

## 8.4 Device Functional Modes

The device operates in normal mode and UVLO mode. See the *Undervoltage Lockout (UVLO)* section for information on UVLO operation mode. In the normal mode the output state is dependent on states of the HI and LI pins. Table 2 lists the output states for different input pin combinations.

| HI Pin | LI Pin HO <sup>(1)</sup> |   | LO <sup>(2)</sup> |  |  |  |  |  |  |  |  |  |

|--------|--------------------------|---|-------------------|--|--|--|--|--|--|--|--|--|

| L      | L                        | L | L                 |  |  |  |  |  |  |  |  |  |

| L      | Н                        | L | Н                 |  |  |  |  |  |  |  |  |  |

| Н      | L                        | Н | L                 |  |  |  |  |  |  |  |  |  |

| Н      | Н                        | Н | Н                 |  |  |  |  |  |  |  |  |  |

### Table 2. Device Logic Table

(1) HO is measured with respect to HS.

(2) LO is measured with respect to VSS.

TEXAS INSTRUMENTS

www.ti.com

## 9 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

To effect fast switching of power devices and reduce associated switching power losses, a powerful gate driver is employed between the PWM output of controllers and the gates of the power semiconductor devices. Also, gate drivers are indispensable when it is impossible for the PWM controller to directly drive the gates of the switching devices. With the advent of digital power, this situation will be often encountered because the PWM signal from the digital controller is often a 3.3-V logic signal which cannot effectively turn on a power switch. Level shifting circuitry is needed to boost the 3.3-V signal to the gate-drive voltage (such as 12 V) in order to fully turn on the power device and minimize conduction losses. Traditional buffer drive circuits based on NPN/PNP bipolar transistors in totem-pole arrangement, being emitter follower configurations, prove inadequate with digital power because they lack level-shifting capability. Gate drivers effectively combine both the level-shifting and buffer-drive functions. Gate drivers also find other needs such as minimizing the effect of high-frequency switching noise by locating the high-current driver physically close to the power switch, driving gate-drive transformers and controlling floating power-device gates, reducing power dissipation and thermal stress in controllers by moving gate charge power losses from the controller into the driver.

Finally, emerging wide band-gap power device technologies such as GaN based switches, which are capable of supporting very high switching frequency operation, are driving very special requirements in terms of gate drive capability. These requirements include operation at low VDD voltages (5 V or lower), low propagation delays and availability in compact, low-inductance packages with good thermal capability. In summary gate-driver devices are extremely important components in switching power, combining benefits of high-performance, low-cost component count and board-space reduction as well as simplified system design.

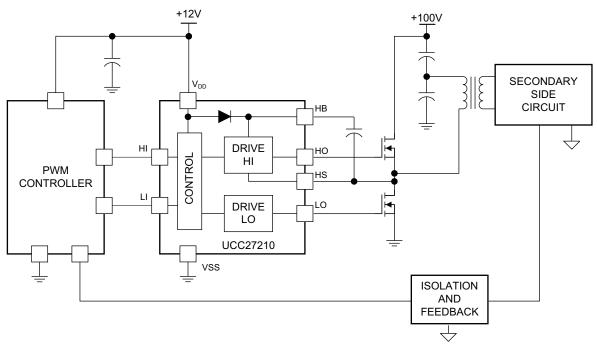

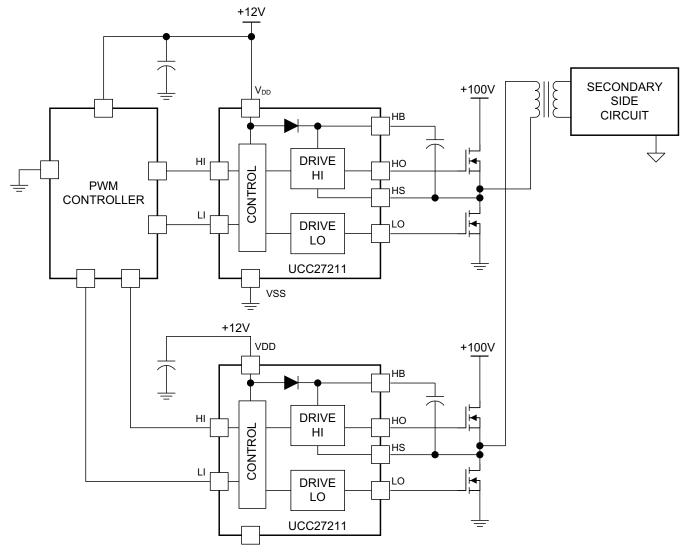

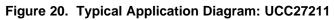

## 9.2 Typical Application

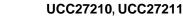

Figure 19. Typical Application Diagram: UCC27210

## **Typical Application (continued)**

## 9.2.1 Design Requirements

| Table 5. Design Opecifications |               |  |  |  |  |  |  |  |

|--------------------------------|---------------|--|--|--|--|--|--|--|

| DESIGN PARAMETER               | EXAMPLE VALUE |  |  |  |  |  |  |  |

| Supply voltage, VDD            | 12 V          |  |  |  |  |  |  |  |

| Voltage on HS, VHS             | 0 V to 100 V  |  |  |  |  |  |  |  |

| Voltage on HB, VHB             | 12 V to 112 V |  |  |  |  |  |  |  |

| Output current rating, IO      | -4 A to 4 A   |  |  |  |  |  |  |  |

| Operating frequency            | 500 kHz       |  |  |  |  |  |  |  |

**Table 3. Design Specifications**

TEXAS INSTRUMENTS

www.ti.com

### 9.2.2 Detailed Design Procedure

### 9.2.2.1 Input Threshold Type

The UCC27210 and UCC27211 have an input maximum voltage range from -10 V to 20 V. This increased robustness means that both parts can be directly interfaced to gate drive transformers. The UCC27210 features pseudo CMOS compatible inputs and UCC27211 features TTL compatible input threshold logic, with wide hysteresis. The threshold voltage levels are low voltage and independent of the VDD supply voltage, which allows compatibility with both logic-level input signals from microcontrollers as well as higher-voltage input signals from analog controllers. See the *Electrical Characteristics* table for the actual input threshold voltage levels and UCC27210 and UCC27211 devices.

## 9.2.2.2 V<sub>DD</sub> Bias Supply Voltage

The bias supply voltage to be applied to the VDD pin of the device should never exceed the values listed in the *Recommended Operating Conditions* table. However, different power switches demand different voltage levels to be applied at the gate terminals for effective turnon and turnoff. With certain power switches, a positive gate voltage may be required for turnon and a negative gate voltage may be required for turnoff, in which case the VDD bias supply equals the voltage differential. With a wide operating range from 8 V to 17 V, the UCC27210 and UCC27211 devices can be used to drive a variety of power switches, such as Si MOSFETs, IGBTs, and wide-bandgap power semiconductors (such as GaN, certain types of which allow no higher than 6 V to be applied to the gate terminals).

### 9.2.2.3 Peak Source and Sink Currents

Generally, the switching speed of the power switch during turnon and turnoff should be as fast as possible in order to minimize switching power losses. The gate driver device must be able to provide the required peak current for achieving the targeted switching speeds with the targeted power MOSFET. The system requirement for the switching speed is typically described in terms of the slew rate of the drain-to-source voltage of the power MOSFET (such as  $dV_{DS}/dt$ ). For example, the system requirement might state that a SPP20N60C3 power MOSFET must be turned-on with a  $dV_{DS}/dt$  of 20V/ns or higher with a DC bus voltage of 400 V in a continuous-conduction-mode (CCM) boost PFC-converter application. This type of application is an inductive hard-switching application and reducing switching power losses is critical. This requirement means that the entire drain-to-source voltage swing during power MOSFET turnon event (from 400 V in the OFF state to  $V_{DS(on)}$  in on state) must be completed in approximately 20 ns or less. When the drain-to-source voltage swing occurs, the Miller charge of the power MOSFET (QGD parameter in SPP20N60C3 data sheet is 33 nC typical) is supplied by the peak current of gate driver. According to power MOSFET inductive switching mechanism, the gate-to-source voltage of the power MOSFET at this time is the Miller plateau voltage, which is typically a few volts higher than the threshold voltage of the power MOSFET,  $V_{GS(TH)}$ .

To achieve the targeted dV<sub>DS</sub>/dt, the gate driver must be capable of providing the Q<sub>GD</sub> charge in 20 ns or less. In other words a peak current of 1.65 A (= 33 nC / 20 ns) or higher must be provided by the gate driver. The UCC27210 and UCC27211 gate driver is capable of providing 4-A peak sourcing current which clearly exceeds the design requirement and has the capability to meet the switching speed needed. The 2.4x overdrive capability provides an extra margin against part-to-part variations in the Q<sub>GD</sub> parameter of the power MOSFET along with additional flexibility to insert external gate resistors and fine tune the switching speed for efficiency versus EMI optimizations. However, in practical designs the parasitic trace inductance in the gate drive circuit of the PCB will have a definitive role to play on the power MOSFET switching speed. The effect of this trace inductance is to limit the dl/dt of the output current pulse of the gate driver. In order to illustrate this, consider output current pulse waveform from the gate driver to be approximated to a triangular profile, where the area under the triangle (1/2 ×I<sub>PEAK</sub> × time) would equal the total gate charge of the power MOSFET (QG parameter in SPP20N60C3 power MOSFET datasheet = 87 nC typical). If the parasitic trace inductance limits the dl/dt then a situation may occur in which the full peak current capability of the gate driver is not fully achieved in the time required to deliver the QG required for the power MOSFET switching. In other words the time parameter in the equation would dominate and the IPEAK value of the current pulse would be much less than the true peak current capability of the device, while the required QG is still delivered. Because of this, the desired switching speed may not be realized, even when theoretical calculations indicate the gate driver is capable of achieving the targeted switching speed. Thus, placing the gate driver device very close to the power MOSFET and designing a tight gate drive-loop with minimal PCB trace inductance is important to realize the full peak-current capability of the gate driver.

### 9.2.2.4 Propagation Delay

The acceptable propagation delay from the gate driver is dependent on the switching frequency at which it is used and the acceptable level of pulse distortion to the system. The UCC27210 features 21 ns and the UCC27211 features 17 ns (typical) propagation delays which ensures very little pulse distortion and allows operation at very high-frequencies. See the *Electrical Characteristics* table for the propagation and switching characteristics of the UCC27210 and UCC27211 devices.

## 9.2.2.5 Power Dissipation

Power dissipation of the gate driver has two portions as shown in Equation 1.

$$P_{DISS} = P_{DC} + P_{SW}$$

(1)

(2)

(3)

(4)

The DC portion of the power dissipation is PDC =  $I_Q \times VDD$  where  $I_Q$  is the quiescent current for the driver. The quiescent current is the current consumed by the device to bias all internal circuits such as input stage, reference voltage, logic circuits, protections, and also any current associated with switching of internal devices when the driver output changes state (such as charging and discharging of parasitic capacitances, parasitic shoot-through, and so forth). The UCC27210 and UCC27211 features very low quiescent currents (less than 0.17 mA, refer to the *Electrical Characteristics* table and contain internal logic to eliminate any shoot-through in the output driver stage. Thus the effect of the PDC on the total power dissipation within the gate driver can be safely assumed to be negligible. The power dissipated in the gate-driver package during switching (PSW) depends on the following factors:

- Gate charge required of the power device (usually a function of the drive voltage VG, which is very close to input bias supply voltage VDD)

- Switching frequency

- Use of external gate resistors. When a driver device is tested with a discrete, capacitive load calculating the power that is required from the bias supply is fairly simple. The energy that must be transferred from the bias supply to charge the capacitor is given by Equation 2.

$$EG = \frac{1}{2}C_{LOAD}V_{DD}^{2} f_{SW}$$

where

- C<sub>LOAD</sub> is load capacitor

- V<sub>DD</sub> is bias voltage feeding the driver

There is an equal amount of energy dissipated when the capacitor is charged. This leads to a total power loss given by Equation 3.

$PG = C_{LOAD}V_{DD}{}^2 f_{SW}$

where

• f<sub>SW</sub> is the switching frequency

The switching load presented by a power MOSFET/IGBT is converted to an equivalent capacitance by examining the gate charge required to switch the device. This gate charge includes the effects of the input capacitance plus the added charge needed to swing the drain voltage of the power device as it switches between the ON and OFF states. Most manufacturers provide specifications of typical and maximum gate charge, in nC, to switch the device under specified conditions. Using the gate charge Qg, determine the power that must be dissipated when charging a capacitor which is calculated using the equation  $Q_G = C_{LOAD} \times V_{DD}$  to provide Equation 4 for power.

$$P_{G} = C_{LOAD} V_{DD}^{2} f_{SW} = Q_{G} V_{DD} f_{SW}$$

This power  $P_G$  is dissipated in the resistive elements of the circuit when the MOSFET/IGBT is being turned on or off. Half of the total power is dissipated when the load capacitor is charged during turnon, and the other half is dissipated when the load capacitor is discharged during turnoff. When no external gate resistor is employed between the driver and MOSFET/IGBT, this power is completely dissipated inside the driver package. With the use of external gate-drive resistors, the power dissipation is shared between the internal resistance of driver and external gate resistor.

## UCC27210, UCC27211

SLUSAT7F - NOVEMBER 2011 - REVISED DECEMBER 2014

**FEXAS**

## www.ti.com

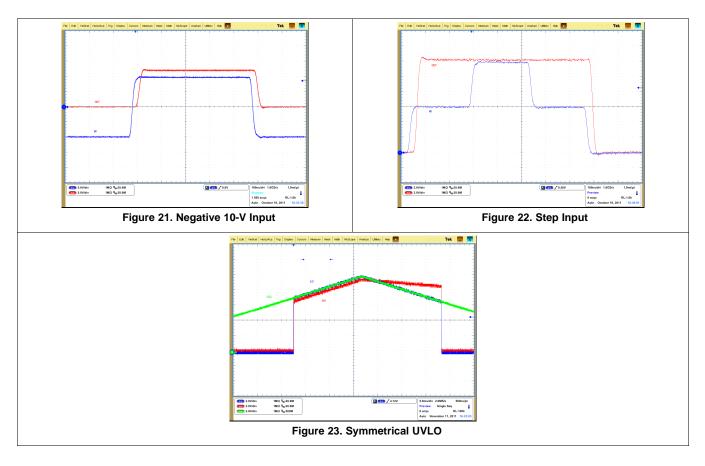

## 9.2.3 Application Curves

Copyright © 2011–2014, Texas Instruments Incorporated

## **10 Power Supply Recommendations**

The bias supply voltage range for which the UCC27210 and UCC27211 device is rated to operate is from 8 V to 17 V. The lower end of this range is governed by the internal undervoltage-lockout (UVLO) protection feature on the V<sub>DD</sub> pin supply circuit blocks. Whenever the driver is in UVLO condition when the V<sub>DD</sub> pin voltage is below the V<sub>(ON)</sub> supply start threshold, this feature holds the output low, regardless of the status of the inputs. The upper end of this range is driven by the 20-V absolute maximum voltage rating of the V<sub>DD</sub> pin of the device (which is a stress rating). Keeping a 3-V margin to allow for transient voltage spikes, the maximum recommended voltage for the V<sub>DD</sub> pin is 17 V. The UVLO protection feature also involves a hysteresis function. This means that when the V<sub>DD</sub> pin bias voltage has exceeded the threshold voltage and device begins to operate, and if the voltage drops, then the device continues to deliver normal functionality unless the voltage drop exceeds the hysteresis specification V<sub>DD(hys)</sub>. Therefore, ensuring that, while operating at or near the 8-V range, the voltage ripple on the auxiliary power supply output is smaller than the hysteresis specification of the device is important to avoid triggering device shutdown. During system shutdown, the device operation continues until the V<sub>DD</sub> pin voltage has dropped below the V<sub>(OFF)</sub> threshold which must be accounted for while evaluating system shutdown timing design requirements. Likewise, at system startup, the device does not begin operation until the  $V_{DD}$  pin voltage has exceeded above the  $V_{(ON)}$  threshold. The quiescent current consumed by the internal circuit blocks of the device is supplied through the  $V_{DD}$  pin. Although this fact is well known, recognizing that the charge for source current pulses delivered by the HO pin is also supplied through the same V<sub>DD</sub> pin is important. As a result, every time a current is sourced out of the HO pin a corresponding current pulse is delivered into the device through the V<sub>DD</sub> pin. Thus ensuring that a local bypass capacitor is provided between the V<sub>DD</sub> and GND pins and located as close to the device as possible for the purpose of decoupling is important. A low ESR, ceramic surface mount capacitor is a must. TI recommends using a capacitor in the range 0.22 uF to 4.7 uF between V<sub>DD</sub> and GND. In a similar manner, the current pulses delivered by the LO pin are sourced from the HB pin. Therefore a 0.022-uF to 0.1-uF local decoupling capacitor is recommended between the HB and HS pins.

## 11 Layout

## 11.1 Layout Guidelines

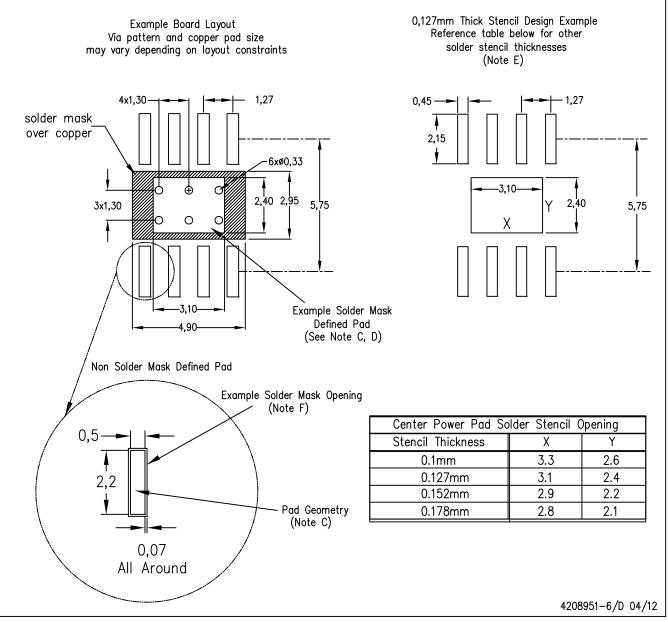

To improve the switching characteristics and efficiency of a design, the following layout rules should be followed.

- Locate the driver as close as possible to the MOSFETs.

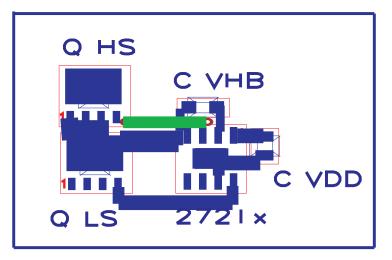

- Locate the  $V_{DD}$ - $V_{SS}$  and  $V_{HB}$ - $V_{HS}$  (bootstrap) capacitors as close as possible to the device (see *Figure 24*).

- Pay close attention to the GND trace. Use the thermal pad of the DDA and DRM package as GND by connecting it to the VSS pin (GND). The GND trace from the driver goes directly to the source of the MOSFET but should not be in the high current path of the MOSFET(S) drain or source current.

- Use similar rules for the HS node as for GND for the high-side driver.

- For systems using multiple UCC27210 and UCC27211 devices we recommend that dedicated decoupling capacitors be located at V<sub>DD</sub>-V<sub>SS</sub> for each device.

- Care should be taken to avoid VDD traces being close to LO, HS, and HO signals.

- Use wide traces for LO and HO closely following the associated GND or HS traces. 60 to 100-mils width is preferable where possible.

- Use as least two or more vias if the driver outputs or SW node must be routed from one layer to another. For GND the number of vias must be a consideration of the thermal pad requirements as well as parasitic inductance.

- Avoid LI and HI (driver input) going close to the HS node or any other high dV/dT traces that can induce significant noise into the relatively high impedance leads.

Keep in mind that a poor layout can cause a significant drop in efficiency or system malfunction versus a good PCB layout and can even lead to decreased reliability of the whole system.

**INSTRUMENTS**

**EXAS**

## 11.2 Layout Example

Figure 24. UCC27210/11 Component Placement

## **11.3 Thermal Considerations**

The useful range of a driver is greatly affected by the drive-power requirements of the load and the thermal characteristics of the package. In order for a gate driver to be useful over a particular temperature range the package must allow for the efficient removal of the heat produced while keeping the junction temperature within rated limits. The thermal metrics for the driver package is listed in *Device Functional Modes*. For detailed information regarding the table, please refer to the Application Note from Texas Instruments entitled *IC Package Thermal Metrics* (SPRA953). The UCC27210 and UCC27211 devices are offered in SOIC (8), PowerPad (8), WSON (10) or VSON (8). The *Thermal Information* section lists the thermal performance metrics related to SOT-23 package.

## **12 Device and Documentation Support**

## **12.1** Documentation Support

## 12.1.1 Related Documentation

These references and links to additional information may be found at www.ti.com

- Additional layout guidelines for PCB land patterns may be found in, QFN/SON PCB Attachment, Application Brief (SLUA271)

- Additional thermal performance guidelines may be found in, *PowerPAD™* Thermally Enhanced Package Application Report, Application Report (SLMA002)

- Additional thermal performance guidelines may be found in, *PowerPAD™ Made Easy*, Application Report (SLMA004)

## 12.2 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

| PARTS    | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL<br>DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |  |

|----------|----------------|--------------|------------------------|---------------------|---------------------|--|

| UCC27210 | Click here     | Click here   | Click here             | Click here          | Click here          |  |

| UCC27211 | Click here     | Click here   | Click here             | Click here          | Click here          |  |

### Table 4. Related Links

## 12.3 Trademarks

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 12.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 12.5 Glossary

## SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

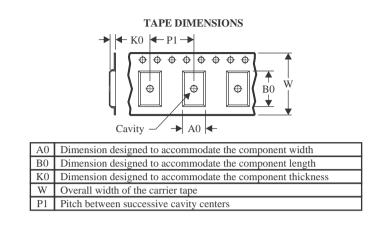

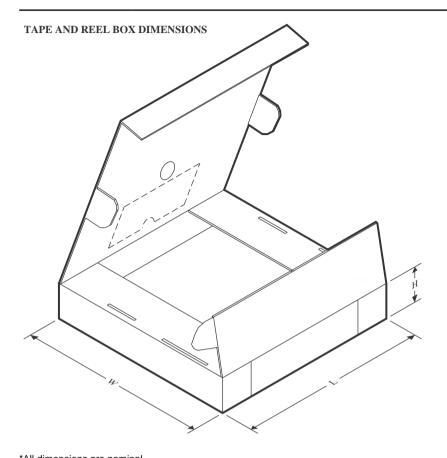

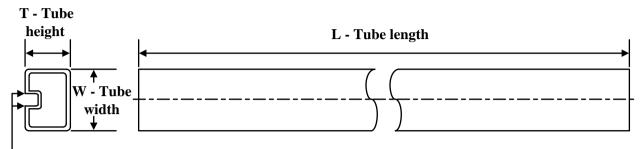

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

10-Dec-2020

## **PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| UCC27210D        | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 140   | 27210                   | Samples |

| UCC27210DDA      | ACTIVE        | SO PowerPAD  | DDA                | 8    | 75             | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 140   | 27210                   | Samples |

| UCC27210DDAR     | ACTIVE        | SO PowerPAD  | DDA                | 8    | 2500           | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 140   | 27210                   | Samples |

| UCC27210DPRR     | ACTIVE        | WSON         | DPR                | 10   | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 140   | UCC<br>27210            | Samples |

| UCC27210DPRT     | ACTIVE        | WSON         | DPR                | 10   | 250            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 140   | UCC<br>27210            | Samples |

| UCC27210DR       | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 140   | 27210                   | Samples |

| UCC27210DRMR     | ACTIVE        | VSON         | DRM                | 8    | 3000           | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 140   | 27210                   | Samples |

| UCC27210DRMT     | ACTIVE        | VSON         | DRM                | 8    | 250            | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 140   | 27210                   | Samples |

| UCC27211D        | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 140   | 27211                   | Samples |

| UCC27211DDA      | ACTIVE        | SO PowerPAD  | DDA                | 8    | 75             | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 140   | 27211                   | Samples |

| UCC27211DDAR     | ACTIVE        | SO PowerPAD  | DDA                | 8    | 2500           | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 140   | 27211                   | Samples |

| UCC27211DPRR     | ACTIVE        | WSON         | DPR                | 10   | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 140   | UCC<br>27211            | Samples |

| UCC27211DPRT     | ACTIVE        | WSON         | DPR                | 10   | 250            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 140   | UCC<br>27211            | Samples |

| UCC27211DR       | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 140   | 27211                   | Samples |

| UCC27211DRMR     | ACTIVE        | VSON         | DRM                | 8    | 3000           | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 140   | 27211                   | Samples |

| UCC27211DRMT     | ACTIVE        | VSON         | DRM                | 8    | 250            | RoHS & Green    | NIPDAUAG                             | Level-1-260C-UNLIM   | -40 to 140   | 27211                   | Samples |

<sup>(1)</sup> The marketing status values are defined as follows: **ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

10-Dec-2020

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".