UCD3138A

SLUSC66E - MARCH 2015-REVISED FEBRUARY 2017

# UCD3138A Highly-Integrated Digital Controller for Isolated Power

#### **Device Overview** 1

#### 1.1 Features

- Digital Control of up to 3 Independent Feedback Loops

- Dedicated PID-Based Hardware

- 2-Pole, 2-Zero Configurable

- Nonlinear Control

- Soft-Start and Soft-Stop with and without Prebias

- Fast Input Voltage Feed Forward Hardware

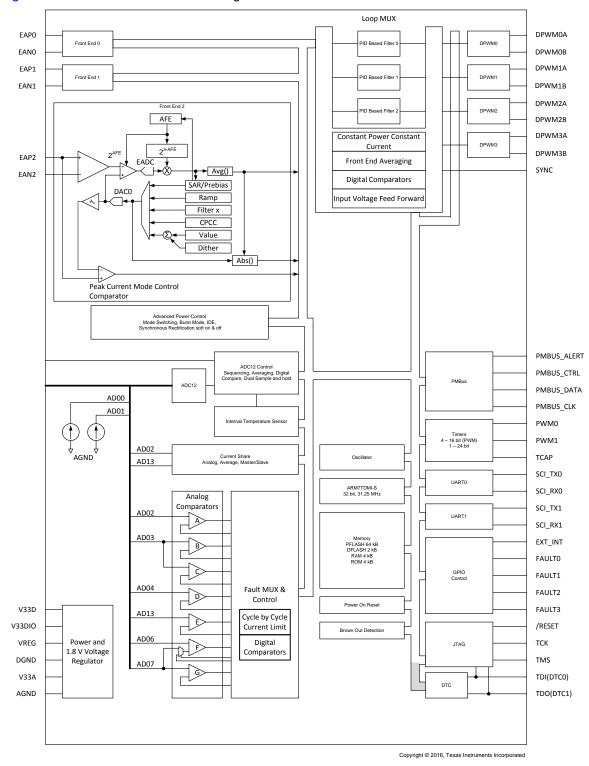

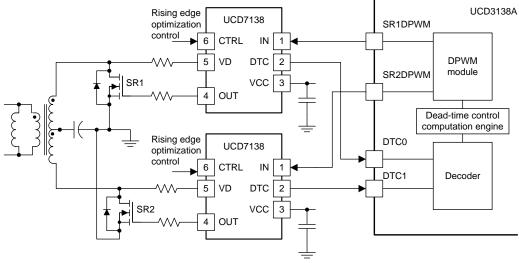

- Synchronous Rectifier Dead Time Optimization Peripheral to Use with UCD7138 Synchronous **Rectifier Driver**

- Up to 16 MHz Error Analog-to-Digital Converter (EADC)

- Configurable Resolution as Small as 1 mV/LSB

- Automatic Resolution Selection

- Up to 8x Oversampling

- Hardware-Based Averaging (up to 8x)

- 10-Bit Effective DAC With 4 Bits of Dither

- Adaptive Sample Trigger Positioning

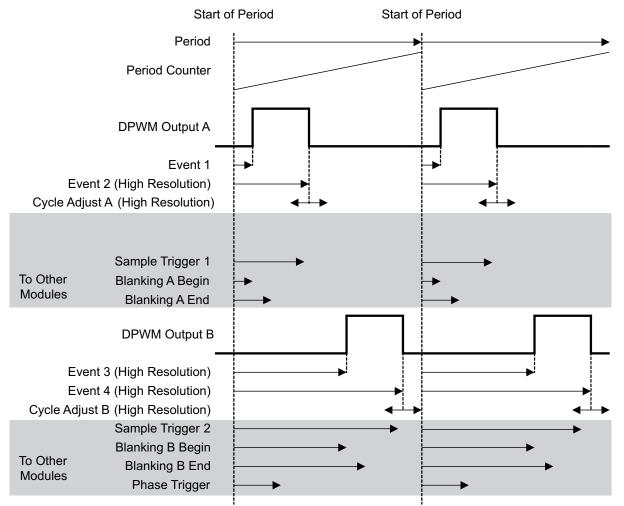

- Up to 8 High-Resolution Digital Pulse Width Modulated (DPWM) Outputs

- 250-ps Pulse Width Resolution

- 4-ns Frequency and Phase Resolution

- Adjustable Phase-Shift Between Outputs

- Adjustable Dead-band Between Pairs

- Cycle-by-Cycle Duty Cycle Matching

- Up to 2-MHz Switching Frequency

- Configurable PWM Edge Movement

- Trailing Modulation

- Leading Modulation

- Triangular Modulation

- Configurable Feedback Control

- Voltage Mode

- Average Current Mode

- Peak Current Mode Control

- Constant Current

- Constant Power

- Configurable Modulation Methods

- Frequency Modulation

- Phase-Shift Modulation

- Pulse Width Modulation

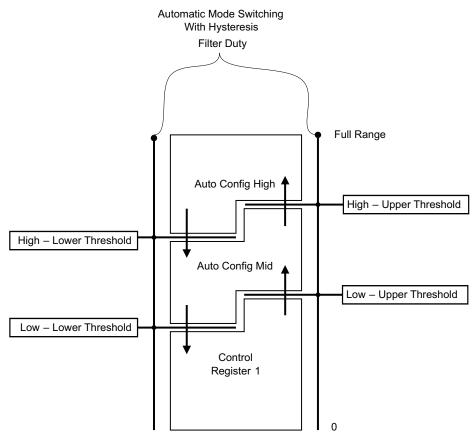

- Fast, Automatic, and Smooth Mode Switching

- Frequency Modulation and PWM

- Phase-Shift Modulation and PWM

- Frequency Modulation and Phase-Shift Modulation

- High Efficiency and Light Load Management

- Burst Mode

- Ideal Diode Emulation

- Synchronous Rectifier Soft On/Off

- Low IC Standby Power

- Primary Side Voltage Sensing

- Copper Trace Current Sensing

- Flux and Phase Current Balancing

- Current Share Bus Support

- Average or Master and Slave

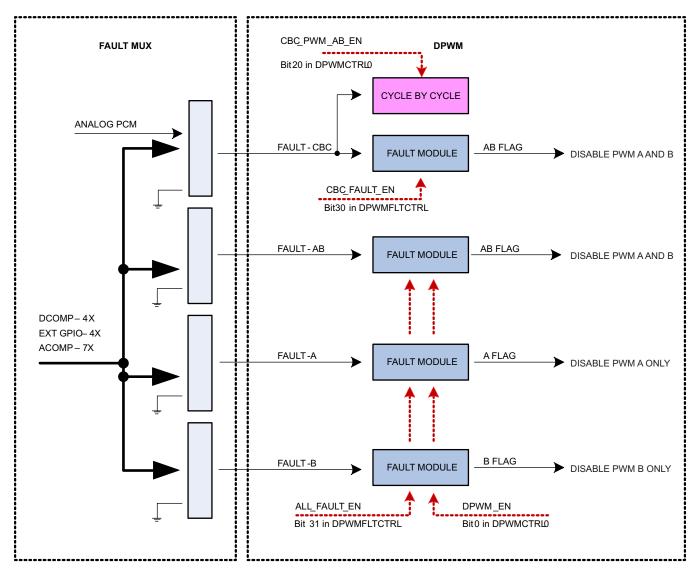

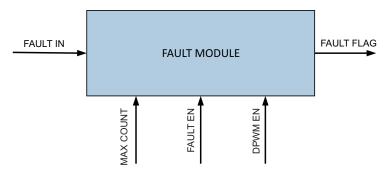

- Feature Rich Fault Protection Options

- 7 High-Speed Analog Comparators

- Cycle-by-Cycle Current Limiting

- Programmable Fault

- External Fault Capability

- 10 Digital Comparators

- Programmable Blanking Time

- Synchronization of DPWM Waveforms Between Multiple UCD3138A devices

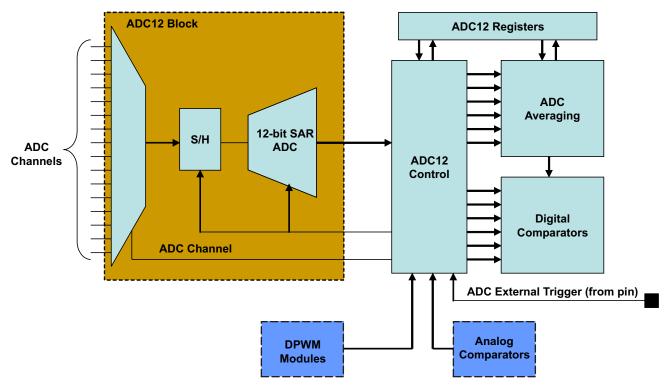

- 14-Channel, 12-Bit, 267-ksps General-Purpose ADC

- Programmable Averaging Filters

- Dual Sample and Hold

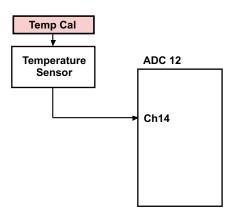

- Internal Temperature Sensor

- Fully Programmable High-Performance 31.25-MHz, 32-Bit ARM7TDMI-S™ Processor

- 32 KB of Program Flash

- 2 KB of Data Flash with ECC

- 4 KB of Data RAM

- Firmware Boot-Load in the Field via PMBus or UART

- Communication Peripherals

- PMBus

- 1 UART

- UART Auto-baud Rate Adjustment

- Timer Capture with Selectable Input Pins

- Up to 5 Additional General Purpose Timers

- Built In Watchdog: BOD and POR

- 64-Pin QFN and 40-Pin QFN Package ٠

- Operating Temperature: -40°C to +125°C

- Debug Interface

- Code Composer Studio<sup>™</sup> with JTAG Interface

- Fusion Digital Power™ Designer GUI Support

#### 1.2 Applications

- Power Supplies and Telecom Rectifiers

- Isolated DC-DC Modules

Power Factor Correction

#### 1.3 Description

The UCD3138A is a digital power supply controller from Texas Instruments offering superior levels of integration and performance in a single-chip solution. The flexible nature of the UCD3138A makes it suitable for a wide variety of power conversion applications. In addition, multiple peripherals inside the device have been specifically optimized to enhance the performance of AC-DC and isolated DC-DC applications and reduce the solution component count in the IT and network infrastructure space.

The UCD3138A controller is a fully programmable solution offering customers complete control of their application, along with ample ability to differentiate their solution. At the same time, TI is committed to simplifying our customers' development effort by offering best-in-class development tools, including application firmware, Code Composer Studio<sup>™</sup> software development environment, and TI's power development GUI which lets customers configure and monitor key system parameters.

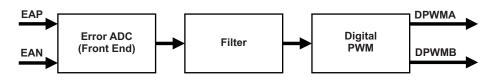

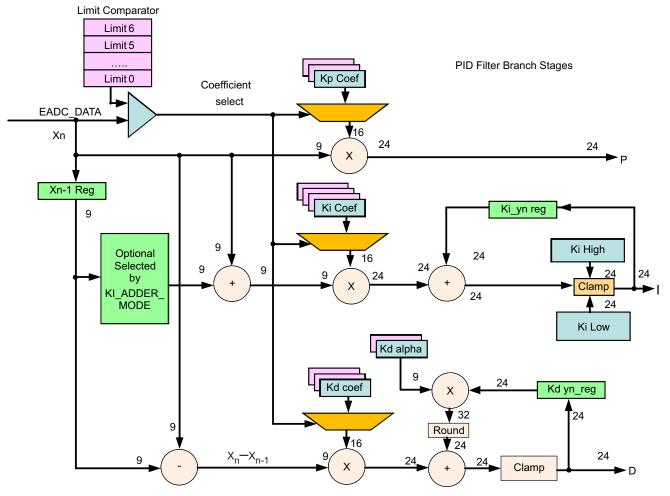

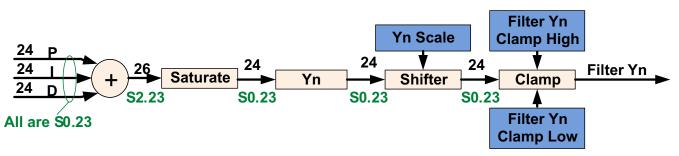

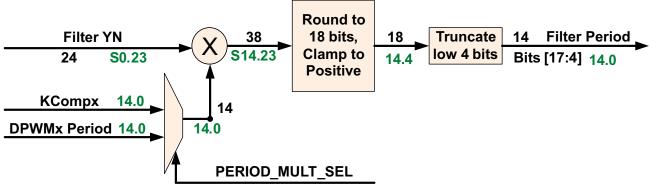

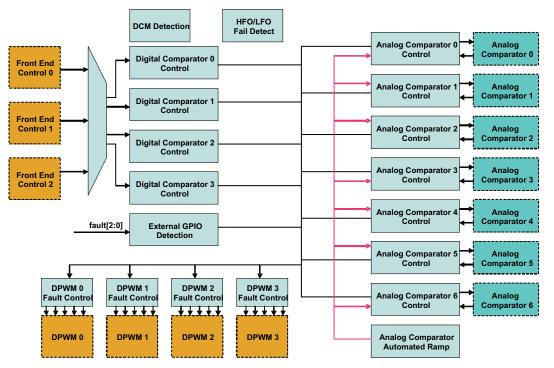

At the core of the UCD3138A controller are the digital control loop peripherals, also known as Digital Power Peripherals (DPPs). Each DPP implements a high-speed digital control loop consisting of a dedicated error analog-to-digital converter (EADC), a PID-based 2-pole-2-zero digital compensator and DPWM outputs with 250-ps pulse width resolution. The device also contains a 12-bit, 267-ksps general-purpose ADC with up to 14 channels, timers, interrupt control, PMBus, and UART communications ports. The device is based on a 32-bit ARM7TDMI-S RISC microcontroller that performs real-time monitoring, configures peripherals, and manages communications. The ARM microcontroller executes its program out of programmable flash memory as well as on-chip RAM and ROM.

In addition to the DPP, specific power management peripherals have been added to enable high efficiency across the entire operating range, high integration for increased power density, reliability, and lowest overall system cost and high flexibility with support for the widest number of control schemes and topologies. Such peripherals include: light load burst mode, synchronous rectification, automatic mode switching, input voltage feed forward, copper trace current sense, ideal diode emulation, constant current constant power control, synchronous rectification soft on and off, peak current mode control, flux balancing, secondary side input voltage sensing, high-resolution current sharing, hardware-configurable soft-start operation with pre-bias, as well as several other features. The device optimizes topology support for voltage mode and peak current mode controlled phase-shifted full bridge, single and dual phase PFC, bridge-less PFC, hard-switched full bridge and half bridge, and LLC half bridge and full bridge.

The UCD3139A is a functional variant of the UCD3138A Digital Power Controller that includes significant improvements over the UCD3138 device For a description of the complete changes made in the UCD3138A, refer to UCD3138A Migration Guide.

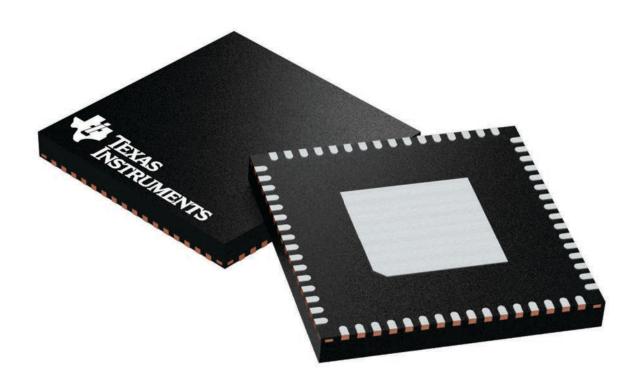

| Device information ? |                 |                          |                   |  |  |  |  |

|----------------------|-----------------|--------------------------|-------------------|--|--|--|--|

| DEVICE NUMBER        | PACKAGE DRAWING | PACKAGE TYPE             | BODY SIZE         |  |  |  |  |

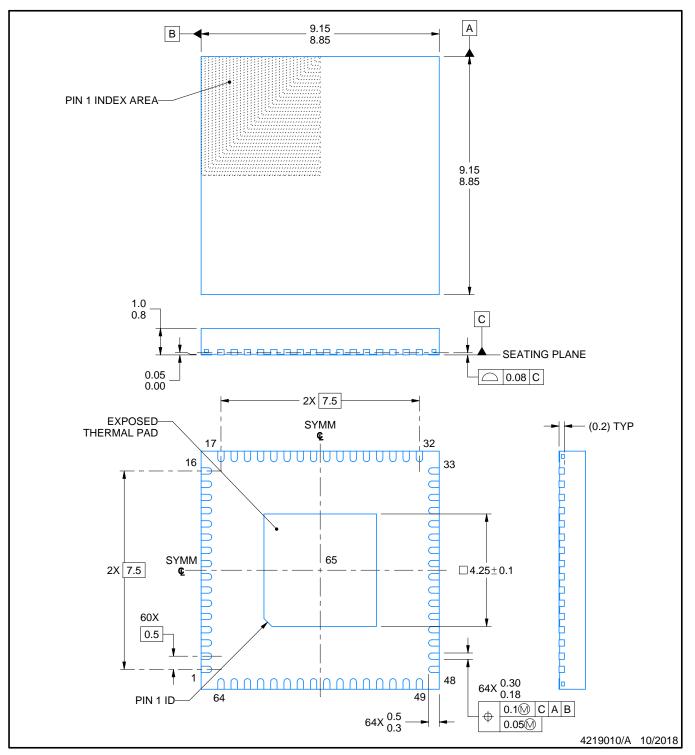

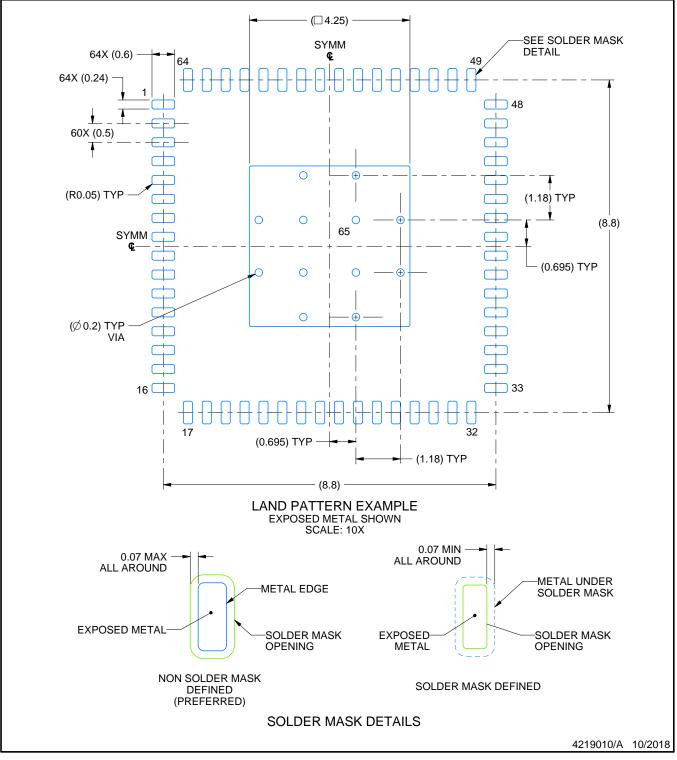

|                      | RGC             | VQFN (64)                | 9.00 mm × 9.00 mm |  |  |  |  |

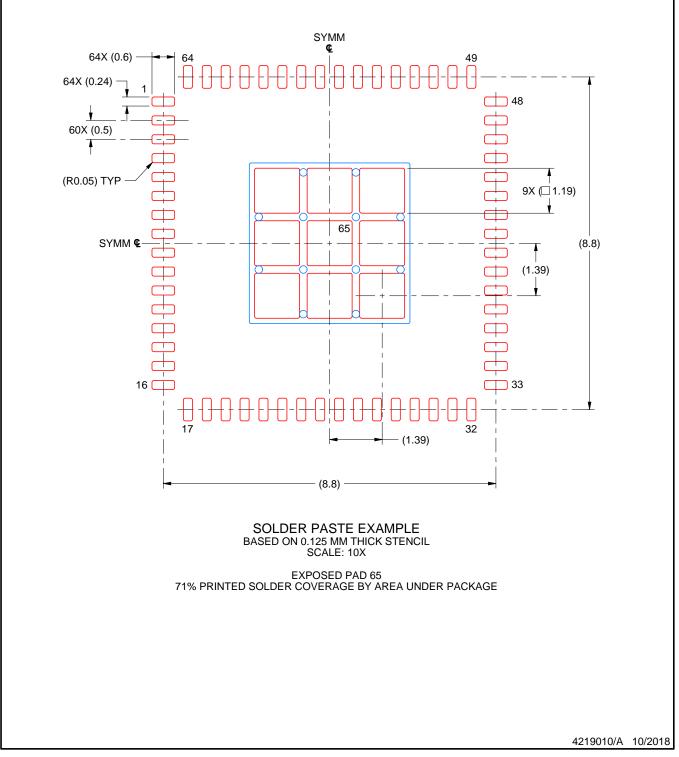

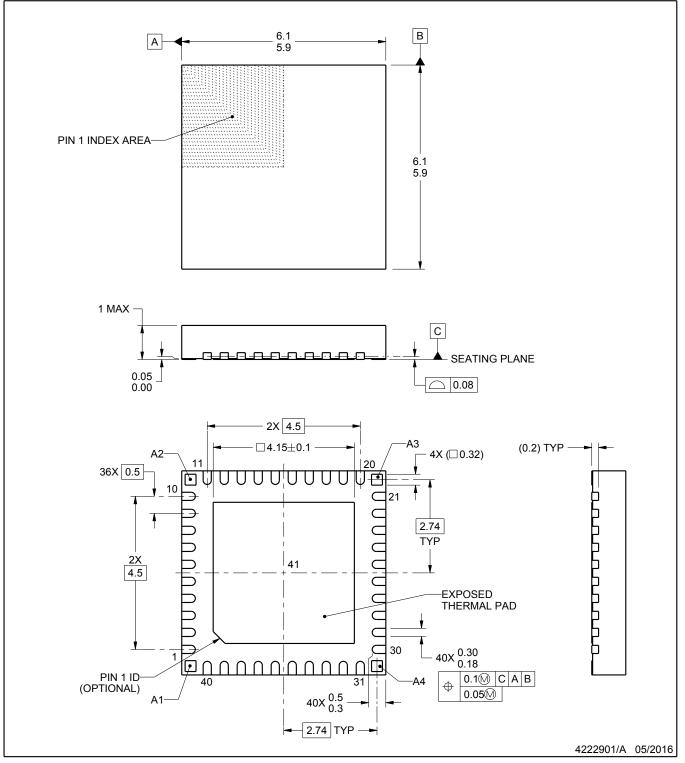

| UCD3138A             | RJA             | VQFN (40) <sup>(3)</sup> | 6.00 mm × 6.00 mm |  |  |  |  |

|                      | RMH             | WQFN (40)                | 6.00 mm × 6.00 mm |  |  |  |  |

## Device Information<sup>(1)</sup>

(1) For all available packages, see the orderable addendum at the end of the datasheet.

(2) 40-pin 6 x 6 x 0.75 mm ultra-thin QFN with corner anchors optimized for IPC9592A Temperature Cycle Testing.

(3) Recommended for new 40-pin designs, optimized for improved performance under temperature cycling test for board level reliability (BLR).

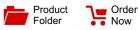

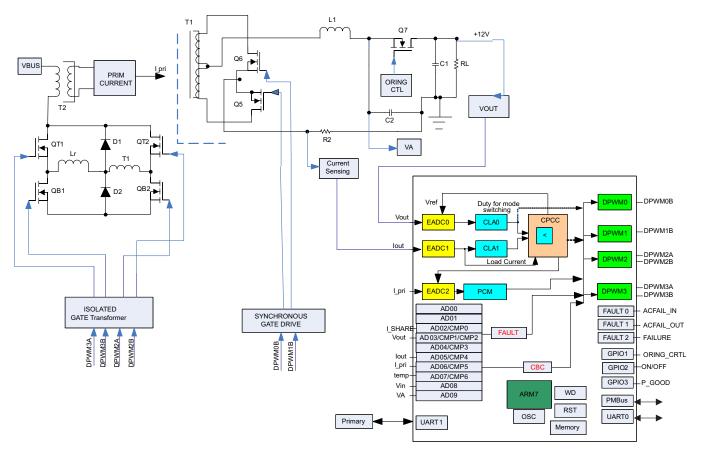

#### 1.4 Functional Block Diagram

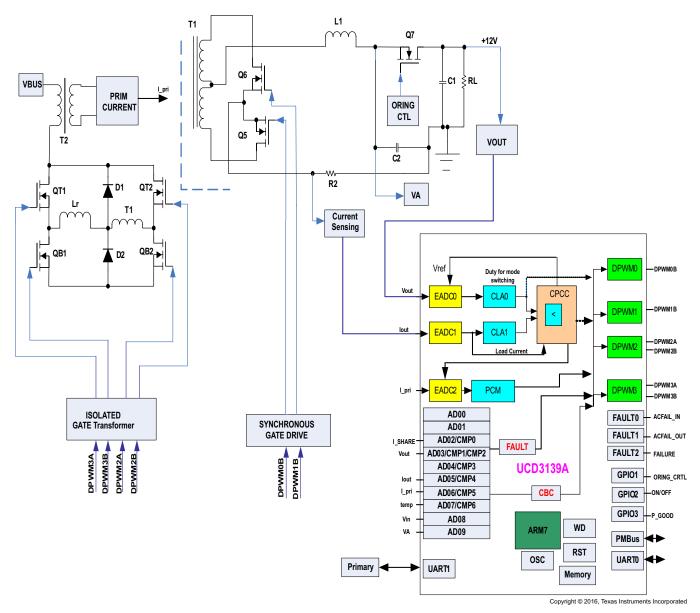

Figure 1-1 shows a functional block diagram of the device.

Figure 1-1. Functional Block Diagram

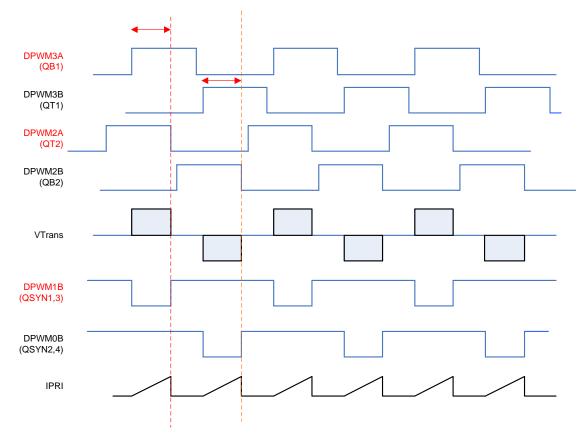

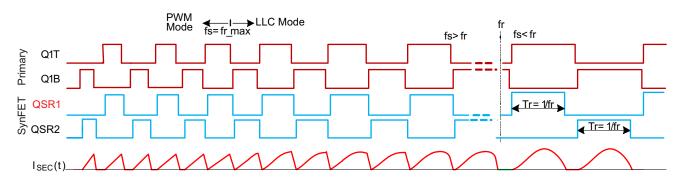

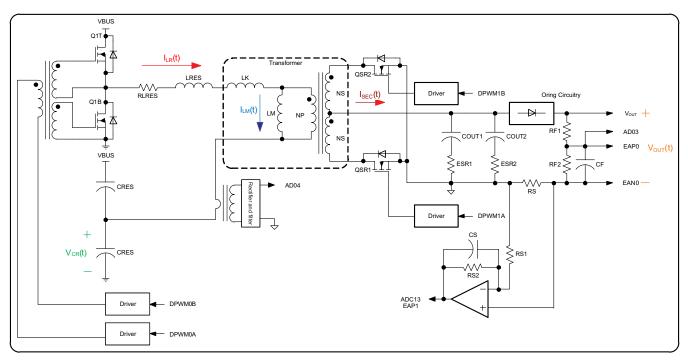

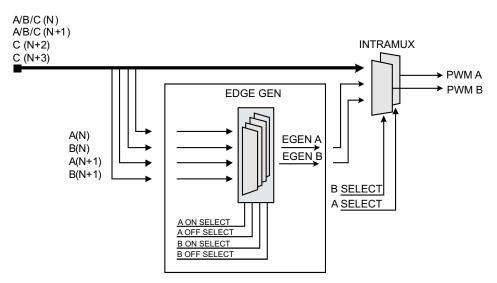

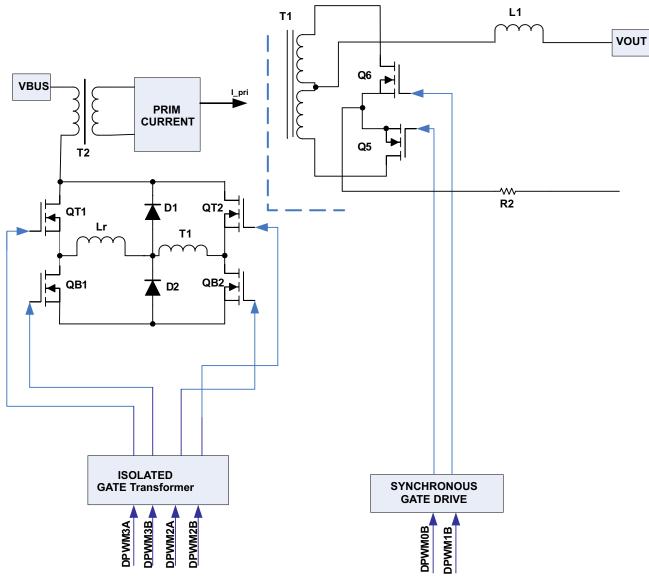

Figure 1-2. Synchronous Rectifier Peripheral Use with Synchronous Rectifier Driver

www.ti.com

Texas

NSTRUMENTS

# **Table of Contents**

| 1 | Devi  | ce Overview                              | <u>1</u>  |

|---|-------|------------------------------------------|-----------|

|   | 1.1   | Features                                 | . 1       |

|   | 1.2   | Applications                             | <u>2</u>  |

|   | 1.3   | Description                              |           |

|   | 1.4   | Functional Block Diagram                 |           |

| 2 | Revi  | sion History                             |           |

| 3 | Devi  | ce Comparison                            |           |

|   | 3.1   | Product Selection Matrix                 | <u>7</u>  |

| 4 | Pin C | Configuration and Functions              |           |

|   | 4.1   | UCD3138A RGC Package                     |           |

|   | 4.2   | UCD3138A RMH Package                     | <u>10</u> |

|   | 4.3   | UCD3138A RJA Package                     | <u>12</u> |

| 5 | Spec  | ifications                               | <u>14</u> |

|   | 5.1   | Absolute Maximum Ratings                 | <u>14</u> |

|   | 5.2   | ESD Ratings                              | <u>14</u> |

|   | 5.3   | Recommended Operating Conditions         | <u>14</u> |

|   | 5.4   | Thermal Information                      | <u>14</u> |

|   | 5.5   | Electrical Characteristics               | <u>15</u> |

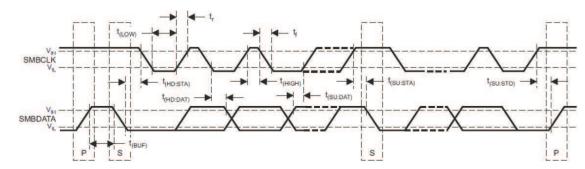

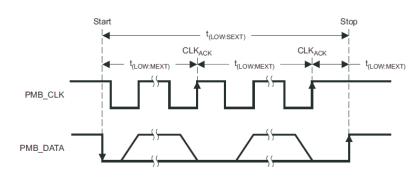

|   | 5.6   | PMBus/SMBus/I <sup>2</sup> C Timing      | <u>19</u> |

|   | 5.7   | Peripherals                              | <u>20</u> |

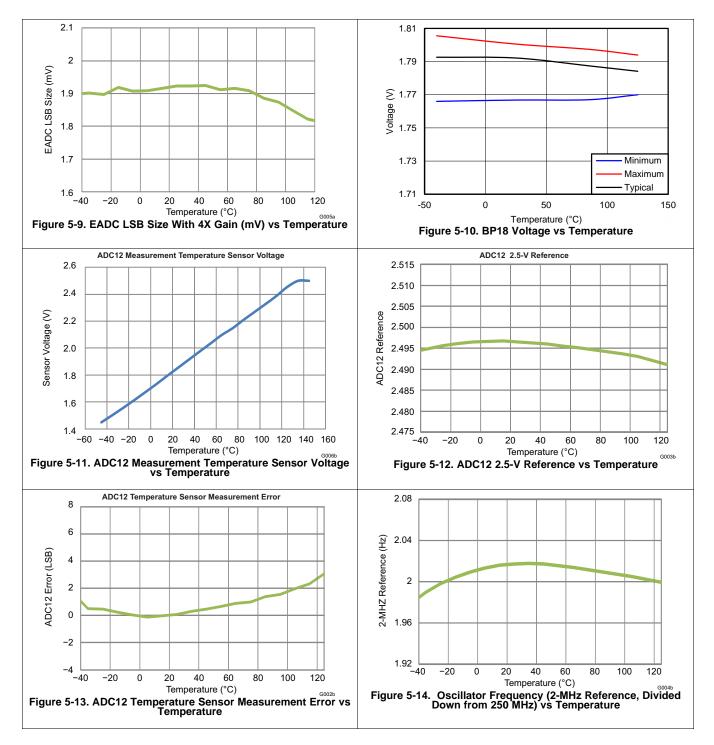

|   | 5.8   | Typical Temperature Characteristics      | <u>28</u> |

| 6 | Para  | metric Measurements Information          | <u>29</u> |

|   | 6.1   | Power-On Reset (POR) and Brown-Out Reset |           |

| _ |       | (BOR)                                    | <u>29</u> |

| 7 | Deta  | iled Description                         | <u>30</u> |

|   |       |                                          |           |

|    | 7.1  | Overview                                        | 30        |

|----|------|-------------------------------------------------|-----------|

|    | 7.2  | ARM Processor                                   | 30        |

|    | 7.3  | Memory                                          | 30        |

|    | 7.4  | System Module                                   | 32        |

|    | 7.5  | Feature Description                             | 34        |

|    | 7.1  | Device Functional Modes                         | 51        |

| 8  | Appl | ication and Implementation                      | 57        |

|    | 8.2  | Application Information                         | 57        |

|    | 8.3  | Typical Application                             | 58        |

| 9  | Pow  | er Supply Recommendations                       | 69        |

|    | 9.1  | Power Supply Decoupling and Bulk Capacitors     | 69        |

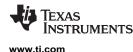

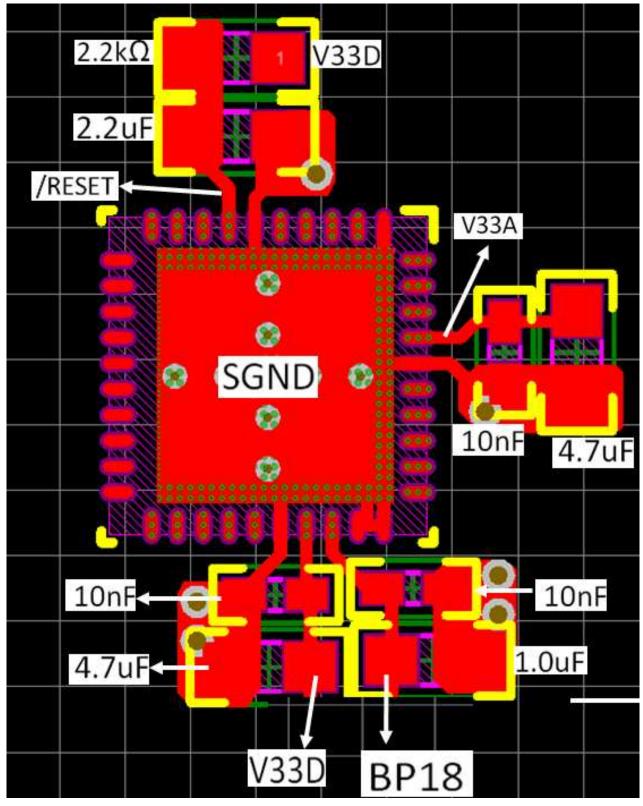

| 10 | Layo | out                                             | 69        |

|    | 10.1 | Layout Guidelines                               | 69        |

|    | 10.2 | Layout Example                                  | 70        |

| 11 | Devi | ce and Documentation Support                    | 72        |

|    | 11.1 | Device Support                                  | 72        |

|    | 11.2 | Documentation Support                           | 74        |

|    | 11.3 | Receiving Notification of Documentation Updates | 74        |

|    | 11.4 | Community Resources                             | 74        |

|    | 11.5 | Trademarks                                      | 74        |

|    | 11.6 | Electrostatic Discharge Caution                 | 74        |

|    | 11.7 | Glossary                                        | 74        |

| 12 | Mecl | hanical Packaging and Orderable                 | _         |

|    |      | mation                                          | <u>74</u> |

|    | 12.1 | Packaging Information                           | <u>74</u> |

|    |      |                                                 |           |

#### 2 **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision D (October 2016) to Revision E Page Added two temperature ranges to the Internal oscillator frequency section. 16 • Changed Layout Example images. ..... 70

#### Changes from Revision C (September 2016) to Revision D

- Added "64-Pin QFN and" to 40-Pin QFN Package bullet.....

- Deleted ICP9592A T/C Qualification bullet.

- Added PACKAGE DRAWING column to the Device Information table.

- Changed Note 2 from "Recommended for new 40-pin designs with advance BLR performance" to "Recommended for new 40-pin designs, optimized for improved performance under temperature cycling test for

- Deleted Note 2, "40-pin 6 x 6 x 0.75 mm ultra-thin QFN with corner anchors optimized for IPC9592A

#### Changes from Revision B (May 2015) to Revision C

- Added the VQFN (40) pin package to the *Device Information* table.

- Added the UCD3138A RJA Package section ..... 12

#### Changes from Revision A (April 2015) to Revision B

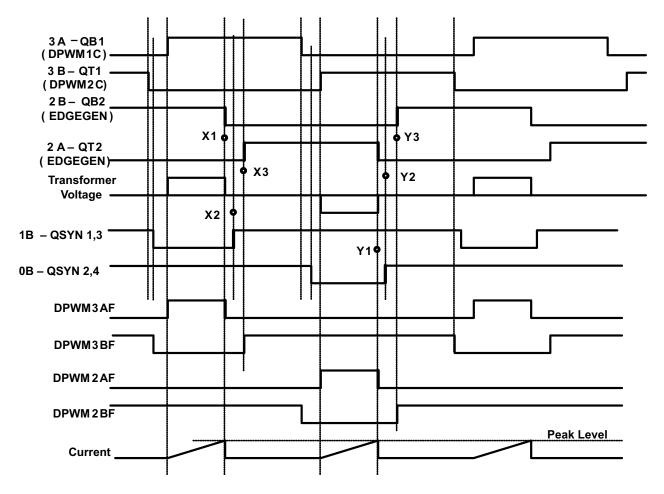

Changed Figure 7-3 image and following notes ..... 54 ٠

#### Changes from Original (March 2015) to Revision A

| Changed the device status From: Product Preview To: Production<br>Changed <i>Feature</i> From: "4KB of Boot ROM Enables Firmware Boot-Load" To: "Firmware Boot-Load"<br>Changed Note 2 of the <i>Device Information</i> table From: "for passing IPC9592A Temperature Cycle Qualification"<br>To: "for IPC9592A Temperature Cycle Testing." | . <u>1</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changed Figure 5-7                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Added Figure 6-1                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Changed Table 7-4 PRIORITY 19 From: CAPTURE_1_INT To: DTC_FLT_INT                                                                                                                                                                                                                                                                           | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

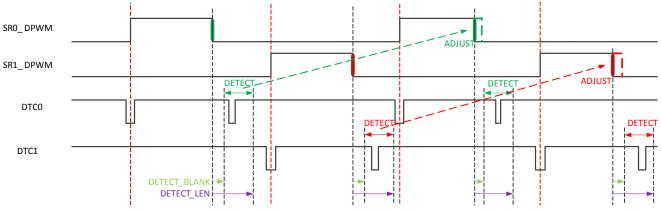

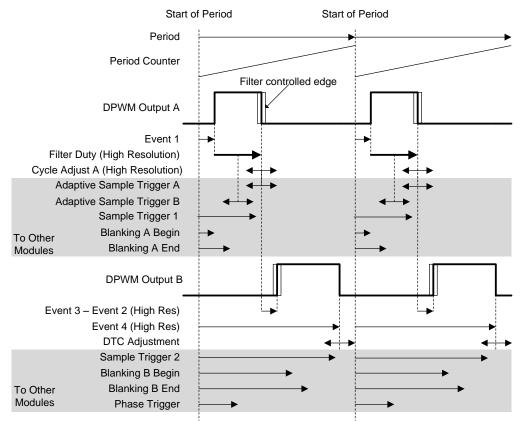

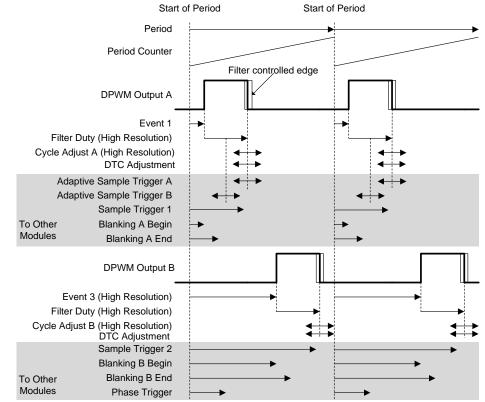

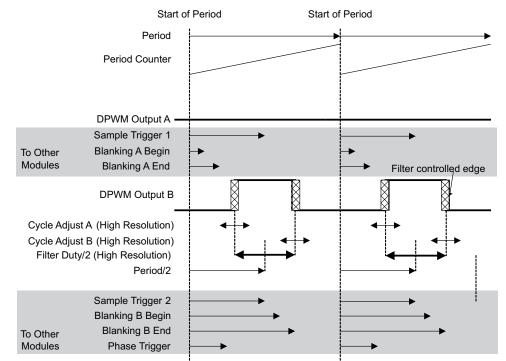

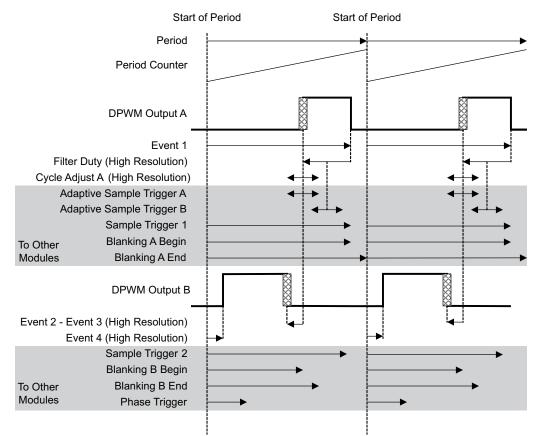

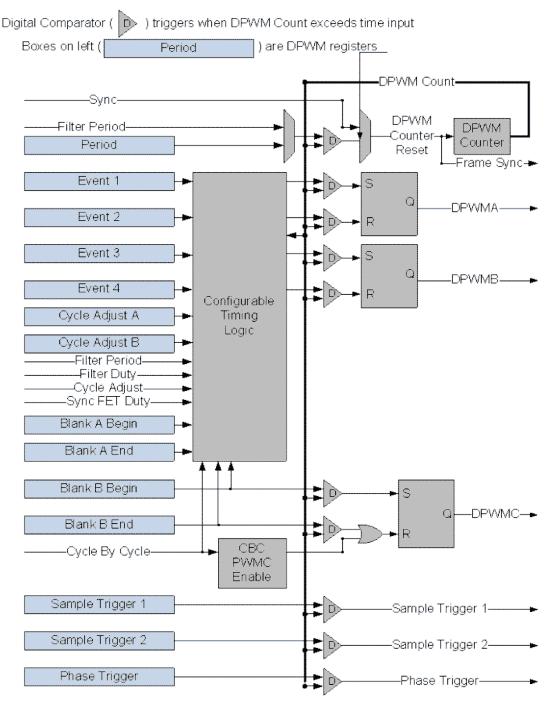

| Changed Figure 7-1 to include DTC Adjustment                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

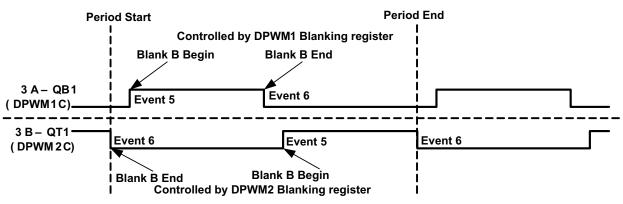

| Changed Figure 7-2 to include DTC Adjustment                                                                                                                                                                                                                                                                                                | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

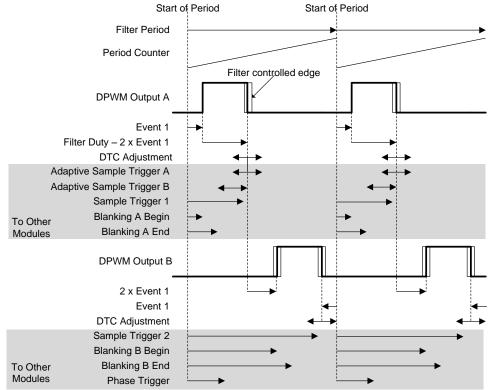

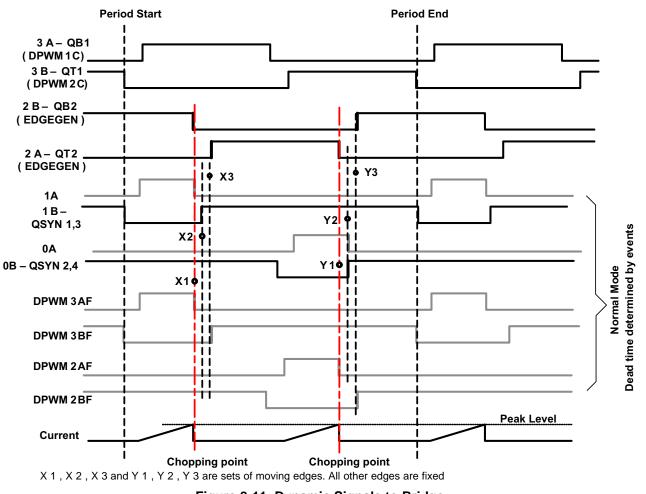

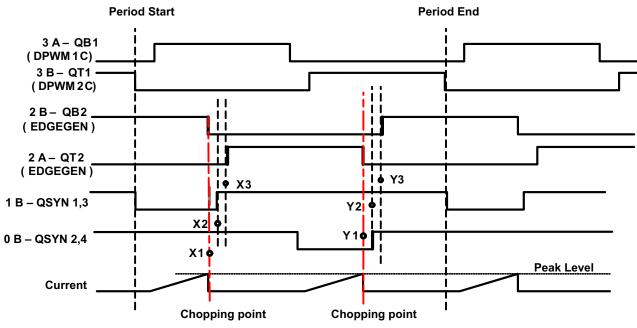

| Changed Figure 7-3 to include DTC Adjustment                                                                                                                                                                                                                                                                                                | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                             | Changed <i>Feature</i> From: "4KB of Boot ROM Enables Firmware Boot-Load" To: "Firmware Boot-Load"<br>Changed Note 2 of the <i>Device Information</i> table From: "for passing IPC9592A Temperature Cycle Qualification"<br>To: "for IPC9592A Temperature Cycle Testing."<br>Changed Figure 5-7<br>Added Figure 6-1<br>Changed Table 7-4 PRIORITY 19 From: CAPTURE_1_INT To: DTC_FLT_INT<br>Changed Figure 7-1 to include DTC Adjustment<br>Changed Figure 7-2 to include DTC Adjustment |

1

1

2

Page

Page

# 3 Device Comparison

# 3.1 Product Selection Matrix

| FEATURE                                                                                                  | UCD3138A 64 PIN<br>(RGC)     | UCD3138A 40 PIN<br>(RMH)     | UCD3138A 40 PIN<br>(RJA)     |

|----------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|

| ARM7TDMI-S core processor                                                                                | 31.25 MHz                    | 31.25 MHz                    | 31.25 MHz                    |

| High resolution DPWM outputs (250-ps resolution)                                                         | 8                            | 8                            | 8                            |

| Number of high speed independent feedback loops (number of regulated output voltages)                    | 3                            | 3                            | 3                            |

| 12-bit, 267-ksps, general-purpose ADC channels                                                           | 14                           | 7                            | 7                            |

| Digital comparators at ADC outputs                                                                       | 4                            | 4                            | 4                            |

| Flash memory (program)                                                                                   | 32 kB                        | 32 kB                        | 32 kB                        |

| Flash memory (data)                                                                                      | 2 kB                         | 2 kB                         | 2 kB                         |

| Flash security                                                                                           | $\checkmark$                 | $\checkmark$                 | $\checkmark$                 |

| RAM                                                                                                      | 4 kB                         | 4 kB                         | 4 kB                         |

| DPWM switching frequency                                                                                 | up to 2 MHz                  | up to 2 MHz                  | up to 2 MHz                  |

| Programmable fault inputs                                                                                | 4                            | 1 + 2                        | 1 + 2                        |

| High speed analog comparators with cycle-by-cycle current limiting                                       | 7 <sup>(1)</sup>             | 6 <sup>(1)</sup>             | 6 <sup>(1)</sup>             |

| UART (SCI)                                                                                               | 2                            | 1                            | 1                            |

| PMBus                                                                                                    | $\checkmark$                 | $\checkmark$                 | $\checkmark$                 |

| Timers                                                                                                   | 4 (16 bit) and<br>1 (24 bit) | 4 (16 bit) and<br>1 (24 bit) | 4 (16 bit) and<br>1 (24 bit) |

| Timer PWM outputs                                                                                        | 2                            | 1                            | 1                            |

| Timer capture inputs                                                                                     | 1                            | 1                            | 1                            |

| Watchdog                                                                                                 | $\checkmark$                 | $\checkmark$                 | $\checkmark$                 |

| On-chip oscillator                                                                                       | $\checkmark$                 | $\checkmark$                 | $\checkmark$                 |

| Power-on reset and brown-out reset                                                                       | $\checkmark$                 | $\checkmark$                 | $\checkmark$                 |

| Package offering                                                                                         | 64 Pin VQFN<br>(9 mm × 9 mm) | 40 Pin WQFN<br>(6 mm × 6 mm) | 40 Pin WQFN<br>(6 mm × 6 mm) |

| Sync IN and sync OUT functions                                                                           | $\checkmark$                 | $\checkmark$                 | $\checkmark$                 |

| Total GPIO (includes all pins with multiplexed functions such as, DPWM, fault inputs, SCI, and so forth) | 30                           | 18                           | 18                           |

| External interruptions                                                                                   | 1                            | 0                            | 0                            |

(1) To facilitate simple OVP and UVP connections both comparators B and C are connected to the AD03 pin.

# 4 Pin Configuration and Functions

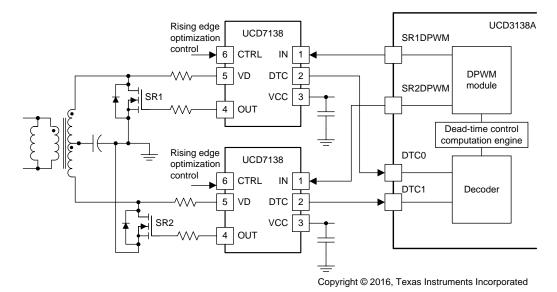

# 4.1 UCD3138A RGC Package

#### UCD3138A RGC Pin Functions

|         | NAME         |                                                                           | ALTERNATE ASSIGNMENT |       |       |       | CONFIGURABLE |

|---------|--------------|---------------------------------------------------------------------------|----------------------|-------|-------|-------|--------------|

| PIN NO. | NAME         | PRIMARY ASSIGNMENT                                                        | NO. 1                | NO. 2 | NO. 3 | NO. 4 | AS A GPIO?   |

| 1       | AGND         | Analog ground                                                             |                      |       |       |       |              |

| 2       | AD13         | 12-bit ADC, Ch 13, comparator E, I-share                                  | DAC output           |       |       |       |              |

| 3       | AD12         | 12-bit ADC, Ch 12                                                         |                      |       |       |       |              |

| 4       | AD10         | 12-bit ADC, Ch 10                                                         |                      |       |       |       |              |

| 5       | AD07         | 12-bit ADC, Ch 7, Connected to comparator F and reference to comparator G | DAC output           |       |       |       |              |

| 6       | AD06         | 12-bit ADC, Ch 6, Connected to comparator F                               | DAC output           |       |       |       |              |

| 7       | AD04         | 12-bit ADC, Ch 4, Connected to comparator D                               | DAC output           |       |       |       |              |

| 8       | AD03         | 12-bit ADC, Ch 3, Connected to comparator B and C                         |                      |       |       |       |              |

| 9       | V33DIO       | Digital I/O 3.3V core supply                                              |                      |       |       |       |              |

| 10      | DGND         | Digital ground                                                            |                      |       |       |       |              |

| 11      | RESET        | Device Reset Input, active low                                            |                      |       |       |       |              |

| 12      | ADC_EXT_TRIG | ADC conversion external trigger input                                     | TCAP                 | SYNC  | PWM0  |       | Yes          |

| 13      | SCI_RX0      | SCI RX 0                                                                  |                      |       |       |       | Yes          |

| 14      | SCI_TX0      | SCI TX 0                                                                  |                      |       |       |       | Yes          |

| 15      | PMBUS_CLK    | PMBUS Clock (Open Drain)                                                  | SCI TX 0             |       |       |       | Yes          |

| 16      | PMBUS_DATA   | PMBus data (Open Drain)                                                   | SCI RX 0             |       |       |       | Yes          |

| 17      | DPWM0A       | DPWM 0A output                                                            |                      |       |       |       | Yes          |

UCD3138A

www.ti.com

| PIN NO. | NAME PRIMARY ASSIGNMENT | ALTERNATE ASSIGNMENT                                                                                |             |              |        | CONFIGURABLE |            |

|---------|-------------------------|-----------------------------------------------------------------------------------------------------|-------------|--------------|--------|--------------|------------|

| PIN NO. | NAME                    | FRIMART ASSIGNMENT                                                                                  | NO. 1       | NO. 2        | NO. 3  | NO. 4        | AS A GPIO? |

| 18      | DPWM0B                  | DPWM 0B output                                                                                      |             |              |        |              | Yes        |

| 19      | DPWM1A                  | DPWM 1A output                                                                                      |             |              |        |              | Yes        |

| 20      | DPWM1B                  | DPWM 1B output                                                                                      |             |              |        |              | Yes        |

| 21      | DPWM2A                  | DPWM 2A output                                                                                      |             |              |        |              | Yes        |

| 22      | DPWM2B                  | DPWM 2B output                                                                                      |             |              |        |              | Yes        |

| 23      | DPWM3A                  | DPWM 3A output                                                                                      |             |              |        |              | Yes        |

| 24      | DPWM3B                  | DPWM 3B output                                                                                      |             |              |        |              | Yes        |

| 25      | DGND                    | Digital ground                                                                                      |             |              |        |              |            |

| 26      | SYNC                    | DPWM Synchronize pin                                                                                | TCAP        | ADC_EXT_TRIG | PWM0   | DTC1         | Yes        |

| 27      | PMBUS_ALERT             | PMBus Alert (Open Drain)                                                                            |             |              |        |              | Yes        |

| 28      | PMBUS_CTRL              | PMBus Control (Open Drain)                                                                          |             |              |        |              | Yes        |

| 29      | SCI_TX1                 | SCI TX 1                                                                                            | PMBUS_ALERT |              |        |              | Yes        |

| 30      | SCI_RX1                 | SCI RX 1                                                                                            | PMBUS_CTRL  |              |        |              | Yes        |

| 31      | PWM0                    | General purpose PWM 0                                                                               |             |              |        |              | Yes        |

| 32      | PWM1                    | General purpose PWM 1                                                                               |             |              |        |              | Yes        |

| 33      | DGND                    | Digital ground                                                                                      |             |              |        |              |            |

| 34      | INT_EXT                 | External Interrupt                                                                                  |             |              |        |              | Yes        |

| 35      | FAULT0                  | External fault input 0                                                                              |             |              |        |              | Yes        |

| 36      | FAULT1                  | External fault input 1                                                                              |             |              |        |              | Yes        |

| 37      | тск                     | JTAG TCK                                                                                            | TCAP        | SYNC         | PWM0   | DTC0         | Yes        |

| 38      | TDO                     | JTAG TDO                                                                                            | SCI_TX0     | PMBUS_ALERT  | FAULT0 | DTC1         | Yes        |

| 39      | TDI                     | JTAG TDI                                                                                            | SCI_RX0     | PMBUS_CTRL   | FAULT1 | DTC0         | Yes        |

| 40      | TMS                     | JTAG TMS                                                                                            |             |              |        |              | Yes        |

| 41      | ТСАР                    | Timer capture input                                                                                 |             |              |        |              | Yes        |

| 42      | FAULT2                  | External fault input 2                                                                              |             |              |        |              | Yes        |

| 43      | FAULT3                  | External fault input 3                                                                              |             |              |        |              | Yes        |

| 44      | DGND                    | Digital ground                                                                                      |             |              |        |              |            |

| 45      | V33DIO                  | Digital I/O 3.3V core supply                                                                        |             |              |        |              |            |

| 46      | BP18                    | 1.8V Bypass                                                                                         |             |              |        |              |            |

| 47      | V33D                    | Digital 3.3V core supply                                                                            |             |              |        |              |            |

| 48      | AGND                    | Substrate analog ground                                                                             |             |              |        |              |            |

| 49      | AGND                    | Analog ground                                                                                       |             |              |        |              |            |

| 50      | EAP0                    | Channel 0, differential analog voltage, positive input                                              |             |              |        |              |            |

| 51      | EAN0                    | Channel 0, differential analog voltage, negative input                                              |             |              |        |              |            |

| 52      | EAP1                    | Channel 1, differential analog voltage, positive input                                              |             |              |        |              |            |

| 53      | EAN1                    | Channel 1, differential analog voltage, negative input                                              |             |              |        |              |            |

| 54      | EAP2                    | Channel 2, differential analog voltage, positive input (Recommended for peak currrent mode control) |             |              |        |              |            |

| 55      | EAN2                    | Channel #2, differential analog voltage, negative input                                             |             |              |        |              |            |

| 56      | AGND                    | Analog ground                                                                                       |             |              |        |              |            |

| 57      | V33A                    | Analog 3.3-V supply                                                                                 |             |              |        |              |            |

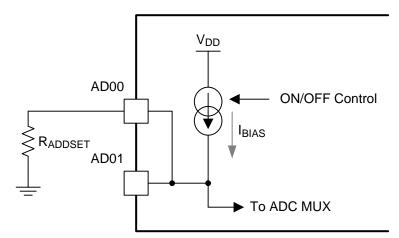

| 58      | AD00                    | 12-bit ADC, Ch 0, Connected to current source                                                       |             |              |        |              |            |

| 59      | AD01                    | 12-bit ADC, Ch 1, Connected to current source                                                       |             |              |        |              |            |

| 60      | AD02                    | 12-bit ADC, Ch 2, Connected to comparator A, I-share                                                |             |              |        |              |            |

| 61      | AD05                    | 12-bit ADC, Ch 5                                                                                    |             |              |        |              |            |

| 62      | AD08                    | 12-bit ADC, Ch 8                                                                                    |             |              |        |              |            |

| 63      | AD09                    | 12-bit ADC, Ch 9                                                                                    |             |              |        |              |            |

| 64      | AD11                    | 12-bit ADC, Ch 11                                                                                   |             |              |        |              |            |

# UCD3138A RGC Pin Functions (continued)

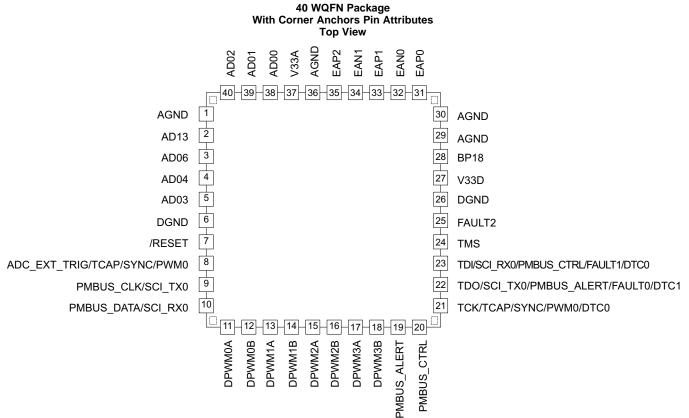

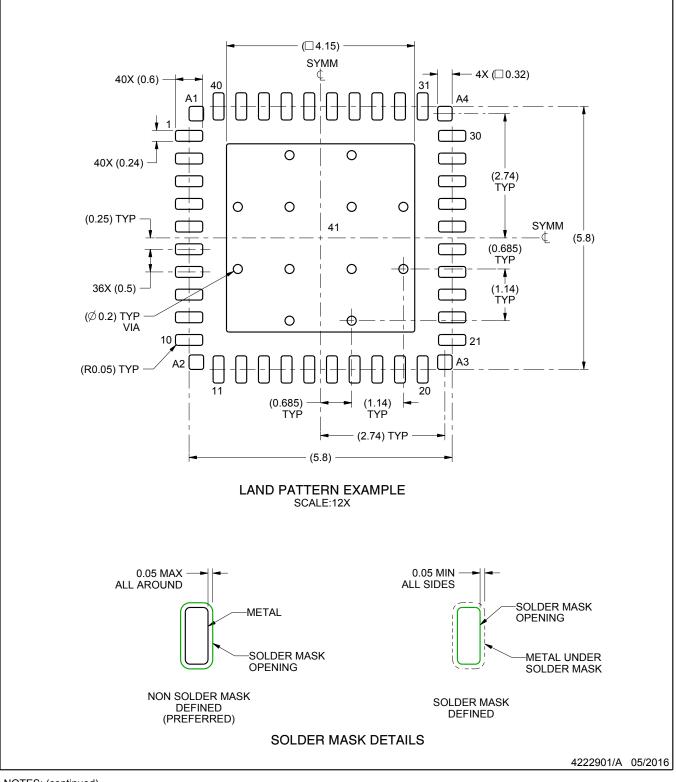

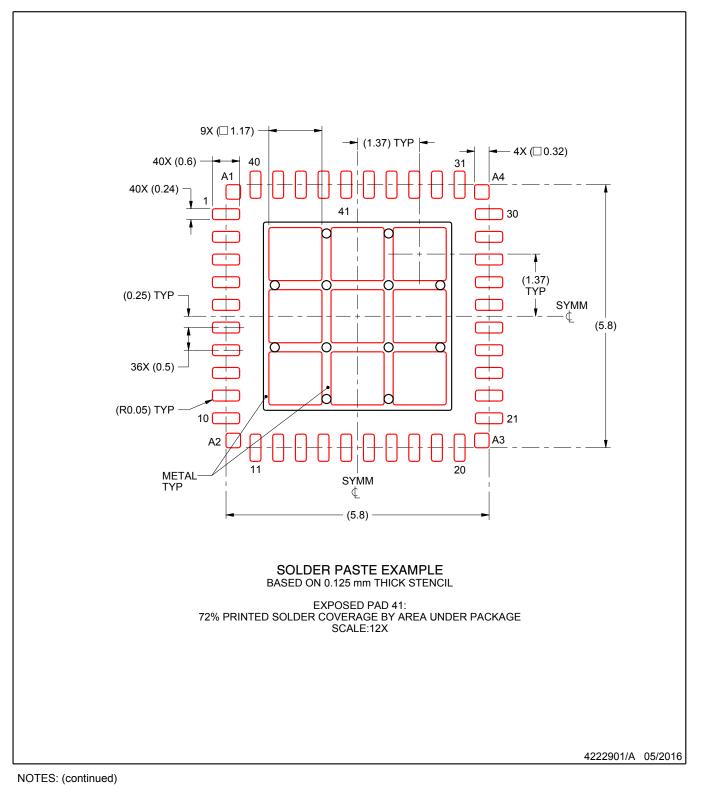

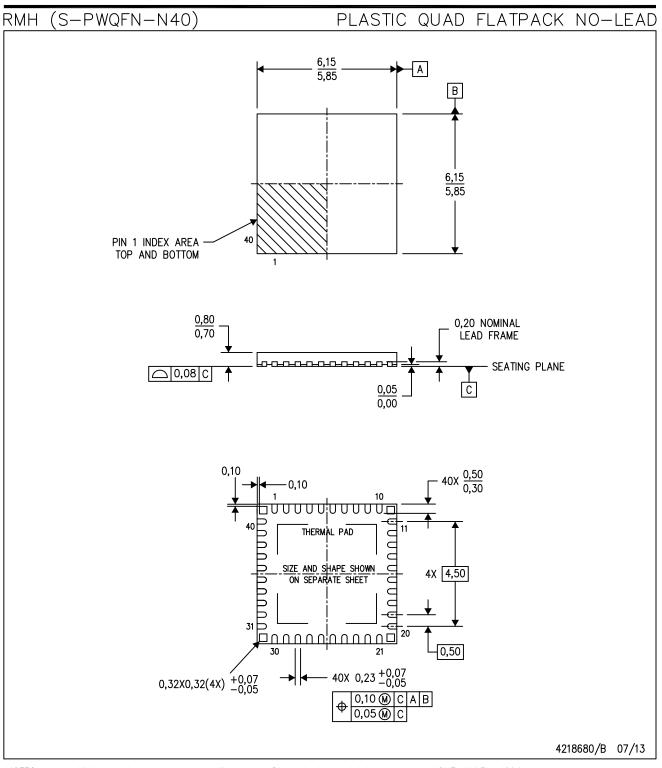

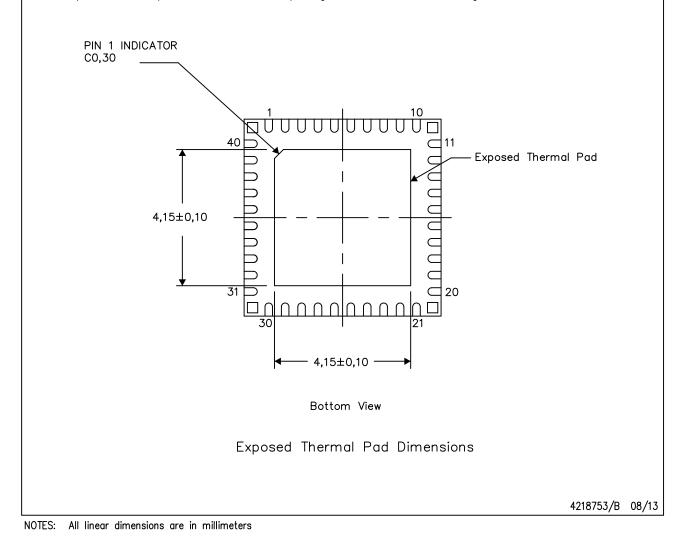

## 4.2 UCD3138A RMH Package

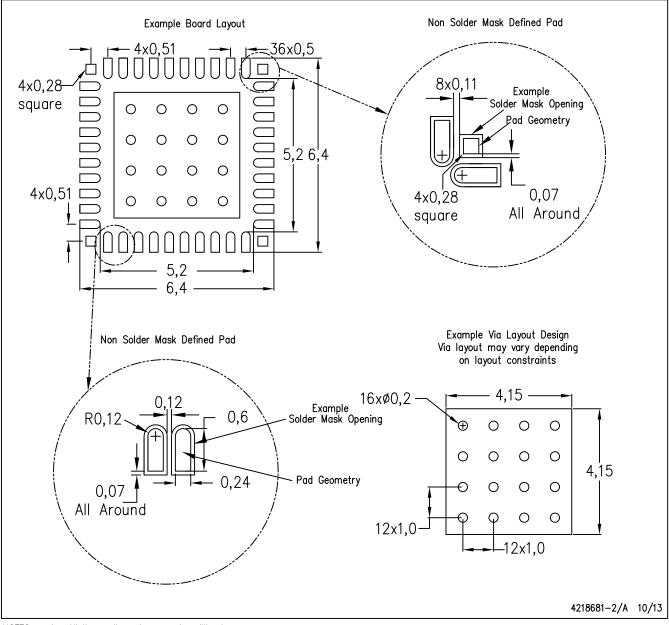

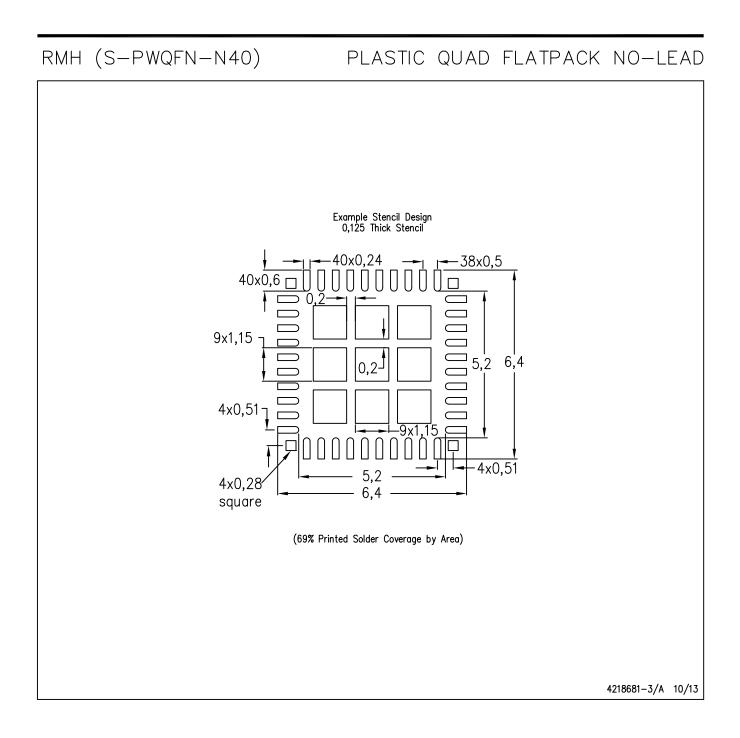

There are four corner pins on the RMH package. The corner anchor pins and thermal pad should be soldered for robust mechanical performance and should be tied to the appropriate ground signal.

#### UCD3138A RMH Pin Functions

|         | NAME         | NAME PRIMARY ASSIGNMENT                               |         | ALTERNATE ASSIGNMENT |        |       |            |

|---------|--------------|-------------------------------------------------------|---------|----------------------|--------|-------|------------|

| PIN NO. |              |                                                       | NO. 1   | NO. 2                | NO. 3  | NO. 4 | AS A GPIO? |

| 1       | AGND         | Analog ground                                         |         |                      |        |       |            |

| 2       | AD13         | 12-bit ADC, Ch 13, Connected to comparator E, I-share |         |                      |        |       |            |

| 3       | AD06         | 12-bit ADC, Ch 6, Connected to comparator F           |         |                      |        |       |            |

| 4       | AD04         | 12-bit ADC, Ch 4, Connected to comparator D           |         |                      |        |       |            |

| 5       | AD03         | 12-bit ADC, Ch 3, Connected to comparator B and C     |         |                      |        |       |            |

| 6       | DGND         | Digital ground                                        |         |                      |        |       |            |

| 7       | RESET        | Device Reset Input, active low                        |         |                      |        |       |            |

| 8       | ADC_EXT_TRIG | ADC conversion external trigger input                 | TCAP    | SYNC                 | PWM0   |       | Yes        |

| 9       | PMBUS_CLK    | PMBUS Clock (Open Drain)                              | SCI_TX0 |                      |        |       | Yes        |

| 10      | PMBUS_DATA   | PMBus data (Open Drain)                               | SCI_RX0 |                      |        |       | Yes        |

| 11      | DPWM0A       | DPWM 0A output                                        |         |                      |        |       | Yes        |

| 12      | DPWM0B       | DPWM 0B output                                        |         |                      |        |       | Yes        |

| 13      | DPWM1A       | DPWM 1A output                                        |         |                      |        |       | Yes        |

| 14      | DPWM1B       | DPWM 1B output                                        |         |                      |        |       | Yes        |

| 15      | DPWM2A       | DPWM 2A output                                        |         |                      |        |       | Yes        |

| 16      | DPWM2B       | DPWM 2B output                                        |         |                      |        |       | Yes        |

| 17      | DWPM3A       | DPWM 3A output                                        |         |                      |        |       | Yes        |

| 18      | DPWM3B       | DPWM 3B output                                        |         |                      |        |       | Yes        |

| 19      | PMBUS_ALERT  | PMBus Alert (Open Drain)                              |         |                      |        |       | Yes        |

| 20      | PMBUS_CTRL   | PMBus Control (Open Drain)                            |         |                      |        |       | Yes        |

| 21      | тск          | JTAG TCK                                              | TCAP    | SYNC                 | PWM0   | DTC0  | Yes        |

| 22      | TDO          | JTAG TDO                                              | SCI_TX0 | PMBUS_ALERT          | FAULT0 | DTC1  | Yes        |

10 Pin Configuration and Functions

Copyright © 2015–2017, Texas Instruments Incorporated

UCD3138A SLUSC66E – MARCH 2015–REVISED FEBRUARY 2017

|                                 | SLUSC66E – MARCH 2015–REVISED FEBRUARY 201 |

|---------------------------------|--------------------------------------------|

|                                 |                                            |

|                                 |                                            |

| UCD3138A RMH Pin Functions (con | itinued)                                   |

| PIN NO.      | NAME                 | PRIMARY ASSIGNMENT                                                                                     | ALTERNATE ASSIGNMENT |            |        |       | CONFIGURABLE |

|--------------|----------------------|--------------------------------------------------------------------------------------------------------|----------------------|------------|--------|-------|--------------|

| i in NO.     | NAME                 | PRIMARTASSIGNMENT                                                                                      | NO. 1                | NO. 2      | NO. 3  | NO. 4 | AS A GPIO?   |

| 23           | TDI                  | JTAG TDI                                                                                               | SCI_RX0              | PMBUS_CTRL | FAULT1 | DTC0  | Yes          |

| 24           | TMS                  | JTAG TMS                                                                                               |                      |            |        |       | Yes          |

| 25           | FAULT2               | External fault input 2                                                                                 |                      |            |        |       | Yes          |

| 26           | DGND                 | Digital ground                                                                                         |                      |            |        |       |              |

| 27           | V33D                 | Digital 3.3V core supply                                                                               |                      |            |        |       |              |

| 28           | BP18                 | 1.8V Bypass                                                                                            |                      |            |        |       |              |

| 29           | AGND                 | Substrate analog ground                                                                                |                      |            |        |       |              |

| 30           | AGND                 | Analog ground                                                                                          |                      |            |        |       |              |

| 31           | EAP0                 | Channel 0, differential analog voltage, positive input                                                 |                      |            |        |       |              |

| 32           | EAN0                 | Channel 0, differential analog voltage, negative input                                                 |                      |            |        |       |              |

| 33           | EAP1                 | Channel 1, differential analog voltage, positive input                                                 |                      |            |        |       |              |

| 34           | EAN1                 | Channel 1, differential analog voltage, negative input                                                 |                      |            |        |       |              |

| 35           | EAP2                 | Channel 2, differential analog voltage, positive input<br>(Recommended for peak currrent mode control) |                      |            |        |       |              |

| 36           | AGND                 | Analog ground                                                                                          |                      |            |        |       |              |

| 37           | V33A                 | Analog 3.3-V supply                                                                                    |                      |            |        |       |              |

| 38           | AD00                 | 12-bit ADC, Ch 0, Connected to current source                                                          |                      |            |        |       |              |

| 39           | AD01                 | 12-bit ADC, Ch 1, Connected to current source                                                          |                      |            |        |       |              |

| 40           | AD02                 | 12-bit ADC, Ch 2, Connected to comparator A, I-share                                                   |                      |            |        |       |              |

| Corner<br>NA | Corner<br>anchor pin | All four anchors should be soldered and tied to GND                                                    |                      |            |        |       |              |

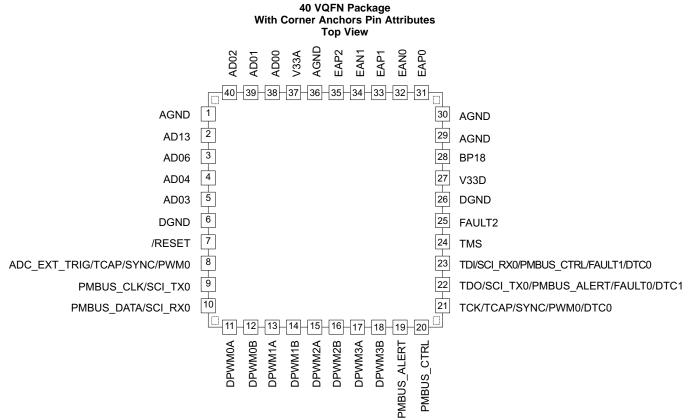

# 4.3 UCD3138A RJA Package

The RJA package has thicker package height compared to the RMH package. There are four corner pins on the RJA package. These features help to improve solder-joint reliability. The corner anchor pins and thermal pad should be soldered for robust mechanical performance and should be tied to the appropriate ground signal.

| PIN NO. | NAME PRIMARY ASSIGNMENT |                                                       | ALTERNATE ASSIGNMENT |       |       |       | CONFIGURABLE |  |

|---------|-------------------------|-------------------------------------------------------|----------------------|-------|-------|-------|--------------|--|

| PIN NO. | NAME                    | FRIMART ASSIGNMENT                                    | NO. 1                | NO. 2 | NO. 3 | NO. 4 | AS A GPIO?   |  |

| 1       | AGND                    | Analog ground                                         |                      |       |       |       |              |  |

| 2       | AD13                    | 12-bit ADC, Ch 13, Connected to comparator E, I-share |                      |       |       |       |              |  |

| 3       | AD06                    | 12-bit ADC, Ch 6, Connected to comparator F           |                      |       |       |       |              |  |

| 4       | AD04                    | 12-bit ADC, Ch 4, Connected to comparator D           |                      |       |       |       |              |  |

| 5       | AD03                    | 12-bit ADC, Ch 3, Connected to comparator B and C     |                      |       |       |       |              |  |

| 6       | DGND                    | Digital ground                                        |                      |       |       |       |              |  |

| 7       | RESET                   | Device Reset Input, active low                        |                      |       |       |       |              |  |

| 8       | ADC_EXT_TRIG            | ADC conversion external trigger input                 | TCAP                 | SYNC  | PWM0  |       | Yes          |  |

| 9       | PMBUS_CLK               | PMBUS Clock (Open Drain)                              | SCI_TX0              |       |       |       | Yes          |  |

| 10      | PMBUS_DATA              | PMBus data (Open Drain)                               | SCI_RX0              |       |       |       | Yes          |  |

| 11      | DPWM0A                  | DPWM 0A output                                        |                      |       |       |       | Yes          |  |

| 12      | DPWM0B                  | DPWM 0B output                                        |                      |       |       |       | Yes          |  |

| 13      | DPWM1A                  | DPWM 1A output                                        |                      |       |       |       | Yes          |  |

| 14      | DPWM1B                  | DPWM 1B output                                        |                      |       |       |       | Yes          |  |

| 15      | DPWM2A                  | DPWM 2A output                                        |                      |       |       |       | Yes          |  |

| 16      | DPWM2B                  | DPWM 2B output                                        |                      |       |       |       | Yes          |  |

| 17      | DWPM3A                  | DPWM 3A output                                        |                      |       |       |       | Yes          |  |

| 18      | DPWM3B                  | DPWM 3B output                                        |                      |       |       |       | Yes          |  |

| 19      | PMBUS_ALERT             | PMBus Alert (Open Drain)                              |                      |       |       |       | Yes          |  |

| 20      | PMBUS_CTRL              | PMBus Control (Open Drain)                            |                      |       |       |       | Yes          |  |

| 21      | тск                     | JTAG TCK                                              | TCAP                 | SYNC  | PWM0  | DTC0  | Yes          |  |

#### UCD3138A RJA Pin Functions

12 Pin Configuration and Functions

Submit Documentation Feedback Product Folder Links: UCD3138A Copyright © 2015-2017, Texas Instruments Incorporated

www.ti.com

Corner NA Corner

anchor pin

ALTERNATE ASSIGNMENT CONFIGURABLE AS A GPIO? NAME PIN NO. PRIMARY ASSIGNMENT NO. 1 NO. 2 NO. 3 NO. 4 TDO JTAG TDO SCI\_TX0 PMBUS\_ALERT FAULT0 DTC1 Yes 22 JTAG TDI SCI\_RX0 PMBUS\_CTRL FAULT1 DTC0 TDI Yes 23 JTAG TMS 24 TMS Yes 25 FAULT2 External fault input 2 Yes DGND 26 Digital ground V33D Digital 3.3V core supply 27 BP18 1.8V Bypass 28 29 AGND Substrate analog ground AGND 30 Analog ground EAP0 Channel 0, differential analog voltage, positive input 31 Channel 0, differential analog voltage, negative input 32 EAN0 33 EAP1 Channel 1, differential analog voltage, positive input 34 EAN1 Channel 1, differential analog voltage, negative input Channel 2, differential analog voltage, positive input (Recommended for peak currrent mode control) 35 EAP2 AGND 36 Analog ground 37 V33A Analog 3.3-V supply 38 AD00 12-bit ADC, Ch 0, Connected to current source 39 AD01 12-bit ADC, Ch 1, Connected to current source AD02 40 12-bit ADC, Ch 2, Connected to comparator A, I-share

All four anchors should be soldered and tied to GND

#### UCD3138A RJA Pin Functions (continued)

# 5 Specifications

#### 5.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                      |                                         | N | lin | MAX | UNIT |

|--------------------------------------|-----------------------------------------|---|-----|-----|------|

|                                      | V33D to DGND                            | - | 0.3 | 3.8 | V    |

|                                      | V33DIO to DGND                          | - | 0.3 | 3.8 | V    |

| land to alter an                     | V33A to AGND                            | - | 0.3 | 3.8 | V    |

| Input voltage                        | BP18 to DGND                            | - | 0.3 | 2.5 | V    |

|                                      | Ground difference,  DGND – AGND         |   |     | 0.3 | V    |

|                                      | Applied to all pins, excluding AGND (2) | - | 0.3 | 3.8 | V    |

| Junction temperature, T <sub>J</sub> |                                         | - | 40  | 150 | °C   |

| Storage temperatu                    | temperature, T <sub>stg</sub> -55 150   |   | 150 | °C  |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Referenced to DGND

## 5.2 ESD Ratings

|                              |                                                                                |                                                                   | VALUE | UNIT     |

|------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|----------|

| V                            | Electrostatic                                                                  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | <b>N</b> |

| V <sub>(ESD)</sub> discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500                                                              | V     |          |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     |                      | MIN | NOM | MAX | UNIT |

|---------------------|----------------------|-----|-----|-----|------|

| V <sub>V33D</sub>   | Digital power        | 3   | 3.3 | 3.6 | V    |

| V <sub>V33DIO</sub> | Digital I/O power    | 3   | 3.3 | 3.6 | V    |

| V <sub>V33A</sub>   | Analog power         | 3   | 3.3 | 3.6 | V    |

| V <sub>BP18</sub>   | 1.8-V digital power  | 1.6 | 1.8 | 2   | V    |

| TJ                  | Junction temperature | -40 |     | 125 | °C   |

#### 5.4 Thermal Information

|                       |                                              |            | UCD3138A   | 3138A      |      |  |  |

|-----------------------|----------------------------------------------|------------|------------|------------|------|--|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | 64 PIN     | 40 PIN     | 40 PIN     | UNIT |  |  |

|                       |                                              | VQFN (RGC) | WQFN (RMH) | VQFN (RJA) |      |  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 25.1       | 31.0       | 30.1       | °C/W |  |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 10.5       | 16.5       | 13.5       | °C/W |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 4.6        | 6.3        | 4.9        | °C/W |  |  |

| ΨJT                   | Junction-to-top characterization parameter   | 0.2        | 0.2        | 0.2        | °C/W |  |  |

| ΨJB                   | Junction-to-board characterization parameter | 4.6        | 6.3        | 4.8        | °C/W |  |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.2        | 1.1        | 0.7        | °C/W |  |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report,

www.ti.com

# 5.5 Electrical Characteristics

$3 V \le V_{V33A} = V_{V33D} = V_{V33DIO} \le to 3.6 V$ , 1  $\mu$ F of capacitance from BP18 to DGND,  $-40^{\circ}C \le T_{J} \le 125^{\circ}C$  (unless otherwise noted)

|                    | PARAMETER                                | TEST CONDITION                                                                                 | MIN    | TYP   | MAX   | UNIT |

|--------------------|------------------------------------------|------------------------------------------------------------------------------------------------|--------|-------|-------|------|

| SUPPLY             | CURRENT                                  |                                                                                                |        |       |       |      |

| I <sub>I33A</sub>  | Analog 3.3-V supply current              | Measured on V33A. The device is<br>powered up but all ADC12 and EADC<br>sampling is disabled   |        | 6.3   |       | mA   |

| I <sub>33DIO</sub> | Digital I/O 3.3-V core supply current    | All GPIO and communication pins are open                                                       |        | 0.35  |       | mA   |

|                    | Digital I/O 3.3-V core supply current    | ROM program execution                                                                          |        | 60    |       | mA   |

| I <sub>33D</sub>   | Digital I/O 3.3-V core supply current    | Flash programming in ROM mode                                                                  |        |       | 70    | mA   |

| l <sub>33</sub>    | Total supply current                     | Operating in ROM mode with all<br>DPWMs enabled and switching at 2<br>MHz. DPWMs all unloaded. |        |       | 105   | mA   |

| ERROR              | ADC INPUTS EAP, EAN                      |                                                                                                |        |       |       |      |

|                    | EAP – AGND                               |                                                                                                | -0.15  |       | 1.998 | V    |

|                    | EAP – EAN                                |                                                                                                | -0.256 |       | 1.848 | V    |

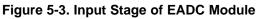

|                    | Typical error range                      | AFE = 0                                                                                        | -256   |       | 248   | mV   |

|                    |                                          | AFE = 3                                                                                        | 0.8    | 1     | 1.20  |      |

|                    | EAP – EAN Error voltage digital          | AFE = 2                                                                                        | 1.7    | 2     | 2.30  |      |

|                    | resolution                               | AFE = 1                                                                                        | 3.55   | 4     | 4.45  | mV   |

|                    |                                          | AFE = 0                                                                                        | 6.90   | 8     | 9.10  |      |

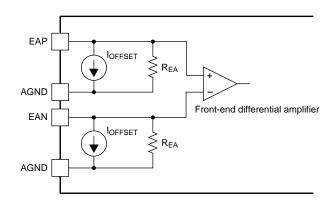

| R <sub>EA</sub>    | Input impedance (See Figure 5-3)         | AGND reference                                                                                 | 0.5    |       |       | MΩ   |

| OFFSET             | Input offset current (See Figure 5-3)    |                                                                                                | -5     |       | 5     | μA   |

|                    |                                          | Input voltage = 0 V at AFE = 0                                                                 | -2     |       | 2     |      |

|                    |                                          | Input voltage = 0 V at AFE = 1                                                                 | -2.5   |       | 2.5   |      |

|                    | EADC offset                              | Input voltage = 0 V at AFE = 2                                                                 | -3     |       | -3    | LSB  |

|                    |                                          | Input voltage = 0 V at AFE = 3                                                                 | -4     |       | 4     |      |

|                    | Sample rate                              |                                                                                                |        |       | 16    | MHz  |

|                    | Analog front end amplifier bandwidth     |                                                                                                |        | 100   |       | MHz  |

| •                  | Gain                                     | See Figure 5-4                                                                                 |        | 1     |       | V/V  |

| ۹ <sub>0</sub>     | Minimum output voltage                   |                                                                                                |        |       | 30    | mV   |

| EADC D             | AC                                       | •                                                                                              |        |       |       |      |

|                    | DAC range                                |                                                                                                | 0      |       | 1.6   | V    |

|                    | VREF DAC reference resolution            | 10 bit, No dithering enabled                                                                   |        | 1.56  |       | mV   |

|                    | VREF DAC reference resolution            | With 4 bit dithering enabled                                                                   |        | 97.6  |       | μV   |

|                    | INL                                      |                                                                                                | -3.0   |       | 3.0   | LSB  |

|                    | DNL                                      | Does not include MSB transition                                                                | -2.1   |       | 1.6   | LSB  |

|                    | DNL at MSB transition                    |                                                                                                |        | -1.4  |       | LSB  |

|                    | DAC reference voltage                    |                                                                                                | 1.58   |       | 1.61  | V    |

| τ                  | Settling time                            | From 10% to 90%                                                                                |        | 250   |       | ns   |

| ADC12              |                                          |                                                                                                |        |       |       |      |

| BIAS               | Bias current for PMBus address pins      |                                                                                                | 9.5    |       | 10.5  | μA   |

|                    | Measurement range for voltage monitoring |                                                                                                | 0      |       | 2.5   | V    |

|                    | Internal ADC reference voltage           |                                                                                                | 2.475  | 2.500 | 2.525 | V    |

|                    | Change in Internal ADC reference from    | $-40^{\circ}C \le T_{A} \le 25^{\circ}C$                                                       |        | -1.2  |       | .,   |

|                    | 25°C reference voltage <sup>(1)</sup>    | $25^{\circ}C \le T_A \le 125^{\circ}C$                                                         |        | -2.6  |       | mV   |

(1) Specified by design. Not production tested.

# **Electrical Characteristics (continued)**

$3 \text{ V} \le \text{V}_{\text{V33A}} = \text{V}_{\text{V33DIO}} \le \text{to } 3.6 \text{ V}, 1 \mu\text{F}$  of capacitance from BP18 to DGND,  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$  (unless otherwise noted)

|                      | PARAMETER                                                                  | TEST CONDITION                                    | MIN             | TYP       | MAX            | UNIT   |

|----------------------|----------------------------------------------------------------------------|---------------------------------------------------|-----------------|-----------|----------------|--------|

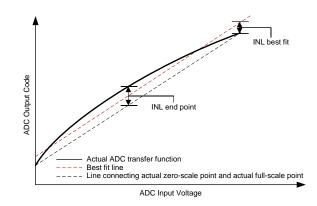

|                      | ADC12 INL integral nonlinearity, end point <sup>(2)</sup> (See Figure 6-1) |                                                   | -3.9            | ±2        | 4.5            | LSB    |

|                      | ADC12 INL integral nonlinearity, best fit <sup>(2)</sup> (See Figure 6-1)  | ADC_SAMPLINGSEL = 0 to 6 for all                  | -2.3            | ±1.5      | 2.6            | LSB    |

|                      | ADC12 DNL differential nonlinearity <sup>(2)</sup>                         | ADC12 data                                        | -               | -0.8/+2.4 |                | LSB    |

|                      | ADC Zero Scale Error                                                       |                                                   | -7              |           | 7              | mV     |

|                      | ADC Full Scale Error                                                       |                                                   | -35             |           | 35             | mV     |

|                      | Input bias                                                                 | V <sub>ADC12</sub> = 2.5 V                        |                 |           | 400            | nA     |

|                      | Input leakage resistance <sup>(1)</sup>                                    | ADC_SAMPLINGSEL = 0 or<br>ADC_SAMPLINGSEL = 6     |                 | 1         |                | MΩ     |

|                      | Input Capacitance <sup>(1)</sup>                                           |                                                   |                 | 10        |                | pF     |

|                      | ADC single sample conversion time <sup>(1)</sup>                           | ADC_SAMPLINGSEL = 0 or<br>ADC_SAMPLINGSEL = 6     |                 | 3.9       |                | μS     |

| DIGITAL              | - INPUTS/OUTPUTS <sup>(3)(4)</sup>                                         |                                                   | •               |           | ,              |        |

| V <sub>OL</sub>      | Low-level output voltage <sup>(5)</sup>                                    | I <sub>OH</sub> = 4 mA, V <sub>V33DIO</sub> = 3 V |                 |           | DGND<br>+ 0.25 | V      |

| V <sub>OH</sub>      | High-level output voltage <sup>(5)</sup>                                   | $I_{OH} = -4$ mA, $V_{V33DIO} = 3$ V              | V33DIO<br>- 0.6 |           |                | V      |

| VIH                  | High-level input voltage                                                   | V <sub>V33DIO</sub> = 3 V                         | 2.1             |           |                | V      |

| V <sub>IL</sub>      | Low-level input voltage                                                    | V <sub>V33DIO</sub> = 3 V                         |                 |           | 1.1            | V      |

| I <sub>OH</sub>      | Output sinking current                                                     |                                                   |                 |           | 4              | mA     |

| I <sub>OL</sub>      | Output sourcing current                                                    |                                                   | -4              |           |                | mA     |

| SYSTEM               | I PERFORMANCE                                                              |                                                   |                 |           |                |        |

| TWD                  | Watchdog time out range                                                    | Total time is: TWD ×<br>(WDCTRL.PERIOD + 1)       | 14.6            | 17        | 20.5           | ms     |

|                      | Time to disable DPWM output based on active FAULT pin signal               | High level on FAULT pin                           |                 | 70        |                | ns     |

|                      | Processor master clock (MCLK)                                              |                                                   |                 | 31.25     |                | MHz    |

| t <sub>Delay</sub>   | Digital compensator delay <sup>(6)</sup>                                   | (1 clock = 32 ns)                                 |                 |           | 6              | clocks |

| t <sub>(reset)</sub> | Pulse width needed at reset <sup>(1)</sup>                                 |                                                   | 10              |           |                | μs     |

|                      | Retention period of flash content (data retention and program)             | $T_J = 25^{\circ}C$                               | 100             |           |                | years  |

|                      | Program time to erase one page or<br>block in data flash or program flash  |                                                   |                 | 20        |                | ms     |

|                      | Program time to write one word in data flash or program flash              |                                                   |                 | 20        |                | μs     |

| 4                    | Internal appillator fragmany                                               | -40°C to +125°C                                   | 240             | 250       | 260            | MHz    |

| f <sub>(PCLK)</sub>  | Internal oscillator frequency                                              | –5°C to +85°C                                     | 245             | 250       | 255            | MHz    |

|                      | Sync-in or sync-out pulse width                                            | SYNC pin                                          |                 | 256       |                | ns     |

|                      | Flash read                                                                 |                                                   |                 | 1         |                | MCLKs  |

|                      | Flash rrite                                                                |                                                   |                 | 20        |                | μs     |

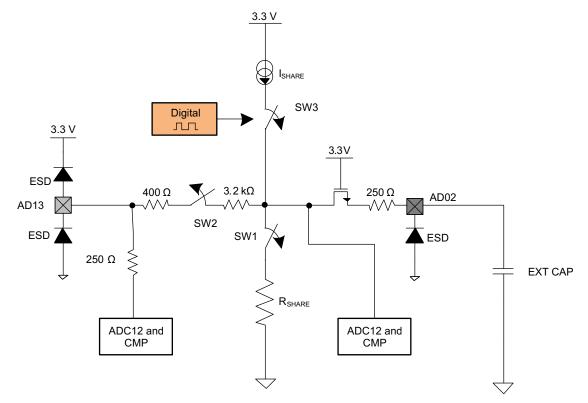

| I <sub>SHARE</sub>   | Current share current source (See Figure 7-16)                             |                                                   | 238             |           | 259            | μΑ     |

(2) Minimum and maximum values are specified by design and characterization data.

- (3) DPWM outputs are low after reset. Other GPIO pins are configured as inputs after reset.

- (4) On the 40-pin package V33DIO is connected to V33D internally.

(6) Time from close of error ADC sample window to time when digitally calculated control effort (duty cycle) is available. This delay, which has no variation associated with it, must be accounted for when calculating the system dynamic response.

<sup>(5)</sup> The maximum total current, I<sub>OH(max)</sub> and I<sub>OL(max)</sub> for all outputs combined, should not exceed 12 mA to hold the maximum voltage drop specified. Maximum sink current per pin = -6 mA at V<sub>OL</sub>; maximum source current per pin = 6 mA at V<sub>OH</sub>.

# **Electrical Characteristics (continued)**

$3 \text{ V} \le \text{V}_{\text{V33A}} = \text{V}_{\text{V33DIO}} \le \text{to } 3.6 \text{ V}, 1 \mu\text{F}$  of capacitance from BP18 to DGND,  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER          |                                              | TEST CONDITION | MIN  | TYP MAX | UNIT |

|--------------------|----------------------------------------------|----------------|------|---------|------|

| R <sub>SHARE</sub> | Current share resistor (See Figure 7-<br>16) |                | 9.75 | 10.3    | kΩ   |

# **Electrical Characteristics (continued)**

$3 \text{ V} \le \text{V}_{\text{V33A}} = \text{V}_{\text{V33D}} = \text{V}_{\text{V33DIO}} \le \text{to } 3.6 \text{ V}, 1 \mu\text{F} \text{ of capacitance from BP18 to DGND}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$  (unless otherwise noted)

|                   | PARAMETER                                                                                             | TEST CONDITION                                 | MIN   | TYP    | MAX   | UNIT   |

|-------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------|-------|--------|-------|--------|

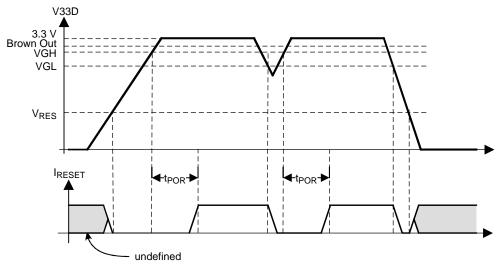

| POWER             | ON RESET AND BROWN OUT (V33D pin                                                                      | , See Figure 6-2)                              |       |        |       |        |

| VGH               | Voltage good high                                                                                     |                                                |       | 2.7    |       | V      |

| VGL               | Voltage good low                                                                                      |                                                |       | 2.5    |       | V      |

| V <sub>res</sub>  | Voltage at which IRESET signal is valid                                                               |                                                |       | 0.8    |       | V      |

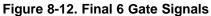

| t <sub>POR</sub>  | Time delay after power is good or<br>RESET relinquished                                               |                                                |       | 1      |       | ms     |