# Precision, Low Drift 4-20mA TWO-WIRE TRANSMITTER

# **FEATURES**

- INSTRUMENTATION AMPLIFIER INPUT:

- Low Offset Voltage, 30 $\mu$ V max

- Low Voltage Drift, 0.75 $\mu\text{V}\text{/}^{\circ}\text{C}$  max

- Low Nonlinearity, 0.01% max

- TRUE TWO-WIRE OPERATION:

- Power and Signal on One Wire Pair

- Current Mode Signal Transmission

- High Noise Immunity

- DUAL MATCHED CURRENT SOURCES

- WIDE SUPPLY RANGE: 11.6V to 40V

- SPECIFICATION RANGE: -40°C to +85°C

- SMALL DIP-14 PACKAGE, CERAMIC AND PLASTIC

# APPLICATIONS

- INDUSTRIAL PROCESS CONTROL:

- Pressure Transmitters

- Temperature Transmitters

- Millivolt Transmitters

- **RESISTANCE BRIDGE INPUTS**

- THERMOCOUPLE INPUTS

- RTD INPUTS

- CURRENT SHUNT (mV) INPUTS

- PRECISION DUAL CURRENT SOURCES

- AUTOMATED MANUFACTURING

- POWER/PLANT ENERGY SYSTEM MONITORING

# DESCRIPTION

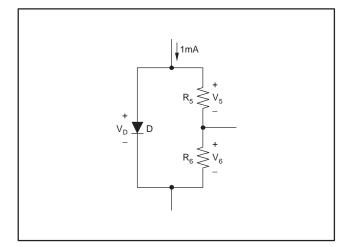

The XTR101 is a microcircuit, 4-20mA, two-wire transmitter containing a high accuracy instrumentation amplifier (IA), a voltage-controlled output current source, and dual-matched precision current reference. This combination is ideally suited for remote signal conditioning of a wide variety of transducers such as thermocouples, RTDs, thermistors, and strain gauge bridges. State-of-the-art design and laser-trimming, wide temperature range operation, and small size make it very suitable for industrial process control applications. In addition, the optional external transistor allows even higher precision.

The two-wire transmitter allows signal and power to be supplied on a single wire pair by modulating the power-supply current with the input signal source. The transmitter is immune to voltage drops from long runs and noise from motors, relays, actuators, switches, transformers, and industrial equipment. It can be used by OEMs producing transmitter modules or by data acquisition system manufacturers.

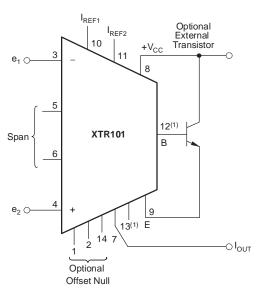

NOTE: (1) Pins 12 and 13 are used for optional BW control.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Power Supply, +V <sub>CC</sub>                                                |

|-------------------------------------------------------------------------------|

| Input Voltage, $e_1$ or $e_2$ $\geq V_{OUT}$ , $\leq +V_{CC}$                 |

| Storage Temperature Range, Ceramic55°C to +165°C                              |

| Plastic55°C to +125°C                                                         |

| Lead Temperature (soldering, 10s) G, P+300°C                                  |

| (wave soldering, 3s) U+260°C                                                  |

| Output Short-Circuit Duration Continuous +V <sub>CC</sub> to I <sub>OUT</sub> |

| Junction Temperature+165°C                                                    |

| (4)                                                                           |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **ORDERING INFORMATION**

| PRODUCT | PACKAGE-<br>LEAD  | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING |

|---------|-------------------|--------------------------------------|-----------------------------------|--------------------|

|         | Ceramic           | JD                                   |                                   | XTR101AG           |

|         | DIP-14            | JD                                   |                                   | XTR101BG           |

| XTR101  | Plastic<br>DIP-14 | Ν                                    | -40°C to +85°C                    | XTR101AP           |

|         | SO-16             | DW                                   |                                   | XTR101AU           |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet.

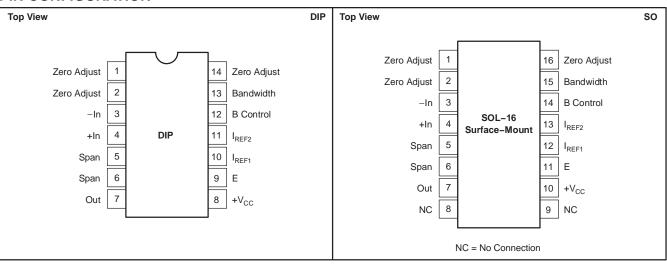

### **PIN CONFIGURATION**

### **ELECTRICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ ,  $+V_{CC} = 24VDC$ , and  $R_L = 100\Omega$  with external transistor connected, unless otherwise noted.

|                                    |                                                                   | )     | (TR101AC   | 3         |              | XTR101E    | 3G        |         | XTR101A    | P                                 | XTR101AU |        |        |            |

|------------------------------------|-------------------------------------------------------------------|-------|------------|-----------|--------------|------------|-----------|---------|------------|-----------------------------------|----------|--------|--------|------------|

| PARAMETER                          | CONDITIONS                                                        | MIN   | TYP        | MAX       | MIN          | TYP        | MAX       | MIN     | TYP        | MAX                               | MIN      | TYP    | MAX    | UNIT       |

| OUTPUT AND LOAD CHAP               |                                                                   |       |            |           |              |            |           |         |            |                                   |          |        |        |            |

| Current                            | Linear Operating Region                                           | 4     |            | 20        | *            |            | *         | *       |            | *                                 | *        |        | *      | mA         |

|                                    | Derated Performance                                               | 3.8   |            | 22        | *            |            | *         | *       |            | *                                 | *        |        | *      | mA         |

| Current Limit                      |                                                                   |       | 28         | 38        |              | *          | *         |         | 31         | *                                 |          | 31     | *      | mA         |

| Offset Current Error               | $I_{OS}, I_{O} = 4mA$                                             |       | ±3.9       | ±10       |              | ±2.5       | ±6        |         | ±8.5       | ±19                               |          | ±8.5   | ±19    | μΑ         |

| vs Temperature                     | ΔΙΟς/ΔΤ                                                           |       | ±10.5      | ±20       |              | ±8         | ±15       |         | ±10.5      | ±20                               |          | *      |        | ppm, FS/°C |

| Full-Scale Output Current<br>Error | Full-Scale = 20mA                                                 |       | ±20        | ±40       |              | ±15        | ±30       |         | ±30        | ±60                               |          | ±30    | ±60    | μА         |

| Power-Supply Voltage               | V <sub>CC</sub> , Pins 7 and 8,<br>Compliance <sup>(1)</sup>      | +11.6 |            | ±40       | *            |            | *         | *       |            | *                                 | *        |        | *      | VDC        |

| Load Resistance                    | At $V_{CC} = +24V$ ,<br>$I_{O} = 20mA$                            |       |            | 600       |              |            | *         |         |            | *                                 |          |        | *      | Ω          |

|                                    | At $V_{CC} = +40V$ ,<br>$I_{O} = 20mA$                            |       |            | 1400      |              |            | *         |         |            | *                                 |          |        | *      | Ω          |

| SPAN                               |                                                                   |       |            |           |              |            |           |         |            |                                   |          |        |        |            |

| Output Current Equation            | $R_S$ in $\Omega,e_1$ and $e_2$ in V                              |       |            |           | $I_{O} = 4n$ |            | )16amps/\ |         |            | e <sub>2</sub> - e <sub>1</sub> ) |          |        |        |            |

| Span Equation                      | $R_S$ in $\Omega$                                                 |       |            |           |              | S = 0      | .016amps, | /volt + | $(40/R_S)$ |                                   |          |        |        | A/V        |

| vs Temperature                     | Excluding TCR of RS                                               |       | ±30        | ±100      |              | *          | *         |         | *          | *                                 |          | *      | *      | ppm/°C     |

| Untrimmed Error <sup>(2)</sup>     | ٤SPAN                                                             | -5    | -2.5       | 0         | *            | *          | *         | *       | *          | *                                 | *        | *      | *      | %          |

| Nonlinearity                       | <sup>E</sup> NONLINEARITY                                         |       |            | 0.01      |              |            | *         |         |            | *                                 |          |        | *      | %          |

| Hysteresis                         | HONEILEART                                                        |       | 0          |           |              | *          |           |         | *          |                                   |          | *      |        | %          |

| Dead Band                          |                                                                   |       | 0          |           |              | *          |           |         | *          |                                   |          | *      |        | %          |

| INPUT CHARACTERISTICS              | 6                                                                 |       |            |           |              |            |           |         |            |                                   |          |        |        |            |

| Impedance: Differential            | 1                                                                 |       | 0.4    3   |           |              | *          |           |         | *          |                                   |          | *      |        | GΩ   pF    |

| Common-Mode                        |                                                                   |       | 10    3    |           |              | *          |           |         | *          |                                   |          | *      |        | GΩ   pF    |

| Voltage Range, Full-Scale          | $\Delta e = (e_2 - e_1)^{(3)}$                                    | 0     |            | 1         | *            |            | *         | *       |            | *                                 | *        |        | *      | V          |

| Offset Voltage                     | Vos                                                               |       | ±30        | ±60       |              | ±20        | ±30       |         | *          | ±100                              |          | *      | ±100   | μV         |

| vs Temperature                     | $\Delta V_{OS} / \Delta T$                                        |       | ±0.75      | ±1.5      |              | ±0.35      | ±0.75     |         | *          | *                                 |          | *      | *      | μV/°C      |

| Power-Supply Rejection             | ∆V <sub>CC</sub> /PSRR = V <sub>OS</sub> Error                    | 110   | 125        |           | *            | *          |           | *       | 122        |                                   | *        | 122    |        | dB         |

| Bias Current                       | IB                                                                |       | 60         | 150       |              | *          | *         |         | *          | *                                 |          | *      | *      | nA         |

| vs Temperature                     | ΔΙΒ/ΔΤ                                                            |       | 0.30       | 1         |              | *          | *         |         | *          | *                                 |          | *      | *      | nA/°C      |

| Offset Current                     | IOSI                                                              |       | 10         | ±30       |              | *          | ±20       |         | *          | *                                 |          | *      | *      | nA         |

| vs Temperature                     | ΔI <sub>OSI</sub> /ΔT                                             |       | 0.1        | 0.3       |              | *          | *         |         | *          | *                                 |          | *      | *      | nA/°C      |

| Common-Mode<br>Rejection(4)        | DC                                                                | 90    | 100        |           | *            | *          |           | *       | *          |                                   | *        | *      |        | dB         |

| Common-Mode Range                  | e1 and e2 with Respect to Pin 7                                   | 4     |            | 6         | *            |            | *         | *       |            | *                                 | *        |        | *      | V          |

| CURRENT SOURCES                    |                                                                   |       |            |           |              |            |           |         |            |                                   |          |        | 1      |            |

| Magnitude                          |                                                                   |       | 1          |           |              | *          |           |         | *          |                                   |          | *      |        | mA         |

| Accuracy                           | $V_{CC} = 24V,$                                                   |       |            | 10.1      |              | 10.00      |           |         |            |                                   |          |        |        |            |

|                                    | VPIN 8 - VPIN 10, 11 = 19V,<br>R <sub>2</sub> = 5kΩ, see Figure 5 |       | ±0.06      | ±0.1<br>7 |              | ±0.02<br>5 | ±0.075    |         | ±0.2       | ±0.37                             |          | ±0.2   | ±0.37  | %          |

| vs Temperature                     |                                                                   |       | ±50        | ±80       |              | ±30        | ±50       |         | *          | *                                 |          | *      | *      | ppm/°C     |

| vs V <sub>CC</sub>                 |                                                                   |       | ±3         |           |              | *          |           |         | *          |                                   |          | *      |        | ppm/V      |

| vs Time                            |                                                                   |       | ±8         |           |              | *          |           |         | *          |                                   |          | *      |        | ppm/month  |

| Compliance Voltage Ratio<br>Match  | With Respect to<br>Pin 7 Tracking                                 | 0     |            | C – 3.5   | *            |            | *         | *       |            | *                                 | *        |        | *      | V          |

| Accuracy                           | $(1 - I_{REF1}/I_{REF2}) \times 100\%$                            |       | ±0.01<br>4 | ±0.0<br>6 |              | ±0.00<br>9 | ±0.04     |         | ±0.031     | ±0.088                            |          | ±0.031 | ±0.088 | %          |

| vs Temperature                     |                                                                   |       |            | ±15       |              |            | 10        |         |            | *                                 |          |        | *      | ppm/°C     |

| vs VCC                             |                                                                   |       | ±10        |           |              | *          |           |         | *          |                                   |          | *      |        | ppm/V      |

| vs Time                            |                                                                   |       | ±10        |           |              | *          |           |         | *          |                                   |          | *      |        | ppm/month  |

| Output Impedance                   |                                                                   | 10    | 20         |           | *            | *          |           | *       | 15         |                                   | *        | 15     |        | MΩ         |

| TEMPERATURE RANGE                  |                                                                   |       |            |           |              |            |           |         |            |                                   |          |        |        |            |

| Specification                      |                                                                   | -40   |            | +85       | *            |            | *         | *       |            | *                                 | *        |        | *      | °C         |

| Operating                          |                                                                   | -55   |            | +125      | *            |            | *         | -40     |            | +85                               | -40      |        | +85    | °C         |

|                                    |                                                                   |       |            |           | *            |            | *         |         |            |                                   |          |        |        |            |

\* Same as XTR101AG.

A Same as XTR101AG.

(1) See the Typical Characteristics.

(2) Span error shown is untrimmed and may be adjusted to zero.

(3) eq and e₂ are signals on the -In and +In terminals with respect to the output, pin 7. While the maximum permissible △e is 1V, it is primarily intended for much lower signal levels, for instance, 10mV or 50mV full-scale for the XTR101A and XTR101B grades, respectively. 2mV FS is also possible with the B grade, but accuracy will degrade due to possible errors in the low value span resistance and very high amplification of offset, drift, and noise.

(4) Offset voltage is trimmed with the application of a 5V common-mode voltage. Thus, the associated common-mode error is removed. See the Application Information section.

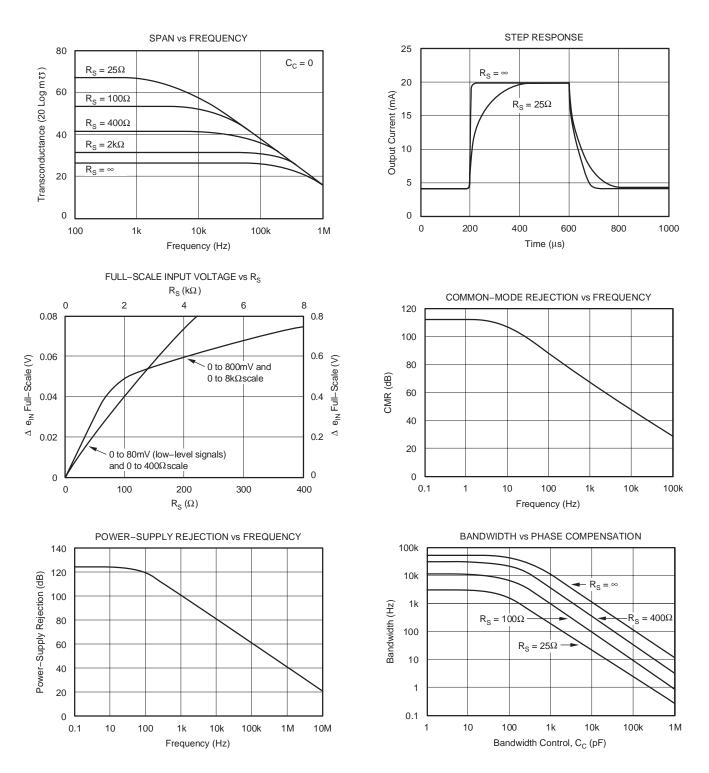

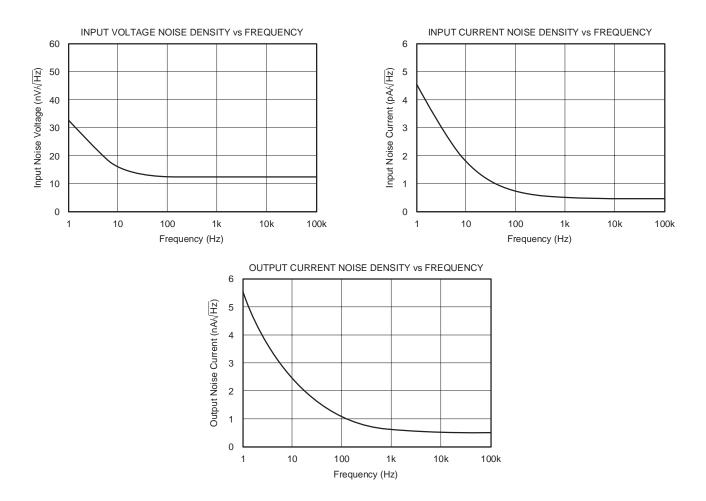

### **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$  and  $V_{CC} = 24VDC$ , unless otherwise noted.

### V TEXAS INSTRUMENTS www.ti.com

### **TYPICAL CHARACTERISTICS (continued)**

At T\_A = +25°C, V\_DD = +3.3V, and V\_IO = +3.3V, unless otherwise noted.

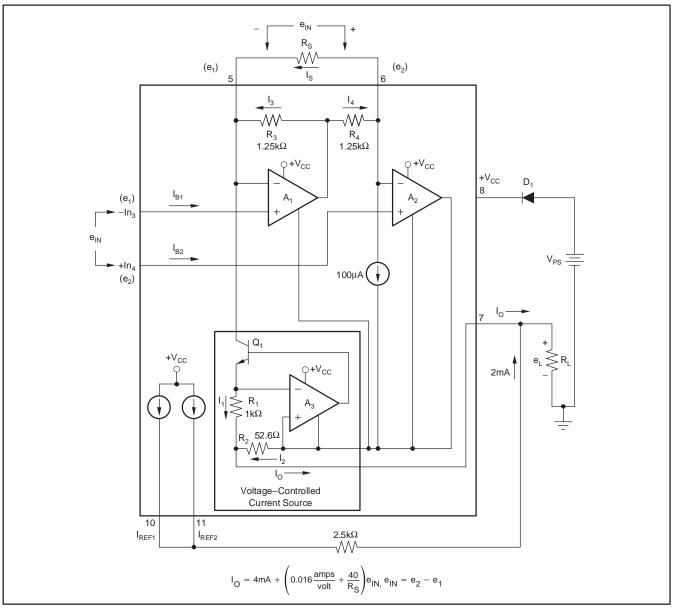

# THEORY OF OPERATION

A simplified schematic of the XTR101 is shown in Figure 1. Basically, the amplifiers A<sub>1</sub> and A<sub>2</sub> act as a single power-supply instrumentation amplifier controlling a current source, A<sub>3</sub> and Q<sub>1</sub>. Operation is determined by an internal feedback loop. e<sub>1</sub> applied to pin 3 will also appear at pin 5, and similarly, e<sub>2</sub> will appear at pin 6. Therefore, the current in R<sub>S</sub> (the span setting resistor) will be I<sub>S</sub> = (e<sub>2</sub> - e<sub>1</sub>)/R<sub>S</sub> = e<sub>IN</sub>/R<sub>S</sub>. This current combines with the current I<sub>3</sub> to form I<sub>1</sub>. The circuit is configured such that I<sub>2</sub> is 19 times I<sub>1</sub>. From this point, the derivation of the transfer function is straightforward but lengthy. The result is shown in Figure 1. Examination of the transfer function shows that  $I_O$  has a lower range-limit of 4mA when  $e_{IN} = e_2 - e_1 = 0V$ . This 4mA is composed of 2mA quiescent current exiting pin 7 plus 2mA from the current sources. The upper range limit of  $I_O$  is set to 20mA by the proper selection of  $R_S$  based on the upper range limit of  $e_{IN}$ . Specifically,  $R_S$  is chosen for a 16mA output current span for the given full-scale input voltage span.

For example,

$$\left(0.016 \frac{\text{amps}}{\text{volt}} + \frac{40}{R_s}\right) (e_{\text{IN}} \text{ full-scale}) = 16 \text{mA}.$$

Note that since  $I_O$  is unipolar,  $e_2$  must be kept larger than  $e_1$  (that is,  $e_2 \ge e_1$  or  $e_{IN} \ge 0$ ). Also note that in order not to exceed the output upper range limit of 20mA,  $e_{IN}$  must be kept less than 1V when  $R_S = \infty$  and proportionately less as  $R_S$  is reduced.

Figure 1. Simplified Schematic of the XTR101

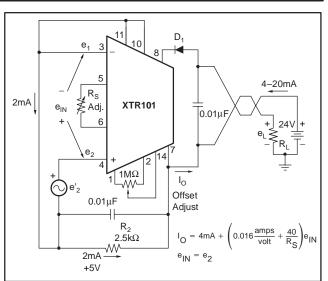

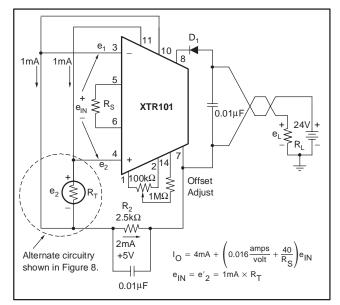

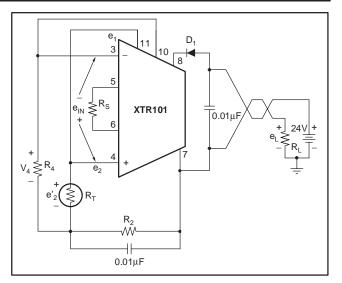

## INSTALLATION AND OPERATING INSTRUCTIONS BASIC CONNECTION

See Figure 1 for the basic connection of the XTR101. A difference voltage applied between input pins 3 and 4 will cause a current of 4-20mA to circulate in the two-wire output loop (through R<sub>L</sub>, V<sub>PS</sub>, and D<sub>1</sub>). For applications requiring moderate accuracy, the XTR101 operates very cost-effectively with just its internal drive transistor. For more demanding applications (high accuracy in high gain), an external NPN transistor can be added in parallel with the internal one. This keeps the heat out of the XTR101 package and minimizes thermal feedback to the input stage. Also, in such applications where the  $e_{\rm IN}$  full-scale is small (< 50mV) and  $R_{\rm SPAN}$  is small (< 150 $\Omega$ ), caution should be taken to consider errors from the external span circuit plus high amplification of offset drift and noise.

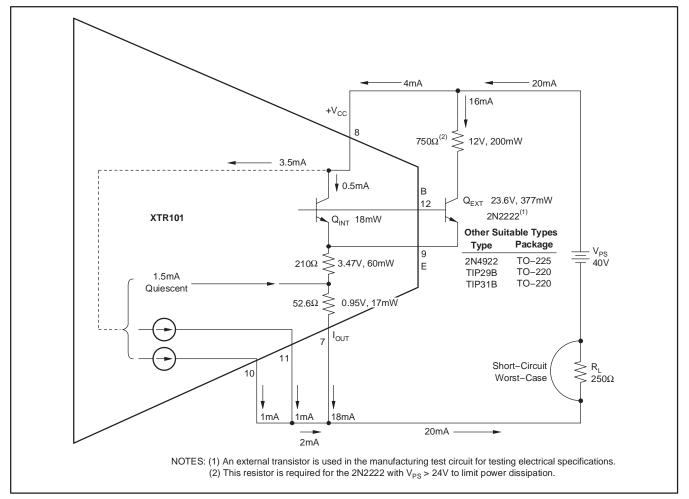

### **OPTIONAL EXTERNAL TRANSISTOR**

The optional external transistor, when used, is connected in parallel with the XTR101 internal transistor. The purpose is to increase accuracy by reducing heat change inside the XTR101 package as the output current spans from 4-20mA. Under normal operating conditions, the internal transistor is never completely turned off, as shown in Figure 2. This maintains frequency stability with varying external transistor characteristics and wiring capacitance. The actual current sharing between internal and external transistors is dependent on two factors:

- 1. relative geometry of emitter areas, and

- 2. relative package dissipation (case size and thermal conductivity).

For best results, the external device should have a larger base-emitter area and smaller package. It will, upon turn-on, take about  $[0.95(I_O - 3.3mA)]mA$ . However, it will heat faster and take a greater share after a few seconds.

Figure 2. Power Calculation of the XTR101 with an External Transistor

Although any NPN of suitable power rating will operate with the XTR101, two readily available transistors are recommended:

- 2N2222 in the TO-18 package. For power-supply voltages above 24V, a 750Ω, 1/2W resistor should be connected in series with the collector. This will limit the power dissipation to 377mW under the worst-case conditions; see Figure 2. Thus, the 2N2222 will safely operate below its 400mW rating at the upper temperature of +85°C. Heat sinking the 2N2222 will result in greatly reduced accuracy improvement and is not recommended.

- TIP29B in the TO-220 package. This transistor will operate over the specified temperature and output voltage range without a series collector resistor. Heat sinking the TIP29B will result in slightly less accuracy improvement. It can be done, however, when mechanical constraints require it.

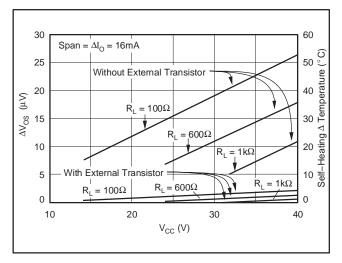

# ACCURACY WITH AND WITHOUT AN EXTERNAL TRANSISTOR

The XTR101 has been tested in a circuit using an external transistor. The relative difference in accuracy with and without an external transistor is shown in Figure 3. Notice that a dramatic improvement in offset voltage change with supply voltage is evident for any value of load resistor.

Figure 3. Thermal Feedback Due to Change in Output Current

# MAJOR POINTS TO CONSIDER WHEN USING THE XTR101

- The leads to R<sub>S</sub> should be kept as short as possible to reduce noise pick-up and parasitic resistance.

- 2.  $+V_{CC}$  should be bypassed with a 0.01µF capacitor as close to the unit as possible (pin 8 to pin 7).

- Always keep the input voltages within their range of linear operation, +4V to +6V (e<sub>1</sub> and e<sub>2</sub> measured with respect to pin 7).

- 4. The maximum input signal level ( $e_{INFS}$ ) is 1V with  $R_S = \infty$  and proportionally less as  $R_S$  decreases.

- 5. Always return the current references (pins 10 and 11) to the output (pin 7) through an appropriate resistor. If the references are not used for biasing or excitation, connect them together to pin 7. Each reference must have between 0V and  $+(V_{CC} 4V)$  with respect to pin 7.

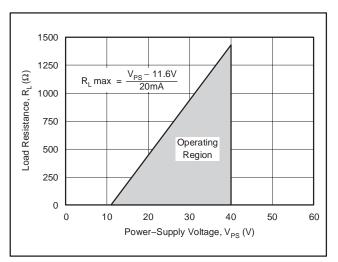

- Always choose R<sub>L</sub> (including line resistance) so that the voltage between pins 7 and 8 (+V<sub>CC</sub>) remains within the 11.6V to 40V range as the output changes between the 4-20mA range (as shown in Figure 4).

- 7. It is recommended that a reverse polarity protection diode ( $D_1$  in Figure 1) be used. This will prevent damage to the XTR101 caused by a momentary (such as a transient) or long-term application of the wrong polarity of voltage between pins 7 and 8.

- 8. Consider PC board layout which minimizes parasitic capacitance, especially in high gain.

Figure 4. Power-Supply Operating Range

### SELECTING THE RS

$R_{SPAN}$  is chosen so that a given full-scale input span (e\_{INFS}) will result in the desired full-scale output span of  $\Delta I_{OFS}$ :

$$\left[ \left( 0.016 \frac{\text{amps}}{\text{volt}} \right) + \left( \frac{40}{\text{R}_{\text{S}}} \right) \right] \Delta e_{\text{IN}} = \Delta I_{\text{O}} = 16 \text{mA}.$$

Solving for R<sub>S</sub>:

$$R_{s} = \frac{40}{\Delta I_{o} / \Delta e_{IN} - 0.016 \frac{amps}{volt}}$$

(1)

For example, if  $\Delta e_{INFS} = 100 \text{mV}$  for  $\Delta I_{OFS} = 16 \text{mA}$ ,

$$R_{s} = \frac{40}{(16\text{mA}/100\text{mV}) - 0.016} = \frac{40}{0.16 - 0.016}$$

$$= \frac{40}{0.144} = 278\Omega$$

See the Typical Characteristics for a plot of  $R_S$  vs  $\Delta e_{INFS}$ . Note that in order not to exceed the 20mA upper range limit,  $e_{IN}$  must be less than 1V when  $R_S = \infty$  and proportionately smaller as  $R_S$  decreases.

#### **BIASING THE INPUTS**

Because the XTR operates from a single supply, both  $e_1$ and  $e_2$  must be biased approximately 5V above the voltage at pin 7 to assure linear response. This is easily done by using one or both current sources and an external resistor,  $R_2$ . Figure 5 shows the simplest case—a floating voltage source  $e'_2$ . The 2mA from the current sources flows through the 2.5k $\Omega$  value of  $R_2$  and both  $e_1$  and  $e_2$  are raised by the required 5V with respect to pin 7. For linear operation the constraint is:

$$+4V \le e_1 \le +6V$$

$$+4V \le e_2 \le +6V$$

The offset adjustment is used to remove the offset voltage of the input amplifier. When the input differential voltage  $(e_{IN})$  equals zero, adjust for 4mA output.

Figure 6 shows a similar connection for a resistive transducer. The transducer could be excited either by one (as shown) or both current sources. Also, the offset adjustment has higher resolution compared to Figure 5.

Figure 5. Basic Connection for Floating Voltage Source

#### **CMV AND CMR**

The XTR101 is designed to operate with a nominal 5V common-mode voltage at the input and will function properly with either input operating over the range of 4V to 6V with respect to pin 7. The error caused by the 5V CMV is already included in the accuracy specifications.

If the inputs are biased at some other CMV, then an input offset error term is (CMV - 5)/CMRR, where CMR is in dB, and CMRR is in V/V.

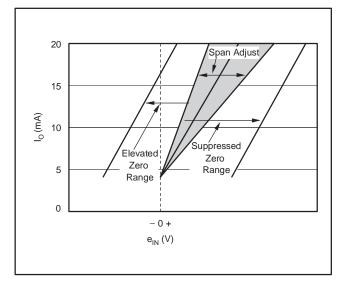

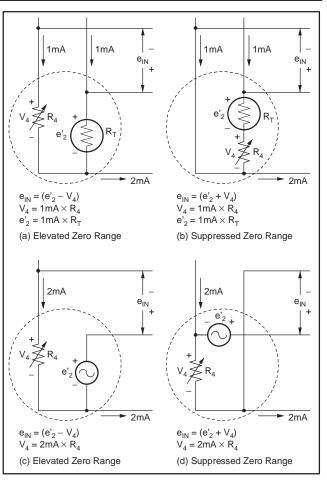

### SIGNAL SUPPRESSION AND ELEVATION

In some applications, it is desired to have suppressed zero range (input signal elevation) or elevated zero range (input signal suppression). This is easily accomplished with the XTR101 by using the current sources to create the suppression/elevation voltage. The basic concept is shown in Figure 7 and Figure 8(a). In this example, the sensor voltage is derived from  $R_T$  (a thermistor, RTD, or other variable resistance element) and excited by one of the 1mA current sources. The other current source is used to create the elevated zero range voltage. Figure 8(b), (c), and (d) show some of the possible circuit variations. These circuits have the desirable feature of noninteractive span and suppression/elevation adjustments.

Note: It is not recommended to use the optional offset voltage null (pins 1, 2, and 14) for elevation/suppression. This trim capability is used only to null the amplifier's input offset voltage. In many applications the already low offset voltage (typically  $20\mu V$ ) will not need to be nulled at all. Adjusting the offset voltage to non-zero values will disturb the voltage drift by  $\pm 0.3\mu V/^{\circ}C$  per  $100\mu V$  or induced offset.

Figure 7. Elevation and Suppression Graph

Figure 8. Elevation and Suppression Circuits

# **APPLICATION INFORMATION**

The small size, low offset voltage and drift, excellent linearity, and internal precision current sources make the XTR101 ideal for a variety of two-wire transmitter applications. It can be used by OEMs producing different types of transducer transmitter modules and by data acquisition systems manufacturers who gather transducer data. Current-mode transmission greatly reduces noise interference. The two-wire nature of the device allows economical signal conditioning at the transducer. Thus the XTR101 is, in general, very suitable for individualized and special-purpose applications.

### **EXAMPLE 1**

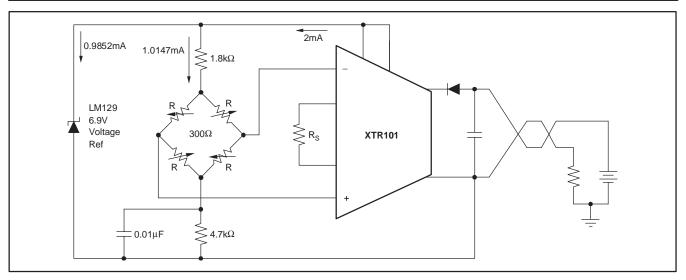

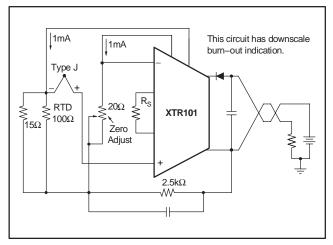

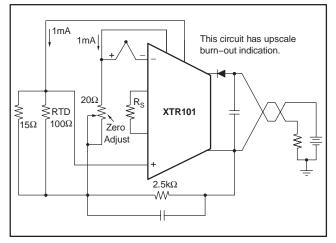

An RTD transducer is shown in Figure 9.

Given a process with temperature limits of +25°C and +150°C, configure the XTR101 to measure the temperature with a platinum RTD which produces  $100\Omega$  at 0°C and  $200\Omega$  at +266°C (obtained from standard RTD tables). Transmit 4mA for +25°C and 20mA for +150°C.

#### **COMPUTING R<sub>S</sub>:**

The sensitivity of the RTD is  $\Delta R/\Delta T = 100\Omega/266^{\circ}C$ . When excited with a 1mA current source for a 25°C to 150°C range (a 125°C span), the span of  $e_{IN}$  is 1mA × (100 $\Omega/266^{\circ}C$ ) × 125°C = 47mV =  $\Delta e_{IN}$ .

From Equation 1,  $R_s = \frac{40}{\Delta I_o / \Delta e_{IN} - 0.016 \frac{amps}{volt}}$  $R_s = \frac{40}{16mA/47mV - 0.016A/V} = \frac{40}{0.3244} = 123.3\Omega$

Span adjustment (calibration) is accomplished by trimming  $\ensuremath{\mathsf{R}_{\mathsf{S}}}\xspace$

#### **COMPUTING R4:**

At + 25°C, e'\_{2} = 1mA(R\_{T} + \Delta R\_{T})

= 1mA

$$\left[100\Omega + \frac{100\Omega}{266°C} \times 25°C\right]$$

= 1mA(109.4 $\Omega$ ) = 109.4mV

In order to make the lower range limit of 25°C correspond to the output lower range limit of 4mA, the input circuitry shown in Figure 9 is used.

e<sub>IN</sub>, the XTR101 differential input, is made 0 at 25°C or:

$$e'_{2 \ 25^{\circ}C} - V_4$$

thus,  $V_4 = e'_{2 \ 25^{\circ}C} = 109.4 \text{mV}$

$R_4 = \frac{V_4}{1\text{mA}} = \frac{109.4 \text{mV}}{1\text{mA}} = 109.4 \Omega$

#### COMPUTING R<sub>2</sub> AND CHECKING CMV:

At + 25°C, e'<sub>2</sub> = 109.4mV

At + 150°C, e'<sub>2</sub> = 1mA(R<sub>T</sub> +

$$\Delta$$

R<sub>T</sub>)

= 1mA[100 $\Omega$  +  $\frac{100\Omega}{266°C} \times 150°C]= 156.4mV$

Since both  $e'_2$  and  $V_4$  are small relative to the desired 5V common-mode voltage, they may be ignored in computing  $R_2$  as long as the CMV is met.

$$\begin{array}{l} \mathsf{R}_2 = \frac{5\mathsf{V}}{2\mathsf{m}\mathsf{A}} = 2.5\mathsf{k}\Omega \\ \mathsf{e}_2\mathsf{min} = 5\mathsf{V} + 0.1094\mathsf{V} \\ \mathsf{e}_2\mathsf{max} = 5\mathsf{V} + 0.1564\mathsf{V} \\ \mathsf{e}_1 = 5\mathsf{V} + 0.1094\mathsf{V} \end{array} \right) \begin{array}{l} \mathsf{The} \ 4\mathsf{V} \ \mathsf{to} \ \mathsf{6V} \ \mathsf{CMV} \\ \mathsf{requirement} \ \mathsf{is} \ \mathsf{met}. \end{array}$$

SBOS146A - OCTOBER 1986 - REVISED AUGUST 2004

Figure 9. Circuit for Example 1

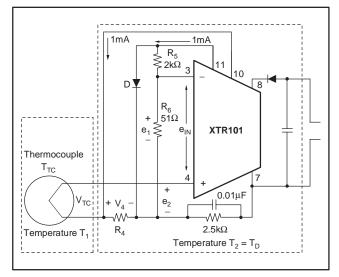

### EXAMPLE 2

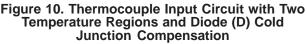

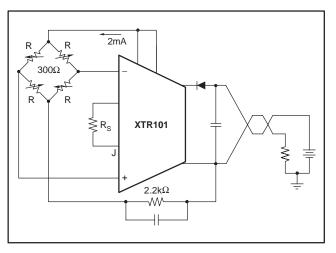

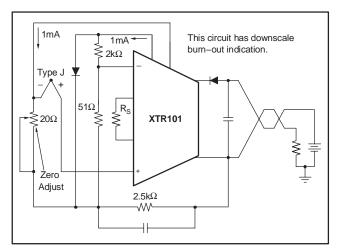

A thermocouple transducer is shown in Figure 10.

Given a process with temperature (T<sub>1</sub>) limits of 0°C and +1000°C, configure the XTR101 to measure the temperature with a type J thermocouple that produces a 58mV change for 1000°C change. Use a semiconductor diode for cold junction compensation to make the measurement relative to 0°C. This is accomplished by supplying a compensating voltage (V<sub>R6</sub>) equal to that normally produced by the thermocouple with its cold junction (T<sub>2</sub>) at ambient. At a typical ambient of +25°C, this is 1.28mV (obtained from standard thermocouple tables with reference junction of 0°C). Transmit 4mA for T<sub>1</sub> = 0°C and 20mA for T<sub>1</sub> = +1000°C. Note:  $e_{IN} = e_2 - e_1$  indicates that T<sub>1</sub> is relative to T<sub>2</sub>.

### ESTABLISHING R<sub>S</sub>:

The input full-scale span is  $58mV (\Delta e_{INFS} = 58mV)$ .

R<sub>S</sub> is found from Equation 1.

$$R_{s} = \frac{40}{\Delta I_{o} / \Delta e_{IN} - 0.016 \frac{amps}{volt}}$$

$$= \frac{40}{16mA / 58mV - 0.016A / V} = \frac{40}{0.2599} = 153.9\Omega$$

#### SELECTING R4:

$R_4$  is chosen to make the output 4mA at  $T_{TC}$  = 0°C ( $V_{TC}$  = –1.28mV) and  $T_D$  = +25°C ( $V_D$  = 0.6V); see Figure 10.

$V_{TC}$  will be -1.28mV when  $T_{TC} = 0^{\circ}C$  and the reference junction is at +25°C.  $e_1$  must be computed for the condition of  $T_D = +25^{\circ}C$  to make  $e_{IN} = 0V$ .

$$V_{D 25^{0}C} = 600 \text{mV}$$

$$e_{1 25^{0}C} = 600 \text{mV} \left(\frac{51}{2051}\right) = 14.9 \text{mV}$$

$$e_{IN} = e_{2} - e_{1} = V_{TC} + V_{4} - e_{1}$$

With  $e_{IN} = 0$  and  $V_{TC} = -1.28mV$ ,

$$V_{4} = e_{1} + e_{IN} - V_{TC}$$

= 14.9mV + 0V - (- 1.28mV)

1mA(R<sub>4</sub>) = 16.18mV

R<sub>4</sub> = 16.18\Omega

#### COLD JUNCTION COMPENSATION:

A temperature reference circuit is shown in Figure 11.

The diode voltage has the form:

$$V_{D} = \frac{KT}{q} \ln \frac{I_{DIODE}}{I_{SAT}}$$

Typically at  $T_2 = +25^{\circ}$ C,  $V_D = 0.6V$  and  $\Delta V_D/\Delta T = -2mV/^{\circ}$ C. R<sub>5</sub> and R<sub>6</sub> form a voltage divider for the diode voltage V<sub>D</sub>. The divider values are selected so that the gradient  $\Delta V_D/\Delta T$  equals the gradient of the thermocouple at the reference temperature. At +25°C this is approximately  $52\mu V/^{\circ}$ C (obtained from a standard thermocouple table); therefore,

$$\frac{\Delta T_{C}}{\Delta T} = \frac{\Delta V_{D}}{\Delta T} \left( \frac{R_{6}}{R_{5} + R_{6}} \right)$$

$$\frac{52\mu V}{^{\circ}C} = \frac{2000\mu V}{^{\circ}C} \left( \frac{R_{6}}{R_{5} + R_{6}} \right)$$

(2)

$R_5$  is chosen as  $2k\Omega$  to be much larger than the resistance of the diode. Solving for  $R_6$  yields 51 $\Omega$ .

Figure 11. Cold Junction Compensation Circuit

### THERMOCOUPLE BURN-OUT INDICATION

In process control applications it is desirable to detect when a thermocouple has burned out. This is typically done by forcing the two-wire transmitter current to either limit when the thermocouple impedance goes very high. The circuits of Figure 16 and Figure 17 inherently have downscale indication. When the impedance of the thermocouple gets very large (open) the bias current flowing into the + input (large impedance) will cause  $I_O$  to go to its lower range limit value (about 3.8mA). If upscale indication is desired, the circuit of Figure 18 should be used. When  $T_C$  opens, the output will go to its upper range limit value (about 25mA or higher).

### **OPTIONAL INPUT OFFSET VOLTAGE TRIM**

The XTR101 has provisions for nulling the input offset voltage associated with the input amplifiers. In many applications the already low offset voltages ( $30\mu$ V max for the B grade and  $60\mu$ V max for the A grade) will not need to be nulled at all. The null adjustment can be done with a potentiometer at pins 1, 2, and 14; see Figure 5 and Figure 6. Either of these two circuits may be used. NOTE: It is not recommended to use this input offset voltage nulling capability for elevation or suppression. See the *Signal Suppression and Elevation* section for the proper techniques.

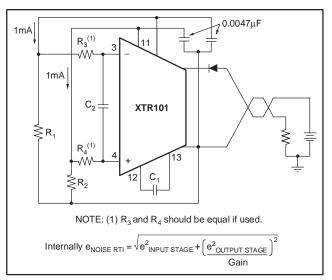

### **OPTIONAL BANDWIDTH CONTROL**

Low-pass filtering is recommended where possible and can be done by either one of two techniques; see Figure 12.  $C_2$  connected to pins 3 and 4 will reduce the bandwidth with a cutoff frequency given by:

$$f_{CO} = \frac{15.9}{(R_1 + R_2 + R_3 + R_4)(C_2 + 3pF)}$$

This method has the disadvantage of having  $f_{CO}$  vary with  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$ , and it may require large values of  $R_3$  and  $R_4$ . The other method, using  $C_1$ , will use smaller values of capacitance and is not a function of the input resistors. It is, however, more subject to nonlinear distortion caused by slew rate limiting. This is normally not a problem with the slow signals associated with most process control transducers. The relationship between  $C_1$  and  $f_{CO}$  is shown in the Typical Characteristics.

Figure 12. Optional Filtering

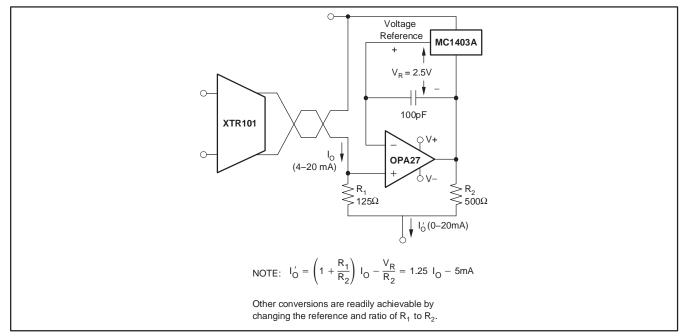

Figure 13. 0-20mA Output Converter

# **APPLICATION CIRCUITS**

# XTR101

SBOS146A - OCTOBER 1986 - REVISED AUGUST 2004

Figure 15. Bridge Input, Current Excitiation

Figure 16. Thermocouple Input with RTD Cold Junction Compensation

Figure 17. Thermocouple Input with Diode Cold Junction Compensation

Figure 18. Thermocouple Input with RTD Cold Junction Compensation

# XTR101

SBOS146A - OCTOBER 1986 - REVISED AUGUST 2004

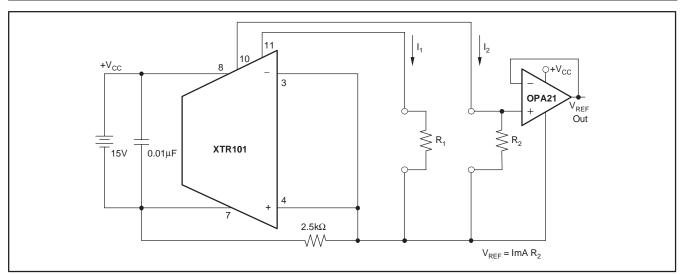

Figure 19. Dual Precision Current Sources Operated from One Supply

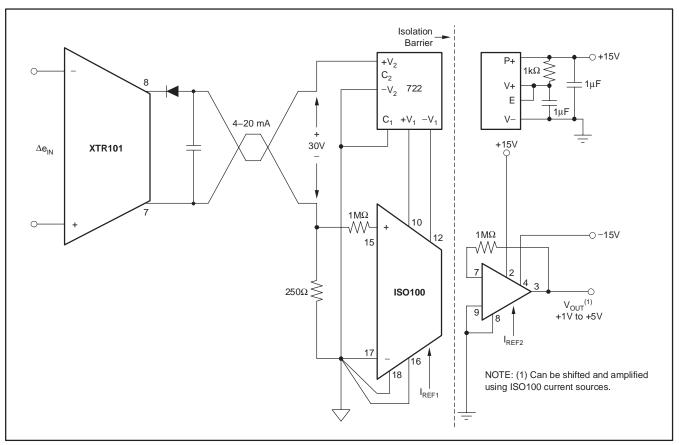

Figure 20. Isolated Two-Wire Current Loop

### **DETAILED ERROR ANALYSIS**

The ideal output current is:

$$I_{O IDEAL} = 4mA + K e_{IN}$$

(3)

where K is the span (gain) term,  $\left(0.016 \frac{\text{amps}}{\text{volt}} + \left(\frac{40}{R_s}\right)\right)$

In the XTR101 there are three major components of error:

- 1.  $\sigma_{O}$  = errors associated with the output stage.

- 2.  $\sigma_S$  = errors associated with span adjustment.

- 3.  $\sigma_I$  = errors associated with the input stage.

The transfer function including these errors is:

$$I_{O \text{ ACTUAL}} = (4mA + \sigma_0) + K(1 + \sigma_s)(e_{IN} + \sigma_I)$$

(4)

When this expression is expanded, second-order terms  $(\sigma_S, \sigma_I)$  dropped, and terms collected, the result is:

$$I_{O \text{ ACTUAL}} = (4\text{mA} + \sigma_0) + K e_{IN} + K\sigma_I + K\sigma_S e_{IN}$$

(5)

The error in the output current is  $I_{O \ ACTUAL} - I_{O \ IDEAL}$  and can be found by subtracting Equation 3 from Equation 5.

$$I_{O ERROR} = \sigma_{O} + K\sigma_{I} + K\sigma_{S} e_{IN}$$

(6)

This is a general error expression. The composition of each component of error depends on the circuitry inside the XTR101 and the particular circuit in which it is applied. The circuit of Figure 9 will be used to illustrate the principles.

$$\sigma_{\rm O} = I_{\rm OS\,RTO} \tag{7}$$

$$\sigma_{\rm S} = \varepsilon_{\rm NONLINEARITY} + \varepsilon_{\rm SPAN} \tag{8}$$

$$\sigma_{\rm I} = V_{\rm OSI} + \left(I_{\rm B1} + R_4 - I_{\rm B2} R_{\rm T}\right) + \frac{\Delta V_{\rm CC}}{\rm PSRR} + \frac{\frac{(e_1 + e_2)}{2} - 5V}{\rm CMRR}$$

(9)

The term in parentheses may be written in terms of offset current and resistor mismatches as  $I_{B1} \Delta R + I_{OS}' R_4$ .

V<sub>OSI</sub><sup>(1)</sup> = input offset voltage.

$I_{B1}^{(1)}$ ,  $I_{B2}^{(1)}$  = input bias current.

$I_{OSI}^{(1)}$  = input offset current.

$I_{OS RTO}^{(1)}$  = output offset current error.

$\Delta R = R_T - R_4 = mismatch in resistor.$

$\Delta V_{CC}$  = change supply voltage between pins 7 and 8 away from 24V nominal.

PSRR<sup>(1)</sup> = power-supply rejection ratio.

CMRR<sup>(1)</sup> = common-mode rejection ratio.

$\varepsilon_{\text{NONLIN}}^{(1)}$  = span nonlinearity.

$\varepsilon_{\text{SPAN}}^{(1)}$  = span equation error.

Untrimmed error = 5% max. May be trimmed to zero.

(1) These items can be found in the Electrical Characteristics.

### **EXAMPLE 3**

See the circuit in Figure 9 with the XTR101BG specifications and the following conditions:  $R_T$  = 109.4 $\Omega$  at 25°C,  $R_T$  = 156.4 $\Omega$  at 150°C,  $I_O$  = 4mA at 25°C,  $I_O$  = 20mA at 150°C,  $R_S$  = 123.3 $\Omega$ ,  $R_4$  = 109 $\Omega$ ,  $R_L$  = 250 $\Omega$ ,  $R_{LINE}$  = 100 $\Omega$ ,  $V_{DI}$  = 0.6V, and  $V_{PS}$  = 24V  $\pm$  0.5%. Determine the % error at the upper and lower range values.

#### A. AT THE LOWER RANGE VALUE (T = $+25^{\circ}$ C)

$\sigma_{\rm O} = I_{\rm OS RTO} = \pm 6 \mu A$

$$\sigma_{I} = V_{OSI} + \left(I_{BI} \Delta R + I_{OSI} R_{4}\right) + \frac{\Delta V_{CC}}{PSRR} + \left[\frac{\left[\frac{e_{1} + e_{2}}{2}\right] - 5V}{CMRR}\right]$$

$$\Delta R = R_{T \, 25^{\circ}C} - R_4 = 109.4 - 109 \approx 0$$

$$\Delta V_{CC} = (24 \times 0.005) + 4mA(25052 + 10052) + 0.6V$$

$$= 120mV + 1400mV + 600mV = 2120mV$$

$$\begin{array}{l} {\mathsf{e}_1} = (2{\mathsf{m}}{\mathsf{A}} \times 2.5 {\mathsf{k}} \Omega) + (1{\mathsf{m}}{\mathsf{A}} \times 109 \Omega) \\ = 5.109 {\mathsf{V}} \\ {\mathsf{e}_2} = (2{\mathsf{m}}{\mathsf{A}} \times 2.5 {\mathsf{k}} \Omega) + (1{\mathsf{m}}{\mathsf{A}} \times 109.4 \Omega) \\ = 5.1094 {\mathsf{V}} \end{array}$$

$$\frac{(e_1 + e_2)}{2} - 5V = 0.1092V$$

$\mathsf{PSRR}$  = 3.16  $\times$  10  $^{5}$  for 110dB

CMRR = 31.6  $\times$  10  $^3$  for 90dB

$$\sigma_{1} = 30\mu V + (150nA \times 0 + 20nA \times 109\Omega) + \frac{2120mV}{3.16 \times 10^{5}} + \frac{0.1092V}{3.16 \times 10^{3}}$$

(10)

=  $30\mu V + 2.18\mu V + 6.7\mu V + 3.46\mu V$

=  $42.34\mu V$

$$= 0.0001 + 0 \text{ (assumes trim of } R_{s})$$

$I_{O ERROR} = \sigma_{O} + K \sigma_{I} + K \sigma_{S} e_{IN}$

$$K = 0.016 + \frac{40}{R_{s}} = 0.016 + \frac{40}{123.3\Omega}$$

$$= 0.340 \frac{\text{amps}}{\text{volts}}$$

$$e_{\text{IN}} = e_{2} - V_{4} = I_{\text{REF1}} R_{\text{T}25^{0}\text{C}} - I_{\text{REF2}} R_{2}$$

Since  $R_{T 25^{\circ}C} = R_4$ :

$$\begin{split} e_{IN} &= \left(I_{REF1} - I_{REF2}\right)R_4 = 0.4\mu A \times 109\Omega \\ &= 43.6\mu V \end{split}$$

Since the maximum mismatch of the current references is 0.04% of 1mA = 0.4 $\mu$ A:

$$\begin{split} I_{o} \mbox{ error } &= 6\mu A + (0.34 A/V \times 42.34 \mu V) + \\ &\quad (0.34 A/V \times 0.0001 \times 43.6 \mu V) \\ &= 6\mu A + 14.40 \mu A + 0.0015 \mu A = 20.40 \mu A \\ \mbox{\% error } &= \frac{20.40 \mu A}{16 m A} \times 100\% \end{split}$$

0.13% of span at lower range value.

### B. AT THE UPPER RANGE VALUE (T = +150°C)

$$\begin{split} \Delta \mathsf{R} \; = \; \mathsf{R}_{\mathsf{T}\; 150^{0}\mathsf{C}} - \; \mathsf{R}_{\mathsf{4}} \; = \; 156.4 - \; 109.4 \; = \; 47\Omega \\ \Delta \mathsf{V}_{\mathsf{CC}} \; = \; (24 \; \times \; 0.005) \; + \; 20\mathsf{m}\mathsf{A}(250\Omega \; + \; 100\Omega) \; + \; 0.6\mathsf{V} \\ \; = \; 7720\mathsf{m}\mathsf{V} \end{split}$$

$$\begin{array}{l} {e_1} = {\rm{5.109V}} \\ {e_2} = \left( {2mA \times {\rm{2.5k}\Omega}} \right) + \left( {1mA \times {\rm{156.4}\Omega}} \right) \\ = {\rm{5.156V}} \end{array}$$

$$\frac{(e_1 - e_2)}{2} - 5V = 0.1325V$$

$\sigma_0 = 6\mu A$

$$\begin{split} \sigma_{1} &= 30\mu V + (150nA \times 47\Omega + 20nA \times 190\Omega) + \\ &= \frac{7720mV}{3.16 \times 10^{5}} + \frac{0.1325V}{3.16 \times 10^{3}} \\ &= 30\mu V + 9.23\mu V + 24\mu V + 4.19\mu V \\ &= 67.42\mu V \\ \sigma_{S} &= 0.0001 \\ e_{IN} &= e'_{2} - V_{4} = I_{REF1} R_{T\,150^{\circ}C} - I_{REF2} R_{4} \\ &= (1mA \times 156.4\Omega) - (1mA \times 109\Omega) \\ &= 47mV \end{split}$$

$$I_{o} \text{ error} = \sigma_{o} + K \sigma_{I} + K \sigma_{s} e_{IN}$$

(11)

= 6\mu A + (0.34A/V \times 67.42\mu V) +

(0.34A/V \times 0.0001 \times 47000\mu V)

= 6\mu A + 22.92\mu A + 1.60\mu A

= 30.52\mu A

% error =  $\frac{30.52\mu A}{16\mu A} \times 100\%$

0.19% of span at upper range value.

#### CONCLUSIONS

**Lower Range:** From Equation 10, it is observed that the predominant error term is the input offset voltage  $(30\mu V \text{ for the B grade})$ . This is of little consequence in many applications. V<sub>OS RTI</sub> can, however, be nulled using the plots shown in Figure 5 and Figure 6. The result is an error of 0.06% of span instead of 0.13% of span.

**Upper Range:** From Equation 11, the predominant errors are I<sub>OS RTO</sub> (6µA), V<sub>OS RTI</sub> (30µV), and I<sub>B</sub> (150nA), max, B grade. Both I<sub>OS</sub> and V<sub>OS</sub> can be trimmed to zero; however, the result is an error of 0.09% of span instead of 0.19% of span.

#### RECOMMENDED HANDLING PROCEDURES FOR INTEGRATED CIRCUITS

All semiconductor devices are vulnerable, in varying degrees, to damage from the discharge of electrostatic energy. Such damage can cause performance degradation or failure, either immediate or latent. As a general practice, we recommend the following handling procedures to reduce the risk of electrostatic damage:

- 1. Remove the static-generating materials (such as untreated plastic) from all areas that handle microcircuits.

- 2. Ground all operators, equipment, and work stations.

- 3. Transport and ship microcircuits, or products incorporating microcircuits, in static-free, shielded containers.

- 4. Connect together all leads of each device by means of a conductive material when the device is not connected into a circuit.

- 5. Control relative humidity to as high a value as practical (50% recommended).

28-Aug-2017

### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | •       | Pins | •    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| XTR101AG         | NRND   | CDIP SB      | JD      | 14   | 1    | Green (RoHS<br>& no Sb/Br) | AU               | N / A for Pkg Type  |              | XTR101AG       |         |

| XTR101AP         | ACTIVE | PDIP         | Ν       | 14   | 25   | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | N / A for Pkg Type  | -40 to 85    | XTR101AP       | Samples |

| XTR101APG4       | ACTIVE | PDIP         | Ν       | 14   | 25   | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | N / A for Pkg Type  | -40 to 85    | XTR101AP       | Samples |

| XTR101AU         | ACTIVE | SOIC         | DW      | 16   | 40   | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | XTR101AU       | Samples |

| XTR101AU/1K      | ACTIVE | SOIC         | DW      | 16   | 1000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | XTR101AU       | Samples |

| XTR101AU/1KG4    | ACTIVE | SOIC         | DW      | 16   | 1000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | XTR101AU       | Samples |

| XTR101AUG4       | ACTIVE | SOIC         | DW      | 16   | 40   | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | XTR101AU       | Samples |

| XTR101BG         | NRND   | CDIP SB      | JD      | 14   | 1    | Green (RoHS<br>& no Sb/Br) | AU               | N / A for Pkg Type  | -40 to 85    | XTR101BG       |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

#### www.ti.com

## PACKAGE OPTION ADDENDUM

28-Aug-2017

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

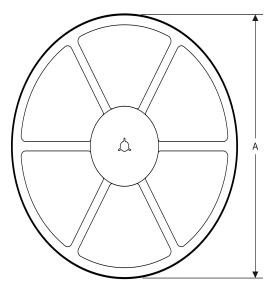

### TAPE AND REEL INFORMATION

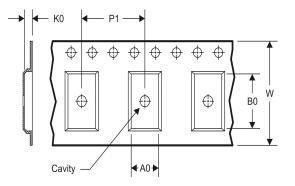

#### REEL DIMENSIONS

Texas Instruments

#### TAPE DIMENSIONS

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

\*All dimensions are nominal

TAPE AND REEL INFORMATION

| Device      |      | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| XTR101AU/1K | SOIC | DW                 | 16   | 1000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

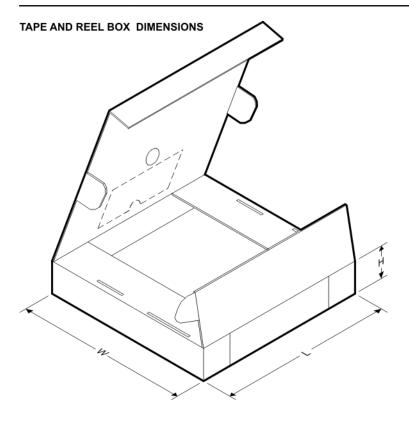

# PACKAGE MATERIALS INFORMATION

14-Jul-2012

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| XTR101AU/1K | SOIC         | DW              | 16   | 1000 | 367.0       | 367.0      | 38.0        |

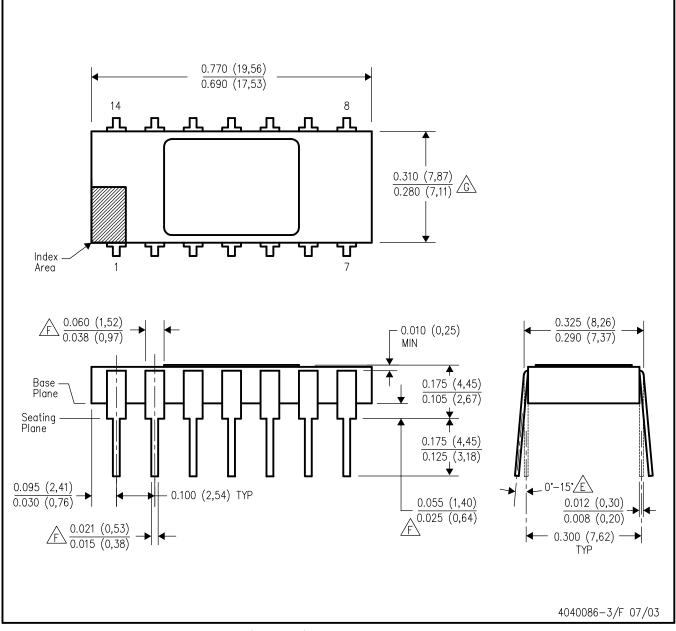

JD (R-CDIP-T14)

## CERAMIC SIDE-BRAZE DUAL-IN-LINE

- NOTES:

- All linear dimensions are in inches (millimeters). Α. B. This drawing is subject to change without notice.

- C. Controlling dimension: inch.

- D. Leads within 0.005 (0,13) radius of true position (TP) at gage plane with maximum material condition and unit installed.

- Ε Angle applies to spread leads prior to installation.

- F Outlines on which the seating plane is coincident with the plane (standoff = 0), terminals lead standoffs are not required, and lead shoulder may equal lead width along any part of the lead above the seating/base plane.

- G Body width does not include particles of packing materials.

- Η. A visual index feature must be located within the cross-hatched area.

# **GENERIC PACKAGE VIEW**

# SOIC - 2.65 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4040000-2/H

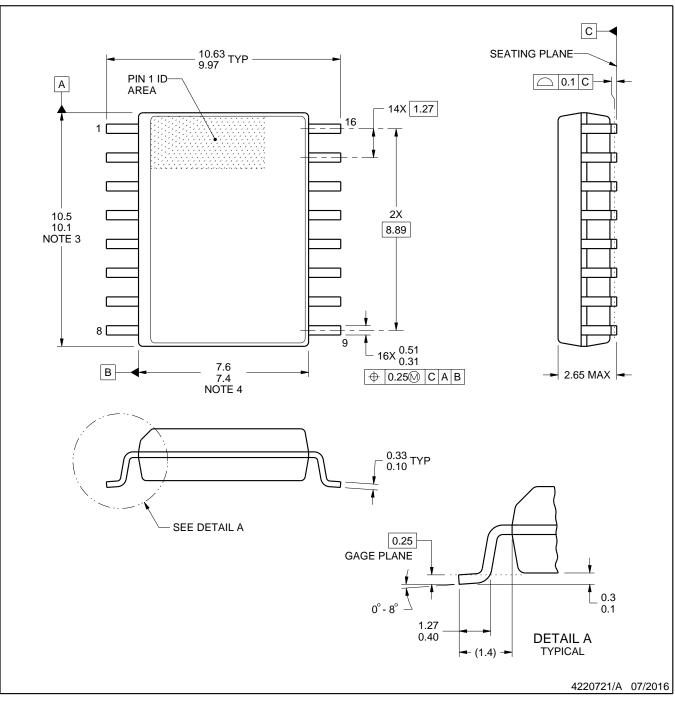

# **DW0016A**

# **PACKAGE OUTLINE**

SOIC - 2.65 mm max height

SOIC

#### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm, per side.

- 5. Reference JEDEC registration MS-013.

# DW0016A

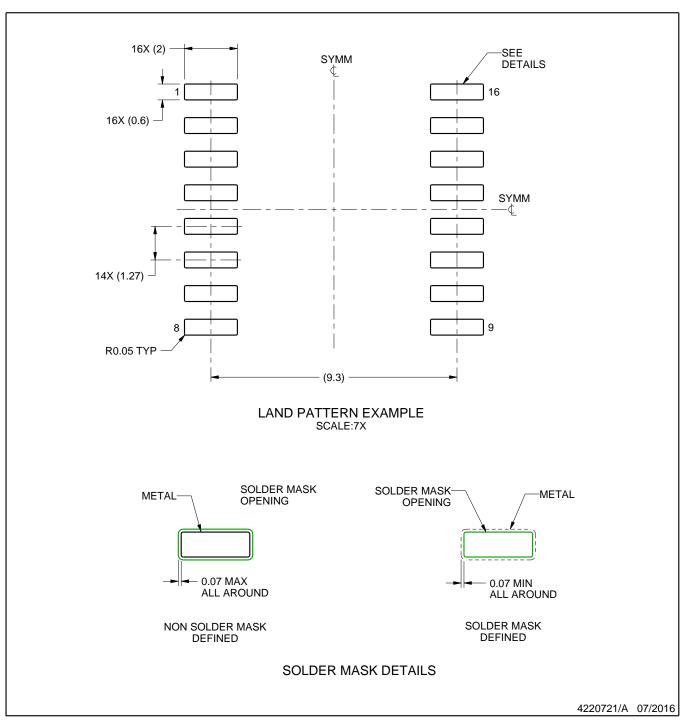

# **EXAMPLE BOARD LAYOUT**

### SOIC - 2.65 mm max height

SOIC

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

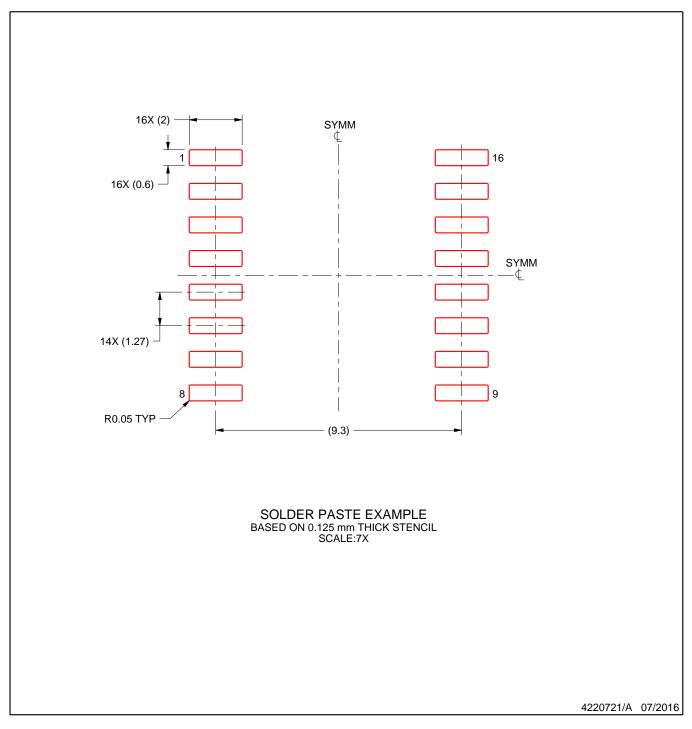

# DW0016A

# **EXAMPLE STENCIL DESIGN**

### SOIC - 2.65 mm max height

SOIC

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

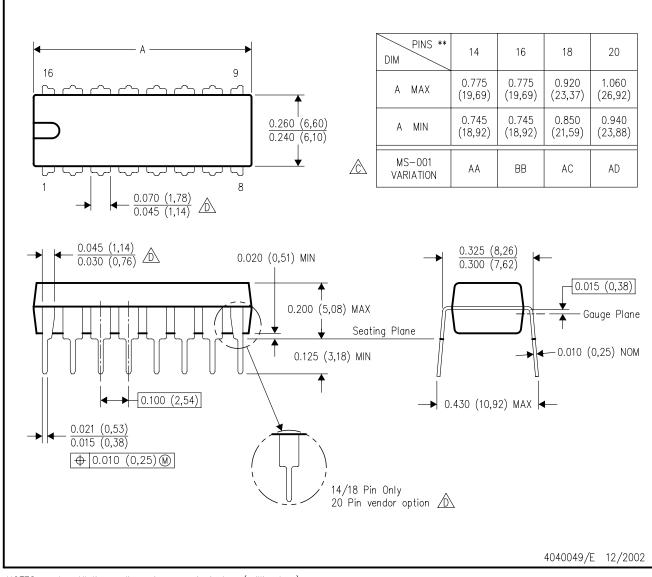

# N (R-PDIP-T\*\*)

PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- $\triangle$  The 20 pin end lead shoulder width is a vendor option, either half or full width.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

TI's published terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products that TI has qualified and released to market. Additional terms may apply to the use or sale of other types of TI products and services.

Reproduction of significant portions of TI information in TI data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such reproduced documentation. Information of third parties may be subject to additional restrictions. Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyers and others who are developing systems that incorporate TI products (collectively, "Designers") understand and agree that Designers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Designers have full and exclusive responsibility to assure the safety of Designers' applications and compliance of their applications (and of all TI products used in or for Designers' applications) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to their applications, Designer has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any applications that include TI products, Designer will thoroughly test such applications and the functionality of such TI products as used in such applications.

TI's provision of technical, application or other design advice, quality characterization, reliability data or other services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using TI Resources in any way, Designer (individually or, if Designer is acting on behalf of a company, Designer's company) agrees to use any particular TI Resource solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

Designer is authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNER AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Unless TI has explicitly designated an individual product as meeting the requirements of a particular industry standard (e.g., ISO/TS 16949 and ISO 26262), TI is not responsible for any failure to meet such industry standard requirements.

Where TI specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards, such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and requirements. Using products in an application does not by itself establish any safety features in the application. Designers must ensure compliance with safety-related requirements and standards applicable to their applications. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equipment includes, without limitation, all medical devices identified by the U.S. Food and Drug Administration as Class III devices and equivalent classifications outside the U.S.

TI may expressly designate certain products as completing a particular qualification (e.g., Q100, Military Grade, or Enhanced Product). Designers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Designers' own risk. Designers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's noncompliance with the terms and provisions of this Notice.

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated