# 4-20mA, TWO-WIRE TRANSMITTER "Smart" Programmable with Signal Conditioning

### **FEATURES**

- COMPLETE TRANSMITTER + RTD LINEARIZATION

- TWO-WIRE, 4-20mA OUTPUT

- VOLTAGE OUTPUT (0.5V to 4.5V)

- ELIMINATES POTENTIOMETERS AND TRIMMING

- DIGITALLY CALIBRATED

- 5V SUB-REGULATOR OUTPUT

- SERIAL SPI<sup>™</sup> BUS INTERFACE

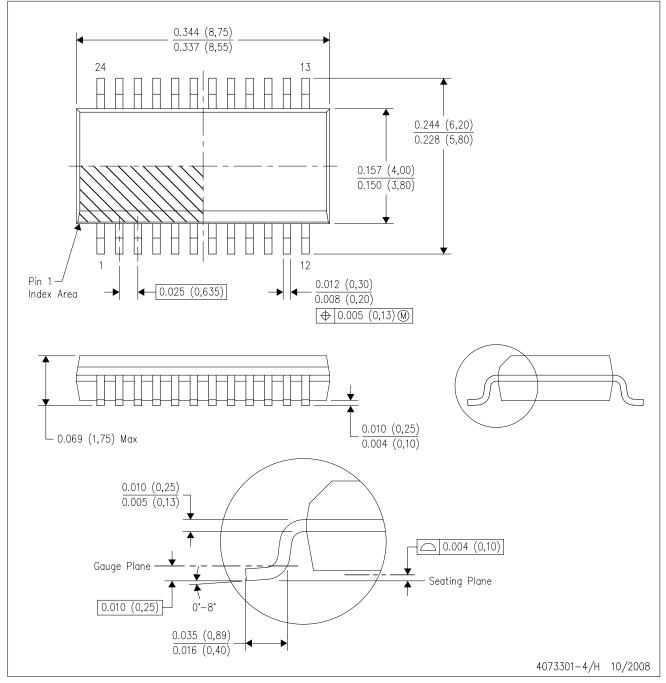

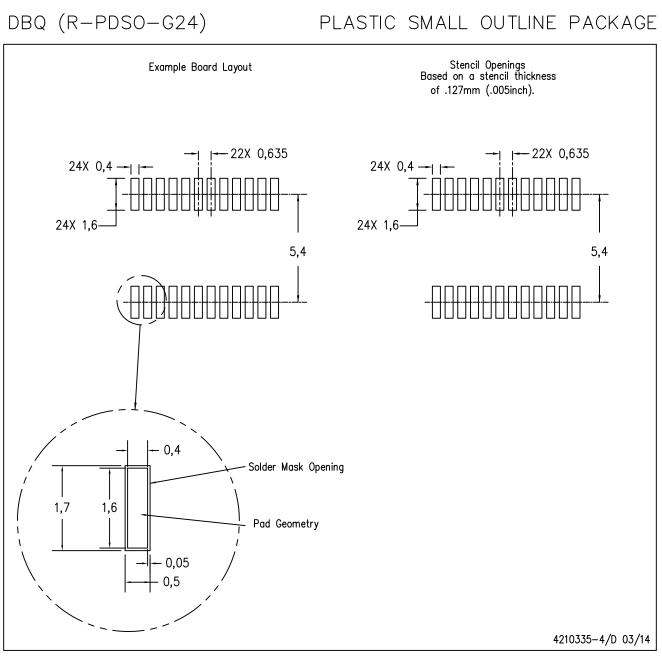

- SSOP-24 PACKAGE

## **APPLICATIONS**

- REMOTE RTD TRANSMITTERS

- PRESSURE BRIDGE TRANSMITTERS

- STRAIN GAGE TRANSMITTERS

- SCADA REMOTE DATA ACQUISITION

- WEIGHING SYSTEMS

- INDUSTRIAL PROCESS CONTROL

### DESCRIPTION

The XTR108 is a "smart," programmable, 4-20mA, two-wire transmitter designed for temperature and bridge sensors. Zero, span, and linearization errors in the analog signal path can be calibrated via a standard digital serial interface, eliminating manual trimming. Non-volatile external EEPROM stores calibration settings.

The all-analog signal path contains an input multiplexer, autozeroed programmable-gain instrumentation amplifier, dual programmable current sources, linearization circuit, voltage reference, sub-regulator, internal oscillator, control logic, and an output current amplifier. Programmable level shifting compensates for sensor DC offsets. Selectable up- and down-scale output indicates out-of-range and burnout per NAMUR NE43. Automatic reset is initiated when supply is lost.

Current sources, steered through the multiplexer, can be used to directly excite RTD temperature sensors, pressure bridges, or other transducers. An uncommitted op amp can be used to convert current into a voltage. The XTR108 is specified for  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI is a trademark of Motorola, Inc. All other trademarks are the property of their respective owners.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Loop Supply Voltage, $V_{PS}$ Dependent on External FET                               |

|---------------------------------------------------------------------------------------|

| XTR Supply Voltage, External V <sub>S</sub> (Referenced to I <sub>RET</sub> Pin)+5.5V |

| Input Voltage to Multiplexer (Referenced to $\rm I_{RET}$ Pin) 0V to $\rm V_S$        |

| Output Current Limit Continuous                                                       |

| Storage Temperature Range55°C to +125°C                                               |

| Junction Temperature +165°C                                                           |

| Lead Temperature (soldering, 10s) +300°C                                              |

NOTE: (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability.

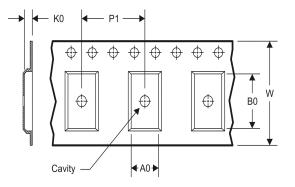

### PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT  | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|----------|--------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| XTR108EA | SSOP-24      | DBQ                   | –40°C to +85°C                    | XTR108EA           | XTR108EA           | Rails                        |

| "        | "            | "                     | "                                 | "                  | XTR108EA/2K5       | Tape and Reel, 2500          |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

## **ELECTRICAL CHARACTERISTICS**

#### **Boldface** limits apply over the specified temperature range, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ .

At T<sub>A</sub> = +25°C, V<sub>PS</sub> = 24V, and Supertex DN2540 external depletion-mode FET transistor, unless otherwise noted, all voltages measured with respect to I<sub>RET</sub> pin.

|                                                       |                                               |      | XTR108EA     |                      |         |

|-------------------------------------------------------|-----------------------------------------------|------|--------------|----------------------|---------|

| PARAMETER                                             | CONDITIONS                                    | MIN  | ТҮР          | MAX                  | UNITS   |

| V <sub>IN</sub> TO I <sub>OUT</sub> TRANSFER FUNCTION | I <sub>O</sub> = V <sub>IN</sub> (Span) + 4mA |      |              |                      |         |

| Output                                                |                                               |      |              |                      |         |

| Specified Range                                       |                                               | 4    |              | 20                   | mA      |

| Over-Scale Limit Resolution                           | Digital Select: 21-28.5mA                     |      | 0.5          |                      | mA      |

| Fault Over-Scale Level <sup>(1)</sup>                 | Above Over-Scale Selected                     |      | +1.0         |                      | mA      |

| Under-Scale Limit Resolution                          | Digital Select: 2.2-3.6mA                     |      | 0.2          |                      | mA      |

| Fault Under-Scale Level <sup>(1)</sup>                | Below Under-Scale Selected                    |      | -0.4         |                      | mA      |

| Output for Zero Input                                 |                                               |      |              |                      |         |

| Zero Error, Unadjusted                                | $V_{IN} = 0V$                                 |      | ±50          |                      | μA      |

| vs Temperature                                        |                                               |      | ±0.2         | ±1.5                 | μÂ/°C   |

| vs Loop-Supply Voltage, VLOOP                         | $V_{1,00P} = 7.5V$ to 24V                     |      | 0.02         |                      | μΑ/V    |

| vs Common-Mode Voltage                                | $V_{CM} = 0.2V$ to 3.5V                       |      | ±1           |                      | μΑ/V    |

| Adjustment Resolution, Zero Input                     |                                               |      | 1.8          |                      | μA/Step |

| Adjustment Range, Zero Input                          |                                               |      | ±4           |                      | mA      |

| Span <sup>(2)</sup>                                   | Span = $I_0/V_{IN}$                           |      |              |                      |         |

| Initial, Unadjusted                                   |                                               |      | ±1           |                      | %       |

| Drift (vs Temperature)                                |                                               |      | 40           |                      | ppm/°C  |

| Span Adjustment Resolution                            |                                               |      | 0.05         |                      | %       |

| Span Adjustment Range                                 |                                               |      |              |                      |         |

| PGA + Output Amplifier <sup>(3)</sup>                 | $R_{VI} = 6.34 k\Omega$                       | 49.3 |              | 3150                 | mA/V    |

| Nonlinearity, Ideal Input                             | Full-Scale V <sub>IN</sub> = 50mV             |      | 0.01         |                      | %       |

| PGA                                                   |                                               |      |              |                      |         |

| Autozeroing Internal Frequency                        |                                               |      | 6.5          |                      | kHz     |

| PGA Offset Voltage (RTI) <sup>(4)</sup>               | $V_{CM} = 1V$                                 |      | ±10          | ±50                  | μV      |

| vs Temperature                                        |                                               |      | ±0.02        |                      | μV/°C   |

| vs Supply Voltage, V <sub>S</sub>                     | $V_{S} = 4.5V$ to 5.5V                        |      | ±0.5         |                      | μV/V    |

| vs Common-Mode Voltage                                | $V_{CM} = 0.2V$ to 3.5V                       |      | 105          |                      | dB      |

| Common-Mode Input Range                               |                                               | 0.2  |              | V <sub>S</sub> – 1.5 | V       |

| Input Bias Current                                    |                                               |      | 50           | -                    | pА      |

| vs Temperature                                        |                                               |      | Doubles/10°C |                      | рА      |

| Input Offset Current                                  |                                               |      | 10           |                      | pA      |

| vs Temperature                                        |                                               |      | Doubles/10°C |                      | рА      |

# ELECTRICAL CHARACTERISTICS (Cont.)

### Boldface limits apply over the specified temperature range, $T_A$ = -40°C to +85°C.

At T<sub>A</sub> = +25°C, V<sub>PS</sub> = 24V, and Supertex DN2540 external depletion-mode FET transistor, unless otherwise noted, all voltages measured with respect to I<sub>RET</sub> pin.

| PARAMETER                                                                                                                                                                                                                                | CONDITIONS                                                                                | MIN                | ТҮР                                                                                   | МАХ                       | UNITS                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------|---------------------------|------------------------------------------|

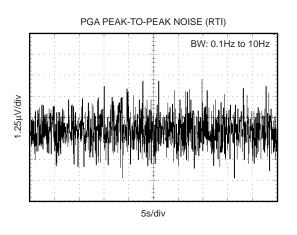

| PGA (Cont.)<br>Input Impedance: Differential<br>Input Impedance: Common-Mode<br>Voltage Noise, 0.1Hz to 10Hz<br>PGA Gain                                                                                                                 |                                                                                           |                    | 30    6<br>50    20<br>6                                                              |                           | GΩ    pF<br>GΩ    pF<br>μVp-p            |

| Gain Range Steps<br>Initial Error                                                                                                                                                                                                        | 6.25, 12.5, 25, 50, 100, 200, 400<br>Gain = 6.25, 12.5, 25, 50<br>G = 100, 200<br>G = 400 | 6.25               | ±0.5<br>±0.5<br>±0.8                                                                  | 400<br>±2.5<br>±3<br>±3.5 | V/V<br>%<br>%                            |

| vs Temperature<br>Output Voltage Range <sup>(5)</sup><br>Typical Operating Range<br>Capacitive Drive<br>Short-Circuit Current                                                                                                            | $R_{LOAD}$ = 6.34k $\Omega$ to $I_{RET}$ for 4-20mA XTR Output                            | 0.2                | ±30<br>0.5 to 2.5<br>200<br>+6/-9                                                     | 4.5                       | ppm/°C<br>∨<br>V<br>pF<br>mA             |

| ZERO OFFSET DACS<br>Zero-Code Output Level<br>RTO <sup>(6)</sup> of Current Amplifier<br>RTO <sup>(6)</sup> of PGA<br>Coarse DAC, 256 Steps<br>Adjustment Range                                                                          | $V_{CM}$ = 1V, $V_{IN}$ = 0V<br>$R_{V/I}$ = 6.34k $\Omega$<br>Relative to Zero-Code Level |                    | 4.116<br>522<br>7 Bits + Sign                                                         |                           | mA<br>mV                                 |

| RTO <sup>(6)</sup> of Current Amplifier<br>RTO <sup>(6)</sup> of PGA<br>Step Size<br>RTO <sup>(6)</sup> of Current Amplifier<br>RTO <sup>(6)</sup> of PGA<br>Linearity                                                                   |                                                                                           |                    | -3.77 to +3.77<br>-470 to +470<br>0.029<br>3.7<br>±0.5                                |                           | mA<br>mV<br>mA<br>mV<br>LSB              |

| Fine DAC, 256 Steps<br>Adjustment Range<br>RTO <sup>(6)</sup> of Current Amplifier<br>RTO <sup>(6)</sup> of PGA<br>Step Size                                                                                                             | Relative to Zero-Code Level                                                               |                    | 7 Bits + Sign<br>-236 to +236<br>-29.4 to +29.4                                       |                           | μA<br>mV                                 |

| RTO <sup>(6)</sup> of Current Amplifier<br>RTO <sup>(6)</sup> of PGA<br>Linearity<br>Noise, RTO <sup>(6)</sup>                                                                                                                           | f = 0.1Hz to 10Hz                                                                         |                    | 0.0018<br>0.23<br>±1<br>1.1                                                           |                           | mA<br>mV<br>LSB<br>μΑρ-ρ                 |

| CURRENT AMPLIFIER<br>Current Gain<br>Current Gain Drift                                                                                                                                                                                  |                                                                                           | 49                 | 50<br>10                                                                              | 51                        | A/A<br>ppm/°C                            |

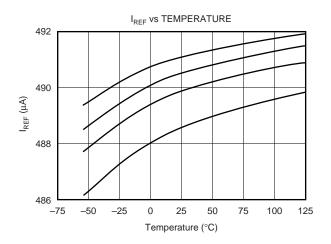

| CURRENT SOURCES, I <sub>REF1</sub> AND I <sub>REF2</sub><br>Zero-Code Output Level, Each<br>Coarse DAC, 256 Steps<br>Adjustment Range <sup>(7)</sup><br>Step Size<br>Fine DAC, 256 Steps<br>Adjustment Range <sup>(7)</sup><br>Step Size | $R_{SET} = 12.1 k\Omega$                                                                  | 480                | 493<br>7 Bits + Sign<br>-195 to +195<br>1.54<br>7 Bits + Sign<br>-12.2 to +12.2<br>96 | 510                       | μΑ<br>μΑ<br>μΑ<br>ηΑ                     |

| Linearity<br>Coarse<br>Fine<br>vs Temperature<br>Matching<br>vs Temperature<br>Compliance Voltage, Positive <sup>(5)</sup>                                                                                                               |                                                                                           | V <sub>S</sub> - 2 | $\pm 0.2$<br>$\pm 0.5$<br>$\pm 35$<br>$\pm 0.2$<br>$\pm 10$<br>V <sub>S</sub> - 1.5   |                           | LSB<br>LSB<br>ppm/°C<br>%<br>ppm/°C<br>V |

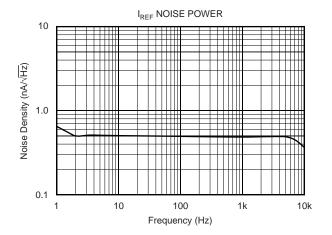

| Output Impedance Current Noise LINEARIZATION DAC                                                                                                                                                                                         | f = 0.1Hz to 10Hz                                                                         | vs-z               | 0.015                                                                                 |                           | ΜΩ<br>μΑp-p                              |

| LINEARIZATION DAC<br>Linearization Range, 256 Steps<br>Max Linearization Coefficient<br>Step Size                                                                                                                                        | $\Delta I_{REF} / \Delta V_{IN}, R_{LIN} = 15.8 k\Omega$                                  |                    | 8 Bits<br>0.99<br>3.9                                                                 |                           | μΑ/mV<br>nA/mV                           |

| SUB-REGULATOR, V <sub>S</sub><br>Voltage<br>vs Temperature                                                                                                                                                                               | Supply Voltage for XTR                                                                    | 4.8                | 5.1<br>±50                                                                            | 5.4                       | V<br>ppm/°C                              |

| vs Loop-Supply Voltage                                                                                                                                                                                                                   | $V_{LOOP} = 7.5V$ to 24V                                                                  |                    | ±0.03                                                                                 |                           | mV/V                                     |

# **ELECTRICAL CHARACTERISTICS (Cont.)**

### Boldface limits apply over the specified temperature range, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ .

At  $T_A = +25^{\circ}$ C,  $V_{PS} = 24$ V, and Supertex DN2540 external depletion-mode FET transistor, unless otherwise noted, all voltages measured with respect to  $I_{RET}$  pin.

| PARAMETER                                     | CONDITIONS                                                            | MIN                | ТҮР            | MAX                  | UNITS          |

|-----------------------------------------------|-----------------------------------------------------------------------|--------------------|----------------|----------------------|----------------|

| OVER- AND UNDER-SCALE LIMITING                |                                                                       |                    |                |                      |                |

| Over-Scale DAC: 16 Steps                      |                                                                       |                    | 4              |                      | Bits           |

| Adjustment Range                              |                                                                       |                    |                |                      |                |

| RTO <sup>(6)</sup> of Current Amplifier       | $R_{VI} = 6.34 k\Omega$                                               |                    | 20.7 to 28.1   |                      | mA             |

| RTO <sup>(6)</sup> of PGA                     |                                                                       |                    | 2.625 to 3.563 |                      | V              |

| Step Size                                     |                                                                       |                    |                |                      |                |

| RTO <sup>(6)</sup> of Current Amplifier       |                                                                       |                    | 0.49           |                      | mA             |

| RTO <sup>(6)</sup> of PGA                     |                                                                       |                    | 62.5           |                      | mV             |

| Accuracy                                      |                                                                       |                    | ±10            |                      | %              |

| Under-Scale DAC: 8 Steps                      |                                                                       |                    | 3              |                      | Bits           |

| Adjustment Range                              |                                                                       |                    |                |                      |                |

| RTO <sup>(6)</sup> of Current Amplifier       | $R_{VI} = 6.34 k\Omega$                                               |                    | 2.17 to 3.55   |                      | mA             |

| RTO <sup>(6)</sup> of PGA                     |                                                                       |                    | 275 to 450     |                      | mV             |

| Step Size                                     |                                                                       |                    | 210 10 400     |                      | IIIV           |

| RTO <sup>(6)</sup> of Current Amplifier       |                                                                       |                    | 0.195          |                      | mA             |

| RTO <sup>(6)</sup> of PGA                     |                                                                       |                    | 25             |                      | mV             |

|                                               |                                                                       |                    | 25<br>±5       |                      | %              |

| Accuracy                                      |                                                                       |                    | ±υ             |                      | 70             |

| VOLTAGE REFERENCE, V <sub>REF</sub>           |                                                                       |                    |                |                      |                |

| Internal Bandgap                              |                                                                       |                    | 1.193          |                      | V              |

| vs Temperature                                |                                                                       |                    | ±5             | ±50                  | ppm/°C         |

| UNCOMMITTED OP AMP                            |                                                                       |                    |                |                      |                |

| Input                                         |                                                                       |                    |                |                      |                |

| Offset Voltage                                | $V_{CM} = 2V$                                                         |                    | ±2             |                      | mV             |

| vs Temperature                                |                                                                       |                    | ±3             |                      | μV/°C          |

| vs Common-Mode Voltage                        |                                                                       |                    | 90             |                      | dB             |

| Open-Loop Gain                                |                                                                       |                    | 110            |                      | dB             |

| Common-Mode Input Range                       |                                                                       |                    | 0 to 3.5       |                      | V              |

| Output Voltage Range                          | $R_{\rm L} = 10 k\Omega$ to $V_{\rm S}/2$                             | 0.2                |                | V <sub>S</sub> – 0.2 | V              |

| DIGITAL INPUT/OUTPUT                          |                                                                       |                    |                | -                    |                |

| Logic Family                                  |                                                                       |                    | CMOS           |                      |                |

| Logic Levels                                  |                                                                       |                    | 00000          |                      |                |

| 0                                             |                                                                       | 0                  |                | 0.8                  | V              |

| V <sub>IL</sub><br>V <sub>IH</sub>            |                                                                       | 3.5                |                | V <sub>S</sub>       | v              |

|                                               | L _ 200u A                                                            | 5.5                |                | 0.4                  | v              |

| V <sub>OL</sub>                               | I <sub>OL</sub> = 300μA<br>I <sub>OH</sub> = -300μA                   | V 1                |                | 0.4                  | v              |

| V <sub>OH</sub><br>Input Current              | i <sub>OH</sub> = -300μA                                              | V <sub>S</sub> – 1 |                |                      | v              |

| I <sub>IH</sub> (CS1)                         | 3.5 < V <sub>IN</sub> < V <sub>S</sub>                                | -200               | -120           | 10                   | ۸              |

|                                               | $3.3 \leq v_{\rm IN} \leq v_{\rm S}$                                  | -200               | -120<br>-6     | 10                   | μA             |

|                                               | $0 < V_{IN} < 0.8$                                                    | -20<br>-20         | 6              | 10                   | μA<br><b>A</b> |

| I <sub>IH</sub> , I <sub>IL</sub> (SCLK, DIO) | $0 < V_{IN} < V_{S}$                                                  | -20                | 0-             | 10                   | μΑ             |

| INTERNAL OSCILLATOR                           |                                                                       |                    |                |                      |                |

| Frequency, f <sub>OSC</sub>                   |                                                                       |                    | 210            |                      | kHz            |

| TEMPERATURE RANGE                             |                                                                       |                    |                |                      |                |

| Specification                                 |                                                                       | -40                |                | +85                  | °C             |

| Operating                                     |                                                                       | -55                |                | +125                 | °C             |

| $\theta_{\rm JA}$ , Junction to Ambient       |                                                                       |                    | 100            |                      | °C/W           |

|                                               |                                                                       |                    |                |                      |                |

| Voltage Range                                 | with Supertex DN2540                                                  | 7.5                |                |                      | V              |

| Quiescent Current                             | $R_{SET}$ Open, $L_{IN}Reg = 0$ , No Sensor Current <sup>(8)(9)</sup> | 1                  | 0.5            |                      | mA             |

|                                               | SEI Open, ENNEG - 0, NO DENSOI CUITEII((*)(*)                         |                    | 0.0            |                      | 1117           |

NOTES: (1) Over-scale and under-scale complies with NAMUR NE43 recommendation. (2) Span adjustment is determined by PGA gain and sensor excitation. (3) Span can be digitally adjusted in three ways: PGA gain, current reference Coarse, and current reference Fine. (4) RTI = Referred to Input. (5) Current source output voltage measured with respect to  $I_{RET}$ . (6) RTO = Referred to Output. (7) Excitation DAC range sufficient to adjust span fully between PGA gain steps. (8) Output current into external circuitry is limited by an external MOS power FET. (9) Measured with over- and under-scale limits disabled.

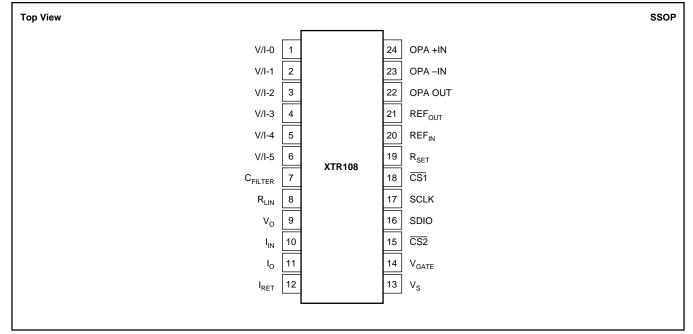

#### **PIN CONFIGURATION**

#### **PIN ASSIGNMENTS**

| PIN                 | NAME                                            | FUNCTION                                                             |  |  |  |  |  |

|---------------------|-------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| V/I-0               | MUX Input Channel 0 and/or I <sub>REF</sub> Out | MUX Input to PGA and/or IREF to Sensor                               |  |  |  |  |  |

| V/I-1               | MUX Input Channel 1 and/or IREF Out             | MUX Input to PGA and/or IREF to Sensor                               |  |  |  |  |  |

| V/I-2               | MUX Input Channel 2 and/or IREF Out             | MUX Input to PGA and/or IREF to Sensor                               |  |  |  |  |  |

| V/I-3               | MUX Input Channel 3 and/or IREF Out             | MUX Input to PGA and/or IREF to Sensor                               |  |  |  |  |  |

| V/I-4               | MUX Input Channel 4 and/or IREF Out             | MUX Input to PGA and/or IREF to Sensor                               |  |  |  |  |  |

| V/I-5               | MUX Input Channel 5 and/or I <sub>REF</sub> Out | MUX Input to PGA and/or IREF to Sensor                               |  |  |  |  |  |

| C <sub>FILTER</sub> | Filter Capacitor                                | Filter to Reduce Chopper Noise in Autozeroing PGA                    |  |  |  |  |  |

| R <sub>LIN</sub>    | Linearization                                   | Linearization Range Adjustment Resistor                              |  |  |  |  |  |

| Vo                  | PGA Output                                      | PGA Amplified Output of Differential Sensor Input                    |  |  |  |  |  |

| I <sub>IN</sub>     | Current Input                                   | Input to Output Current Amplifier                                    |  |  |  |  |  |

| lo                  | Output Current                                  | 4-20mA Current for Output Loop                                       |  |  |  |  |  |

| IRET                | Return Current                                  | Return for All External Circuitry Current                            |  |  |  |  |  |

| Vs                  | Voltage Regulator                               | Supply Voltage for XTR and External Circuitry, If Used               |  |  |  |  |  |

| V <sub>GATE</sub>   | Gate Voltage                                    | Gate Voltage for External MOSFET Transistor                          |  |  |  |  |  |

| CS2                 | Chip Select 2                                   | Select for XTR Serial Port to External EEPROM (Output from XTR Only) |  |  |  |  |  |

| SDIO                | Serial Data Input/Output                        | Serial Data Input or Output                                          |  |  |  |  |  |

| SCLK                | Serial Clock                                    | Serial Clock                                                         |  |  |  |  |  |

| CS1                 | Chip Select 1                                   | Select for External µC Serial Port (Input to XTR Only)               |  |  |  |  |  |

| R <sub>SET</sub>    | Resistor for Reference                          | Sets Current Reference                                               |  |  |  |  |  |

| REFIN               | Voltage Reference Input                         | Voltage Reference Input to XTR                                       |  |  |  |  |  |

| REFOUT              | Voltage Reference Output                        | Voltage Reference Output from Internal Bandgap                       |  |  |  |  |  |

| OPA OUT             | Uncommitted Op Amp Output                       | Uncommitted Op Amp Output                                            |  |  |  |  |  |

| OPA –IN             | Uncommitted Op Amp Negative Input               | Uncommitted Op Amp Negative Input                                    |  |  |  |  |  |

| OPA +IN             | Uncommitted Op Amp Positive Input               | Uncommitted Op Amp Positive Input                                    |  |  |  |  |  |

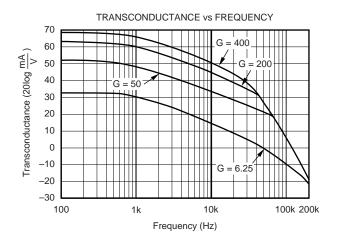

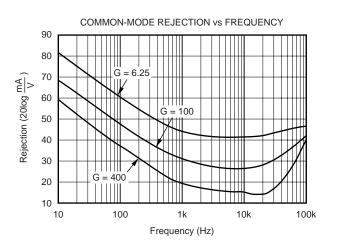

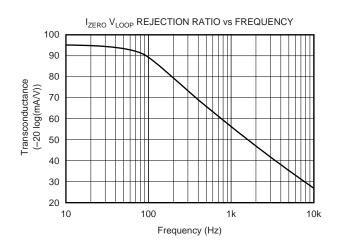

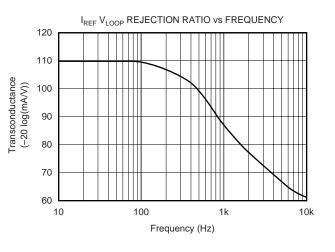

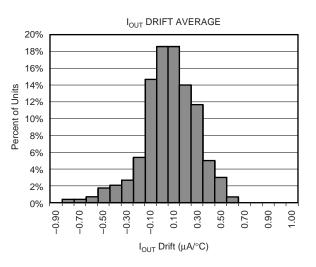

# **TYPICAL CHARACTERISTICS**

At T<sub>A</sub> = +25°C, V+ = 24V, unless otherwise noted. R<sub>VI</sub> = 6.34k $\Omega$ .

### **TYPICAL CHARACTERISTICS (Cont.)**

At T<sub>A</sub> = +25°C, V+ = 24V, unless otherwise noted. R<sub>VI</sub> = 6.34k\Omega.

$\mathsf{I}_{\mathsf{ZERO}}$  CURRENT NOISE POWER 100 Noise Density (nA/VHz) 10 1 1 10 100 10k 1k Frequency (Hz)

## **TYPICAL CHARACTERISTICS (Cont.)**

At T\_A = +25°C, V+ = 24V, unless otherwise noted. R\_{VI} = 6.34k\Omega.

### **OVERVIEW**

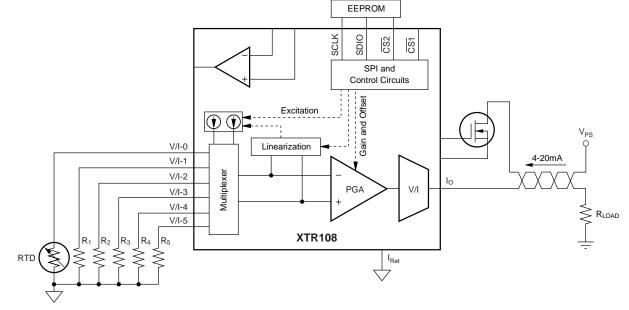

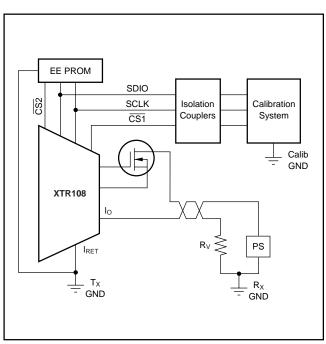

The XTR108 is a 4-20mA current-loop transmitter that allows the user to digitally adjust the gain, offset, and linearity correction of the analog output to calibrate the sensor. The digital data for adjustment are stored in an external EEPROM device.

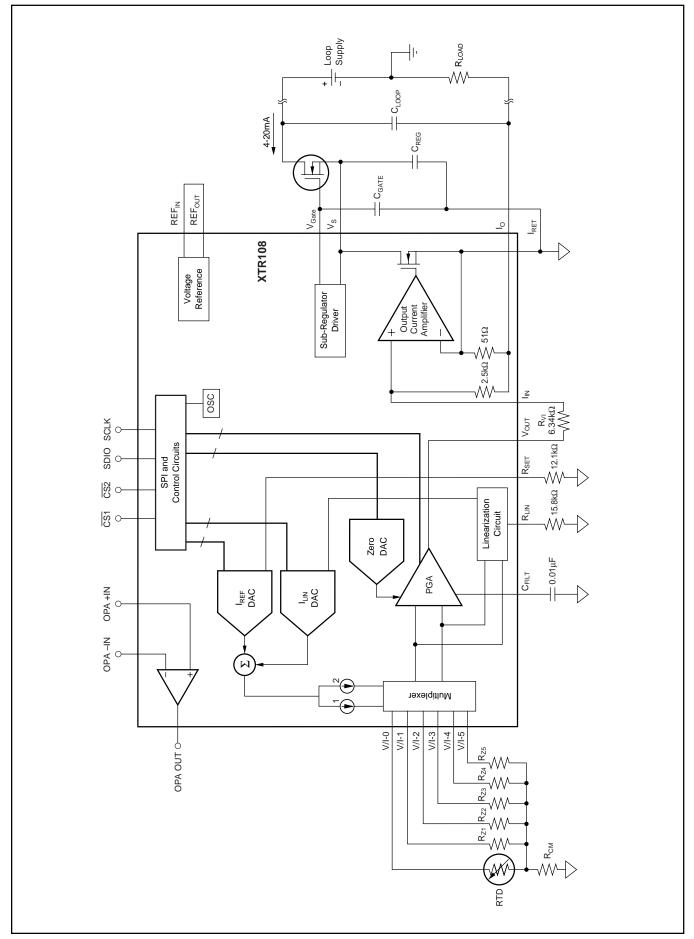

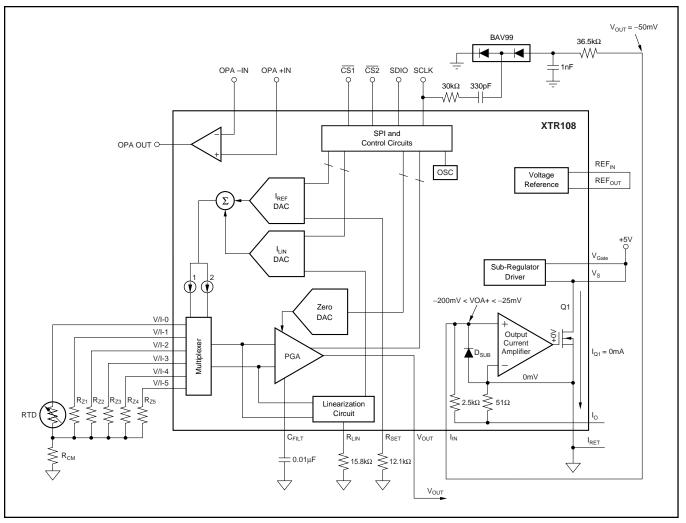

The analog signal path is composed of a compound multiplexer (MUX), programmable gain instrumentation amplifier (PGA), and an output current amplifier. Analog support functions include digitally controlled current sources for sensor excitation, PGA offset control, linearization, voltage reference, and voltage regulator.

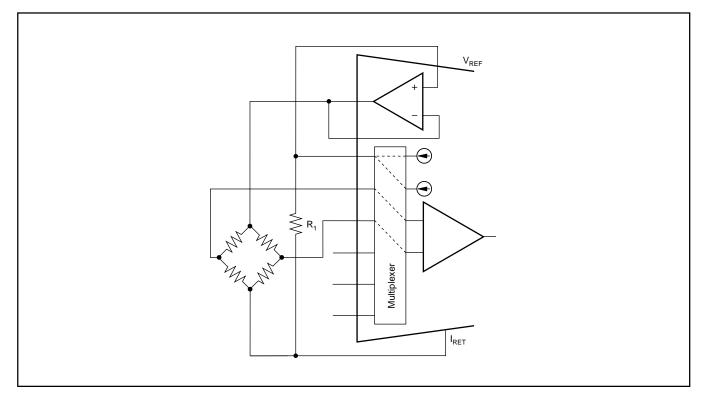

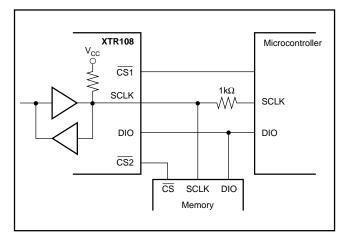

The digital interface communicates with external devices for calibration and to store the resultant data in an SPI compatible EEPROM. A complete system is shown in Figure 1. The XTR108 serial interface is SPI compatible and only requires four connections to the calibration controller: a serial clock (SCLK), a serial data line (SDIO), a chip select line ( $\overline{\text{CS1}}$ ), and a ground sense line. All logic signals to the XTR108 must be referenced to the potential of the ground sense line ( $I_{\text{RET}}$  pin on the XTR108).

Within this entire system there may exist three different "GND" voltage levels. In addition, the voltage difference between the  $I_{RET}$  and  $I_O$  potential will depend on the output current level. It is not certain that the "GND" potential of the calibration system will be at the same potential of either the  $I_{RET}$  or  $I_O$  potential, and therefore the isolation couplers are shown in Figure 1. All voltages specified for the XTR108 are with reference to the  $I_{RET}$  pin.

FIGURE 1. Complete System Level Configuration with Three Unique Ground Voltage Levels.

The XTR108 also needs to communicate with the external EEPROM device independently from the calibration controller to retrieve the calibration constants during normal operation. The XTR108 provides a second chip select function  $(\overline{CS2})$  for the EEPROM device to facilitate this communication.

### THEORY OF OPERATION

#### REFERENCE

The XTR108 has an on-board precision bandgap voltage reference with output at pin 21 (REF<sub>OUT</sub>). The value of the reference is factory-trimmed to 1.193V, with a typical temperature drift of 5ppm/°C. Pins 21 (REF<sub>OUT</sub>) and 20 (REF<sub>IN</sub>) must be connected together to use the internal reference.

External circuitry, such as a voltage excited sensor or an Analog-to-Digital Converter (ADC), can be connected to the  $\text{REF}_{\text{OUT}}$  pin. The unbuffered  $\text{REF}_{\text{OUT}}$  is capable of sourcing current but not sinking.

If the application necessitates, an external reference can be connected to the XTR108  $\text{REF}_{\text{IN}}$  pin, as long as the reference does not exceed 1.4V. The  $\text{REF}_{\text{IN}}$  pin has a high input impedance with the input current not exceeding a few nanoamps.

#### INPUT MULTIPLEXER

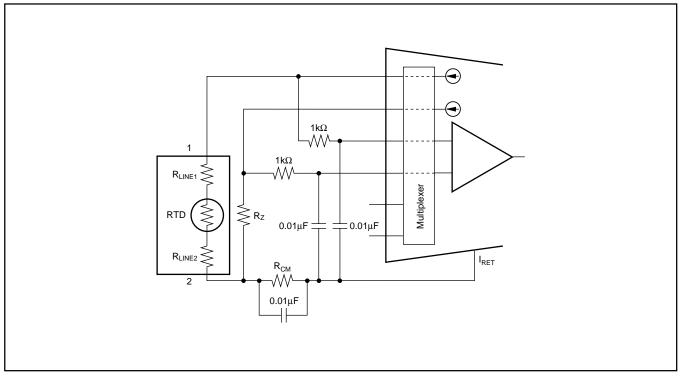

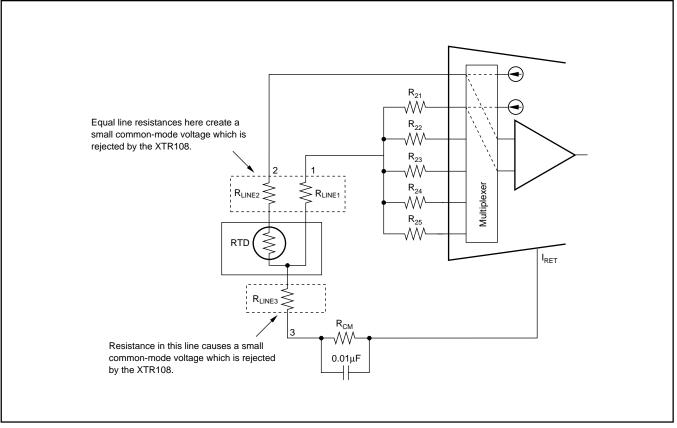

The XTR108 input multiplexer is a full 6 by (2+2) crosspoint switch. The current references and PGA inputs can be independently connected to any of the six external pins, including simultaneous connections to the same pin. This allows a great flexibility in the sensor excitation and input configuration. The input pins must not be driven below the  $I_{RET}$  potential or above V<sub>S</sub>.

See Figure 2 for an RTD sensor connected to pin  $V_{\rm IN}0$  with both  $I_{\rm REF}$  supplied and PGA  $V_{\rm IN+}$  sensed at that pin. The other five input pins are used for a bank of  $R_Z$  resistors that can be selected during the calibration process for a particular measurement range.

#### PROGRAMMABLE GAIN INSTRUMENTATION AMPLIFIER

The programmable gain instrumentation amplifier has seven voltage-gain settings in binary steps from 6.25 V/V to 400V/V. The input common-mode range of the PGA is 0.2V to 3.5V above the I<sub>RET</sub> potential.

Normally, in the application for 4-20mA transmitters, the PGA output voltage range should be set to  $V_{ZERO} = 0.5V$  and  $V_{FS} = 2.5V$ . Connecting a resistor ( $R_{VI} = 6.34k\Omega$ ) between pin 9 ( $V_0$ ) and pin 10 ( $I_{IN}$ ) converts this voltage to the signal for the output amplifier that produces a 4-20mA scale current output. In this mode, the PGA voltage gain converts to an overall transconductance in the range of 50mA/V to 3200mA/V (approximately). Table I shows the gain to transconductance relationship.

| VOLTAGE GAIN                            | 6.25 | 12.5 | 25  | 50  | 100 | 200  | 400  |

|-----------------------------------------|------|------|-----|-----|-----|------|------|

| OUTPUT TRANSCONDUCTANCE                 | 49   | 99   | 197 | 394 | 789 | 1577 | 3155 |

| FULL-SCALE DIFFERENTIAL V <sub>IN</sub> | 320  | 160  | 80  | 40  | 20  | 10   | 5    |

TABLE I. PGA Gain, Corresponding Loop Transductance and Input Full-Scale Differential Voltage. If over-scale and under-scale limiting is disabled, the PGA can be used with rail-to-rail voltage output, for example, in applications that require a 0.5V to 4.5V voltage scale.

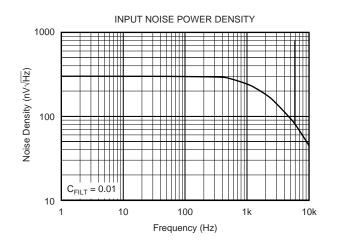

The PGA uses advanced auto-zero circuit techniques to achieve high DC precision, and reduce mismatches and errors within the chip such as input offset, offset temperature drift, and lowfrequency noise (see the input noise typical characteristic).

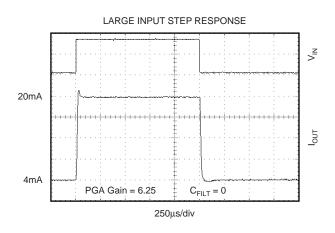

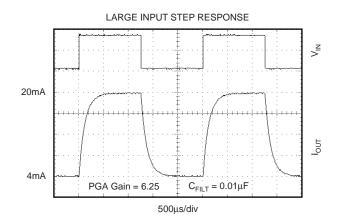

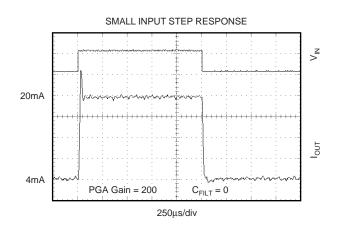

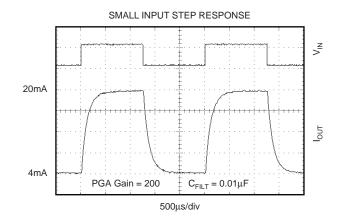

The basic clock frequency of the auto-zero loop is about 6.5kHz. Due to the switching nature of the auto-zero circuit, the output of the PGA can have a noticeable clock feed-through ripple in higher gains. This noise can be reduced by the addition of a 0.01 $\mu$ F capacitor between pin 7 (C<sub>FILTER</sub>) and the local ground, pin 12 (I<sub>RET</sub>). This creates a one-pole low-pass filter with –3dB frequency at about 1.5kHz. If wider bandwidth or faster settling time is needed, the C<sub>FILTER</sub> can be reduced or eliminated at the expense of higher glitch amplitude at the output. Please refer to the typical step response traces for settling time comparisons.

#### ZERO DACS

Two output-referred, 8-bit Digital-to-Analog Converters (DACs) (coarse and fine with a pedestal) set the zero level of the PGA output. They allow setting a desired zero-scale output level and compensate the initial offset at the PGA input due to the sensor and resistor mismatches, sensor non-idealities, etc. Both coarse and fine DACs are bidirectional and allow the output level to be set above or below a preset pedestal.

Output signals of the DACs,  $I_{Z \text{ COARSE}}$  and  $I_{Z \text{ FINE}}$ , are summed with the pedestal,  $I_{Z \text{ PROGRAM}}$ . Each of the DACs has 8-bit resolution (256 steps) with 4-bit overlap between the coarse and fine DACs. This means that one LSB of the coarse DAC is equal to 16 fine LSBs, and the full-scale range of the fine DAC is equal to 16 coarse LSBs. This effectively produces 12-bit adjustment resolution.

This overlap allows the user to set pre-calculated values before the calibration, using the coarse DAC only and adjust the zero output level with the fine DAC during the calibration process see Table II for the equations for calculating the value of the output when zero differential voltage is applied at the PGA input. For the adjustment range, LSB sizes, and linearity values of the Zero DACs, please refer to the electrical characteristics table.

Note that a DAC can be set to a value that produces an output below the under-scale level. In this case, the under-scale limit will prevent the output from getting to the desired value. The value of the minimum scale should not be set so low that the PGA voltage output,  $V_0$ , goes below its specified range of 0.2V from  $I_{RET}$ .

# ADJUSTABLE OVER-SCALE AND UNDER-SCALE LIMITING CIRCUIT

The XTR108 incorporates circuitry to set adjustable limits at the output in cases when the sensor signal goes above or below its range. There are 16 levels for over-scale limit adjustment (4-bit DAC) and 8 levels for the under-scale (3-bit DAC).

FIGURE 2. XTR108 Internal Block Diagram.

|                             | VOLTAGE REFERRED TO V <sub>O</sub> PIN<br>WITH RESPECT TO I <sub>RET</sub>               | CURRENT REFERRED TO I <sub>OUT</sub> PIN                                                 |

|-----------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| OVERALL                     | V <sub>ZERO</sub> = V <sub>Z PROGRAM</sub> + V <sub>Z COARSE</sub> + V <sub>Z FINE</sub> | I <sub>ZERO</sub> = I <sub>Z PROGRAM</sub> + I <sub>Z COARSE</sub> + I <sub>Z FINE</sub> |

| PROGRAM                     | $V_{ZPROGRAM} = \frac{3.5V_{REF}}{8}$                                                    | $I_{ZPROGRAM} = \frac{175V_{REF}}{8R_{VI}}$                                              |

| COARSE DAC                  | $V_{Z \text{ COARSE}} = \frac{V_{\text{REF}}}{80} \bullet \frac{N_{13}}{4}$              | $I_{Z \text{ COARSE}} = \frac{5V_{\text{REF}}}{8R_{\text{VI}}} \bullet \frac{N_{13}}{4}$ |

| FINE DAC                    | $V_{ZFINE} = \frac{V_{REF}}{80} \bullet \frac{N_{12}}{64}$                               | $I_{Z  FINE} = \frac{5V_{REF}}{8R_{VI}} \bullet \frac{N_{12}}{64}$                       |

| NOTE: $N_{13}$ and $N_{12}$ | are assigned decimal values of registers 13 and 12, respectively.                        | ·                                                                                        |

TABLE II. Equations for Calculating Zero Output.

The circuit is designed for compliance with NAMUR NE43 recommendation for sensor interfaces. The limit levels are listed in Tables VII and VIII. Because of the large step sizes, units that use this feature should be checked if the value is critical. The under-scale limit circuit will override the Zero DAC level if it is set lower and there is not enough sensor offset at the PGA input.

It may be necessary to disable limiting if the XTR108 is used in applications other than a 4-20mA transmitter, where the PGA output is between 0.5V and 4.5V.

#### SENSOR FAULT DETECTION CIRCUIT

To detect sensor burnout and/or short, a set of four comparators is connected to the inputs of the PGA. If any of the inputs are taken outside of the PGA's common-mode range, the corresponding comparator sets a sensor fault flag that causes the PGA output to go either to the upper or lower error limit. The state of the fault condition can be read in the digital form from register 3. The direction of the analog output is set according to the "Alarm Configuration Register" (see Table X). The level of the output is produced as follows: if the over-scale/under-scale limiting is enabled, the error levels are: over-scale limit +2LSBs of the over-scale DAC, about 1mA referred to I<sub>OUT</sub> or 0.125V referred to V<sub>O</sub>, of under-scale limit -2LSBs of the under-scale DAC, about 0.4mA referred to  $I_{OUT}$  or 0.05V referred to  $V_{O}$ . If the overscale/under-scale limiting is disabled, the PGA output voltage will go to within 150mV of either positive or negative supply ( $V_S$  or  $I_{RET}$ ), depending on the alarm configuration bit corresponding to the error condition.

#### **OUTPUT CURRENT AMPLIFIER + Rvi RESISTOR**

To produce the 4-20mA output, the XTR108 uses a current amplifier with a fixed gain of 50A/A. The voltage from the PGA is converted to current by the external resistor,  $R_{VI}$ . Pin  $I_{RET}$ , the common potential of the circuit (substrate and local ground), is connected to the output and inverting input of the amplifier. This allows collecting all external and internal supply currents, sensor return current, and leakage currents from the different parts of the system and accounting for them in the output current. The current from  $R_{VI}$  flows into the pin  $I_{IN}$  that is connected to the noninverting input and therefore, is at ground potential as well. The ratio of two

matched internal resistors determines a current gain of this block. Note that the  $I_{\rm OUT}$  pin is always biased below the substrate potential.

#### EXCITATION CURRENT DACS AND R<sub>SET</sub> RESISTOR

Two matched adjustable reference current sources are available for sensor excitation. The defining equations are given in Table III. Both current sources are controlled simultaneously by the coarse and fine DACs with a pedestal.

The external resistor  $R_{SET}$  is used to convert the REF voltage into the reference current for the sensor excitation DACs. The total current output of the DACs is split, producing two references:  $I_{REF1}$  and  $I_{REF2}$ . Both of the current references match very closely over the full adjustment range without mismatched differential steps. Both current reference outputs must be within the compliance range, i.e.: one reference cannot be floated since it will change the value of the other current source.

The recommended value of  $R_{SET}$  is  $12.1k\Omega$  for use with  $100\Omega$  RTD sensors. This generates  $I_{REF1,\,2} = 492\mu A$  currents when both coarse and fine DACs are set to zero. The value of the  $R_{SET}$  resistor can be increased if lower reference currents are required, i.e.: for  $1000\Omega$  RTD or a bridge sensor.

|                                                            | REFERENCE CURRENT                                                                         |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| OVERALL                                                    | $I_{REF1, 2} = I_{REF PROGRAM} + I_{REF COARSE} + I_{REF FINE}$                           |

| PROGRAM                                                    | $I_{\text{REF PROGRAM}} = \frac{5V_{\text{REF}}}{R_{\text{SET}}}$                         |

| COARSE DAC                                                 | $I_{\text{REF COARSE}} = \frac{V_{\text{REF}}}{R_{\text{SET}}} \bullet \frac{N_{11}}{64}$ |

| FINE DAC                                                   | $I_{\text{REFFINE}} = \frac{V_{\text{REF}}}{R_{\text{SET}}} \bullet \frac{N_{10}}{1024}$  |

| NOTE: N <sub>11</sub> and N <sub>10</sub><br>respectively. | are the decimal values of registers 11 and 10,                                            |

TABLE III. Equations for Calculating the Values of Each Reference Current.

Similar to the Zero DACs, the outputs of the fine and coarse DAC are summed together with the pedestal  $I_{REF PROGRAM}$ . Each of the excitation DACs has 8-bit resolution (256 steps) with 4-bit overlap between the coarse and the fine. This

means that one LSB of the coarse DAC is equal to 16 fine LSBs, and the full-scale range of the fine DAC is equal to 16 coarse LSBs. This effectively produces 12-bit adjustment resolution. This allows the user to set pre-calculated values before the calibration, using the coarse DAC only and adjust the reference current output level with the fine DAC during the calibration process.

#### LINEARIZATION CIRCUIT AND RLIN RESISTOR

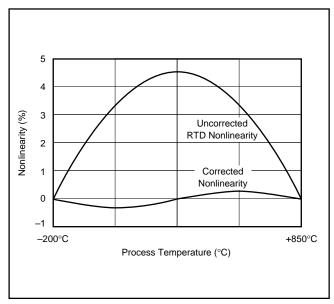

The XTR108 incorporates circuitry for correcting a secondorder sensor nonlinearity. A current proportional to the voltage at the input of the PGA is added to the sensor excitation. The R<sub>LIN</sub> resistor is used to convert this voltage into current. By appropriately scaling this current using the linearization DAC, parabolic sensor nonlinearity can be improved by up to a 40:1 ratio, as shown in Figure 3. The linearization coefficient (ratio of the reference current change to the input voltage) is expressed in  $\mu$ A/mV as follows:

$$G_{LIN} = \frac{\Delta I_{REF}}{V_{IN}} \bullet \frac{N_{14}}{16 \bullet R_{LIN}}$$

where  $N_{14}$  is the decimal value from register 14.

The recommended value of the resistor is  $15.8 \mathrm{k} \Omega$ , for use with 100 $\Omega$  RTD sensors. This value produces a full-scale linearization coefficient of about 1mA/V. Please see the section below on using the XTR108 with an RTD temperature sensor. If the sensor excitation is scaled down by increasing the value of  $R_{\rm SET}$ , the value of  $R_{\rm LIN}$  should be scaled proportionally.

FIGURE 3. Pt100 Nonlinearity Correction Using the XTR108.

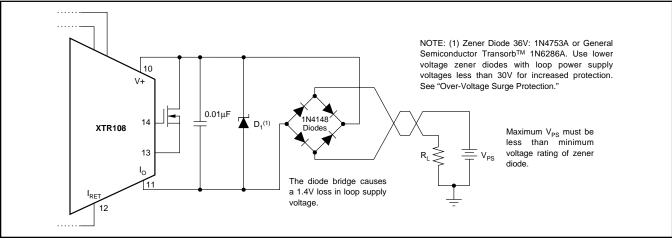

#### SUB-REGULATOR WITH EXTERNAL MOSFET

The XTR108 is manufactured using a low-voltage CMOS process with maximum supply voltage limited to 5.5V. For applications in a 4-20mA current loop, a special sub-regulator circuit is incorporated in the device that requires an external

n-channel depletion-mode MOS transistor and three capacitors, see Figure 2.

A number of third-party suppliers make n-channel depletion-mode MOSFETs. A list of devices tested by Texas Instruments, Inc. is shown in Table IV with the capacitor values recommended for those devices.

| MANUFACTURER | MOSFET MODEL                     | C <sub>GATE</sub> VALUE |

|--------------|----------------------------------|-------------------------|

| Supertex     | DN2535, DN2540<br>DN3535, DN3525 | 220pF<br>1000pF         |

| Siliconix    | ND2012, ND2020                   | 220pF                   |

| Infineon     | BSP149                           | 1000pF                  |

TABLE IV. Recommended Gate Capacitor Values For Selected MOSFETs.

The capacitors  $C_{LOOP}$  (0.01µF),  $C_{REG}$  (2.2µF), and  $C_{GATE}$  are required for the regulator loop stability and supply bypass. They should be placed in close proximity to the XTR108 on the PCB. An additional 1µF capacitor may be used to bypass the supply of an EEPROM chip.

If a MOSFET other than those listed in Table IV is used, the value of  $C_{GATE}$  should be adjusted such that there is no overshoot of  $V_S$  during power-up and supply glitches. Any  $V_S$  overshoot above 7.5V may damage the XTR108 or deteriorate its performance.

#### LOOP VOLTAGE

The XTR108 transmitter minimum loop voltage can somewhat be effected by the choice of the external MOSFET. The devices are tested to 7.5V compliance with Supertex DN2540; choosing other MOSFETs can change this value slightly.

The maximum loop voltage is limited by the power dissipation on the MOSFET as well as its breakdown voltage. Possible ambient temperatures and the power dissipation should be taken into account when selecting the MOSFET package. The external MOSFET can dissipate a considerable amount of power when running at high loop supply. For example, if  $V_{LOOP} = 24V$  and  $I_{OUT} = 20mA$ , the DC power dissipated by the MOSFET is:

$$P_{\text{MOSFET}} = I_{\text{OUT}} (V_{\text{LOOP}} - V_{\text{S}}) = 380 \text{m}\Omega$$

For a SOT-89 package soldered on an FR5 board, this will cause a 30°C rise in the temperature. The power dissipation gets significantly higher when the circuit is driven into an over-scale condition. Therefore, special attention should be paid to removing the heat from the MOSFET, especially with small-footprint packages such as SOT-89 and TO-92. Please follow manufacturer's recommendations about the package thermal characteristics and board mounting.

#### UNCOMMITTED OP AMP

For added flexibility in various applications, the XTR108 has an on-chip uncommitted operational amplifier. The op amp has rail-to-rail output range. The input range extends to  $I_{RET}$  potential.

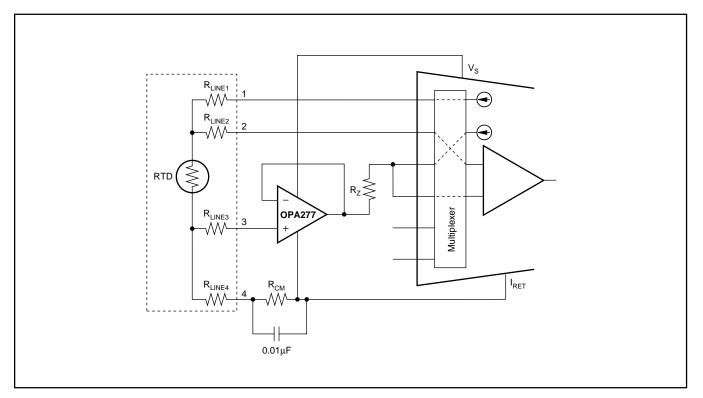

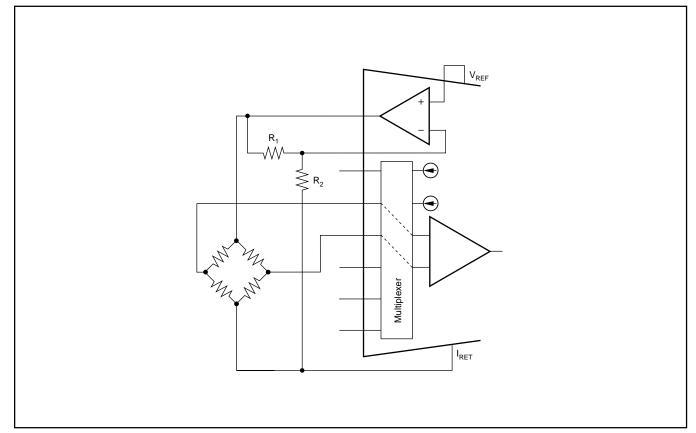

The uncommitted amplifier can be used for a variety of purposes, such as voltage sensor excitation, buffering the REF<sub>OUT</sub> pin, four-wire RTD connection, or sensing the bridge voltage for temperature compensation.

#### **POWER-GOOD/POWER-ON RESET**

In case of a supply brownout condition or short interruption, the XTR108 power-good detection circuit will initiate a chip reset that will cause all registers to be reset to 0's and a cycle of EEPROM read to begin. The circuit generates a reset if  $V_S$  droops below 1.5V and then recovers up to the normal level.

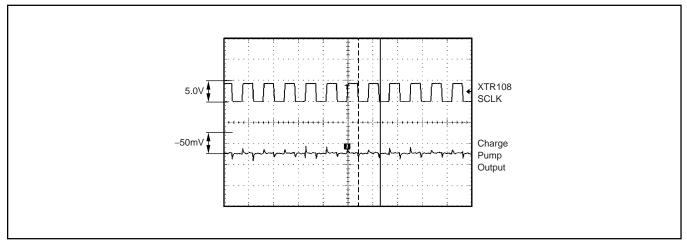

#### USING THE XTR108 IN VOLTAGE OUTPUT MODE

The XTR108 can be used not only in 4-20mA current loops, but also as a low-power, single-supply, "smart" sensorconditioning chip with voltage output. In this mode, the  $I_{RET}$  pin must be connected below ground (-200mV <  $I_{RET}$  < -25mV). This negative voltage is required to overcome the input offset voltage of the output current amplifier and prevent it from turning on and drawing excessive current. An application circuit that generates this negative voltage using the XTR108 clock output and a simple charge pump is shown in the application section.

The sub-regulator with an external MOSFET may or may not be used. If the circuit is powered externally, the supply voltage must be in the range of  $5V \pm 0.5V$ .

### **CONTROL REGISTERS**

Table V shows the registers that control the analog functions of the XTR108.

#### **DESCRIPTION OF CONTROL REGISTERS**

#### Address = 0: Control Register 1

If the RST bit is set to '1' in a write operation, all the registers in the XTR108 will be returned to their power-on reset condition. The RST bit will always read as a '0'. CSE, the checksum error bit, is read only and will be set to '1' if a checksum error has been detected. This bit is cleared by a reset operation or by detection of a valid checksum. The remaining bits are reserved and must be set to '0'.

#### Address = 3: Fault Status Register

This register is a read-only register. If the input voltage to the PGA exceeds the linear range of operation, the XTR108 will indicate this error condition (typically caused by a sensor fault) by setting the under-scale or over-scale error level depending on the state of the Alarm Configuration Register (Address = 7). Information on the nature of the fault may be read in digital form from this register, as shown in Table VI. The remaining bits will be set to '0'.

| BIT | FAULT MODE                             |

|-----|----------------------------------------|

| F0  | Negative Input Exceeds Positive Limit. |

| F1  | Negative Input Exceeds Negative Limit. |

| F2  | Positive Input Exceeds Positive Limit. |

| F3  | Positive Input Exceeds Negative Limit. |

TABLE VI. Register 3, Fault Status Register.

| Instruction | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |                   |                                         |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-------------------|-----------------------------------------|

| Read/Write  | R/W | 0   | 0   | 0   | A3  | A2  | A1  | A0  | Read/Write Op     | eration                                 |

| EPROM Mode  | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | Assert CS2        |                                         |

| L           |     |     | I   |     |     |     |     |     | J Ignore Serial D | ata/A                                   |

| Data Bit    | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | ]                 |                                         |

| 0           | RST | CSE | 0   | 0   | 0   | 0   | 0   | 0   | Read/Write        | Control Register 1                      |

| 1           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Reserved          |                                         |

| 2           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Reserved          |                                         |

| 3           | 0   | 0   | 0   | 0   | F3  | F2  | F1  | F0  | Read Only         | Fault Status Register                   |

| 4           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | RBD | Read/Write        | Control Register 2                      |

| 5           | FD  | US2 | US1 | US0 | OS3 | OS2 | OS1 | OS0 | Read/Write        | Over/Under-Scale Register               |

| 6           | 0   | 0   | 0   | 0   | 0   | G2  | G1  | G0  | Read/Write        | PGA Gain                                |

| 7           | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 | Read/Write        | Alarm Config. Register                  |

| 8           | 0   | VP2 | VP1 | VP0 | 0   | VN2 | VN1 | VN0 | Read/Write        | PGA Input Config. Register              |

| 9           | 0   | IB2 | IB1 | IB0 | 0   | IA2 | IA1 | IA0 | Read/Write        | IREF Output Config. Register            |

| 10          | FG7 | FG6 | FG5 | FG4 | FG3 | FG2 | FG1 | FG0 | Read/Write        | Fine I <sub>REF</sub> Adjust Register   |

| 11          | CG7 | CG6 | CG5 | CG4 | CG3 | CG2 | CG1 | CG0 | Read/Write        | Coarse I <sub>REF</sub> Adjust Register |

| 12          | FZ7 | FZ6 | FZ5 | FZ4 | FZ3 | FZ2 | FZ1 | FZ0 | Read/Write        | Fine Zero Adjust Register               |

| 13          | CZ7 | CZ6 | CZ5 | CZ4 | CZ3 | CZ2 | CZ1 | CZ0 | Read/Write        | Coarse Zero Adjust Register             |

| 14          | L7  | L6  | L5  | L4  | L3  | L2  | L1  | LO  | Read/Write        | Linearization Adjust Register           |

| 15          | S7  | S6  | S5  | S4  | S3  | S2  | S1  | S0  | Read/Write        | Checksum Register                       |

TABLE V. Analog Control Registers.

#### Address = 4: Control Register 2

If the RBD bit is set to '1', the automatic read-back from the EEPROM will be disabled after a valid checksum byte is received in Register 15. This bit is read from the EEPROM during a read-back by the XTR108 and allows the user to program the XTR108 to read the EEPROM data once (instead of continuously), and then disables the automatic read-back function. The XTR108 will continuously read the EEPROM if RBD is set to '0'. The remaining bits in this register must be set to '0'.

#### Address = 5: Over- and Under-Scale Register

This register sets the magnitude of the over-scale current limit and the magnitude of the under-scale current limit. The threshold level, as shown in Table VII and VIII, is the normal analog (no error condition) output limit. If an input voltage to the PGA exceeds the linear operation range, the output will be programmed to either the over-scale error level or the under-scale error level. The over-scale error level is 10mA greater than the over-scale threshold level. The under-scale error level is 0.4mA less than the underscale threshold level. The FD bit will disable the over-scale and under-scale limiting function as well as the PGA fault indication error levels.

#### Address = 6: PGA Gain Register

This register sets the gain of the programmable-gain amplifier. The unused bits must always be set to '0'. The gain step to register content is given in Table IX.

#### Address = 7: Alarm Configuration Register

This register configures whether the XTR108 will go overscale or under-scale for various detected fault conditions at the input of the PGA. Table X defines each of the bits.

If a bit corresponding to the particular error is set to '1', the output will go over-scale when it occurs and if a bit corresponding to the particular error is set to '0', the output will go under-scale.

| OS3 | OS2 | OS1 | OS0 | V <sub>o</sub> OVER-SCALE<br>THRESHOLD | I <sub>O</sub> OVER-SCALE<br>THRESHOLD<br>R <sub>VI</sub> = 6.34kΩ |

|-----|-----|-----|-----|----------------------------------------|--------------------------------------------------------------------|

| 0   | 0   | 0   | 0   | 2.625V                                 | 20.7mA                                                             |

| 0   | 0   | 0   | 1   | 2.6875V                                | 21.2mA                                                             |

| 0   | 0   | 1   | 0   | 2.75V                                  | 21.7mA                                                             |

| 0   | 0   | 1   | 1   | 2.8125V                                | 22.2mA                                                             |

| 0   | 1   | 0   | 0   | 2.875V                                 | 22.7mA                                                             |

| 0   | 1   | 0   | 1   | 2.9375V                                | 23.2mA                                                             |

| 0   | 1   | 1   | 0   | 3.0V                                   | 23.7mA                                                             |

| 0   | 1   | 1   | 1   | 3.0625V                                | 24.2mA                                                             |

| 1   | 0   | 0   | 0   | 3.125V                                 | 24.6mA                                                             |

| 1   | 0   | 0   | 1   | 3.1875V                                | 25.1mA                                                             |

| 1   | 0   | 1   | 0   | 3.25V                                  | 25.6mA                                                             |

| 1   | 0   | 1   | 1   | 3.3125V                                | 26.1mA                                                             |

| 1   | 1   | 0   | 0   | 3.375V                                 | 26.6mA                                                             |

| 1   | 1   | 0   | 1   | 3.4375V                                | 27.1mA                                                             |

| 1   | 1   | 1   | 0   | 3.5V                                   | 27.6mA                                                             |

| 1   | 1   | 1   | 1   | 3.5625V                                | 28.1mA                                                             |

| US2 | US1 | US0 | V <sub>o</sub> UNDER-SCALE<br>THRESHOLD | I <sub>O</sub> UNDER-SCALE<br>THRESHOLD<br>R <sub>VI</sub> = 6.34kΩ |

|-----|-----|-----|-----------------------------------------|---------------------------------------------------------------------|

| 0   | 0   | 0   | 450mV                                   | 3.55mA                                                              |

| 0   | 0   | 1   | 425mV                                   | 3.35mA                                                              |

| 0   | 1   | 0   | 400mV                                   | 3.15mA                                                              |

| 0   | 1   | 1   | 375mV                                   | 2.96mA                                                              |

| 1   | 0   | 0   | 350mV                                   | 2.76mA                                                              |

| 1   | 0   | 1   | 325mV                                   | 2.56mA                                                              |

| 1   | 1   | 0   | 300mV                                   | 2.37mA                                                              |

| 1   | 1   | 1   | 275mV                                   | 2.17mA                                                              |

|     |     |     |                                         |                                                                     |

TABLE VIII. Register 5, Under-Scale Threshold.

| G2 | G1 | G0 | PGA<br>VOLTAGE GAIN | SIGNAL PATH<br>TRANSCONDUCTANCE<br>$R_{VI} = 6.34k\Omega$ |

|----|----|----|---------------------|-----------------------------------------------------------|

| 0  | 0  | 0  | 6.25V/V             | 49mA/V                                                    |

| 0  | 0  | 1  | 12.5V/V             | 99mA/V                                                    |

| 0  | 1  | 0  | 25V/V               | 197mA/V                                                   |

| 0  | 1  | 1  | 50V/V               | 394mA/V                                                   |

| 1  | 0  | 0  | 100V/V              | 789mA/V                                                   |

| 1  | 0  | 1  | 200V/V              | 1577mA/V                                                  |

| 1  | 1  | 0  | 400V/V              | 3155mA/V                                                  |

| 1  | 1  | 1  | Reserved            |                                                           |

TABLE IX. Register 6, PGA Gains.

| BIT                                                                                                                                                | AC          | AC          | AC         | AC          | AC          | AC          | AC          | AC          |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------------|-------------|-------------|-------------|-------------|-------------|

| #<br>V <sub>INN</sub><br>V <sub>INP</sub>                                                                                                          | 7<br>h<br>l | 6<br>I<br>h | 5<br> <br> | 4<br>h<br>h | 3<br>n<br>I | 2<br>n<br>h | 1<br>I<br>n | 0<br>h<br>n |

| NOTES: 'h' = input exceeds positive common-mode range, 'l' = input exceeds negative common-mode range, and 'n' = input pin is within the CM range. |             |             |            |             |             |             |             |             |

TABLE X. Register 7, Alarm Configuration Register.

#### Address = 8: PGA Input Configuration Register

This register connects the inputs of the PGA to the various multiplexed input pins. Tables XI and XII show the relationship between register, contents, and PGA inputs.

| VP2 | VP1 | VP0 | PGA POSITIVE INPUT                      |

|-----|-----|-----|-----------------------------------------|

| 0   | 0   | 0   | PGA V <sub>IN+</sub> Connected to V/I-0 |

| 0   | 0   | 1   | PGA V <sub>IN+</sub> Connected to V/I-1 |

| 0   | 1   | 0   | PGA V <sub>IN+</sub> Connected to V/I-2 |

| 0   | 1   | 1   | PGA V <sub>IN+</sub> Connected to V/I-3 |

| 1   | 0   | 0   | PGA V <sub>IN+</sub> Connected to V/I-4 |

| 1   | 0   | 1   | PGA V <sub>IN+</sub> Connected to V/I-5 |

| 1   | 1   | 0   | Reserved                                |

| 1   | 1   | 1   | Reserved                                |

| VN2 | VN1 | VN0 | PGA NEGATIVE INPUT                       |

|-----|-----|-----|------------------------------------------|

| 0   | 0   | 0   | PGA V <sub>IN</sub> _ Connected to V/I-0 |

| 0   | 0   | 1   | PGA V <sub>IN</sub> Connected to V/I-1   |

| 0   | 1   | 0   | PGA V <sub>IN</sub> Connected to V/I-2   |

| 0   | 1   | 1   | PGA V <sub>IN</sub> Connected to V/I-3   |

| 1   | 0   | 0   | PGA V <sub>IN</sub> Connected to V/I-4   |

| 1   | 0   | 1   | PGA V <sub>IN</sub> Connected to V/I-5   |

| 1   | 1   | 0   | Reserved                                 |

| 1   | 1   | 1   | Reserved                                 |

TABLE XII. Register 8, PGA Negative Input Selection.

#### Address = 9: I<sub>REF</sub> Output Configuration Register

This register connects the reference currents to the various multiplexed input pins.  $I_{\rm REF}$  connection codes are given in Table XIII.

#### Address = 10: Fine I<sub>REF</sub> Adjust Register

This register sets the code to the 8-bit Fine DAC that adjusts the magnitude of both reference currents. The DAC output value has a bipolar range (for each reference current) and can be calculated using the equations in Table III.

| IA2              | IA1                   | IA0              |                                                                                                                                                                                                           |

|------------------|-----------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                | 0                     | 0                | IREF1 Connected to V/I-0                                                                                                                                                                                  |

| 0                | 0                     | 1                | IREF1 Connected to V/I-1                                                                                                                                                                                  |

| 0                | 1                     | 0                | IREF1 Connected to V/I-2                                                                                                                                                                                  |

| 0                | 1                     | 1                | IREF1 Connected to V/I-3                                                                                                                                                                                  |

| 1                | 0                     | 0                | I <sub>REF</sub> 1 Connected to V/I-4                                                                                                                                                                     |

| 1                | 0                     | 1                | I <sub>REF</sub> 1 Connected to V/I-5                                                                                                                                                                     |

| 1                | 1                     | 0                | Reserved                                                                                                                                                                                                  |

| 1                | 1                     | 1                | Reserved                                                                                                                                                                                                  |

| IB2              | IB1                   | IB0              |                                                                                                                                                                                                           |

| 1                |                       | IBU              | REF CONNECTION                                                                                                                                                                                            |

| 0                | 0                     | 0                | I <sub>RFF</sub> 2 Connected to V/I-0                                                                                                                                                                     |

| 0<br>0           |                       |                  |                                                                                                                                                                                                           |

|                  | 0                     | 0                | I <sub>REF</sub> 2 Connected to V/I-0                                                                                                                                                                     |

| 0                | 0                     | 0                | I <sub>REF</sub> 2 Connected to V/I-0<br>I <sub>REF</sub> 2 Connected to V/I-1                                                                                                                            |

| 0                | 0<br>0<br>1           | 0<br>1<br>0      | I <sub>REF</sub> 2 Connected to V/I-0<br>I <sub>REF</sub> 2 Connected to V/I-1<br>I <sub>REF</sub> 2 Connected to V/I-2                                                                                   |

| 0<br>0<br>0      | 0<br>0<br>1<br>1      | 0<br>1<br>0<br>1 | I <sub>REF</sub> 2 Connected to V/I-0<br>I <sub>REF</sub> 2 Connected to V/I-1<br>I <sub>REF</sub> 2 Connected to V/I-2<br>I <sub>REF</sub> 2 Connected to V/I-3                                          |

| 0<br>0<br>0<br>1 | 0<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1 | I <sub>REF</sub> 2 Connected to V/I-0<br>I <sub>REF</sub> 2 Connected to V/I-1<br>I <sub>REF</sub> 2 Connected to V/I-2<br>I <sub>REF</sub> 2 Connected to V/I-3<br>I <sub>REF</sub> 2 Connected to V/I-3 |

TABLE XIII. Register 9, I<sub>REF</sub> Output Configuration.

#### Address = 11: Coarse I<sub>REF</sub> Adjust Register

This register sets the code to the 8-bit coarse DAC that adjusts the magnitude of both reference currents. The nominal value for the reference current (both Coarse and Fine adjust set to '0') is  $I_{PROGRAM} \bullet 5$ . See Table III for formulas.

#### Address = 12: Fine Zero-Adjust Register

This register sets the code to the 8-bit Fine DAC that adjusts the magnitude of the zero output currents. Equations are given in Table II. Negative numbers are in Binary Two's Complement.

#### Address = 13: Coarse Zero-Adjust Register

This register sets the code to the 8-bit Coarse DAC that adjusts the magnitude of zero-output current. See Table II for equations. Negative numbers are given in Binary Two's Complement.

#### Address = 14: Linearization Adjust Register

This register sets the code to the 8-bit DAC that adjusts the magnitude of the linearization feedback current. Value is unipolar to 255.

#### Address = 15: Checksum Register

This register contains the checksum byte that is used to validate the data read from the EEPROM. If a write occurs to this register, and the checksum is invalid, an error condition will set (CSE = '1'). If the checksum is valid, the error condition will be cleared (CSE = '0').

If a checksum error is detected, the XTR108 will program itself to the lowest under-scale error level.

### SERIAL INTERFACE

#### PROTOCOL

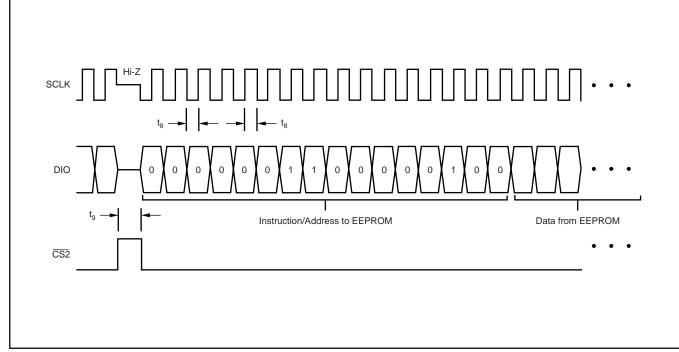

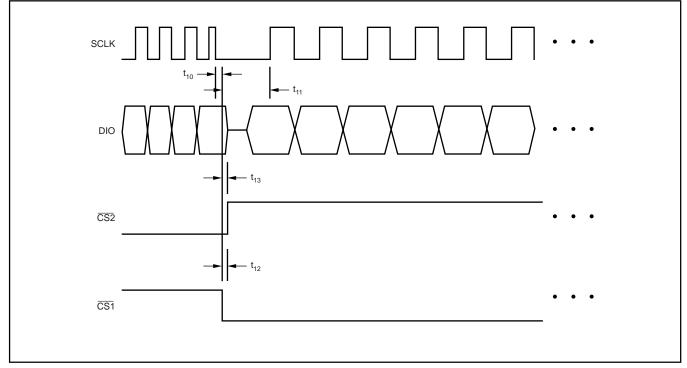

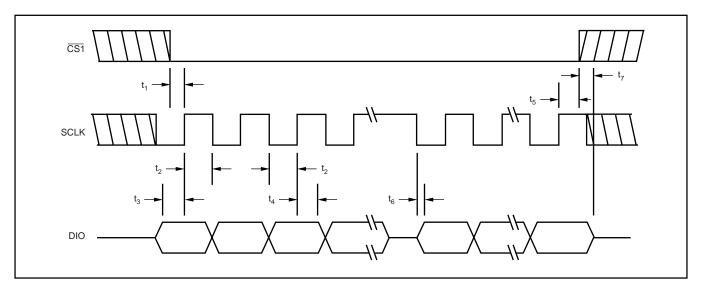

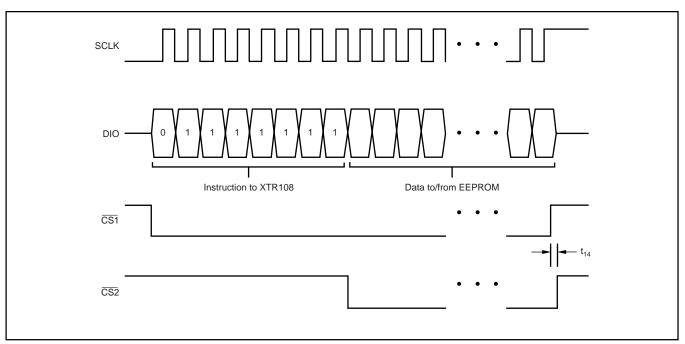

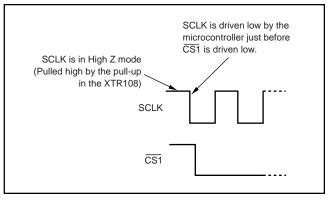

The XTR108 has an SPI-compatible serial interface. The data is transmitted MSB first in 8-bit bytes. The first byte is an instruction byte in which the first bit is a read/write flag ('0' = write, '1' = read), the lowest four bits are the register address and the remaining three bits are set to zero. The second, and all successive bytes, are data. During a write operation, the successive data bytes are written to successive registers within the XTR108. The address is automatically incremented at the completion of each byte. The SDIO line is always an input during a write operation. During a read operation, the SDIO line becomes an output during the second and successive bytes. As in the case of a write operation, the address is automatically incremented at the completion of each byte. Each communication transaction is terminated when  $\overline{CS1}$  is de-asserted. The  $\overline{CS2}$  line remains de-asserted during read and write operations.